OSC-1无源晶振基础

引言:晶振全称为晶体振荡器,其作用在于产生原始的时钟频率,在电路中用作时间或频率的基准源,这个频率经过频率发生器的倍频或分频后就成了系统中各种不同的总线频率、时钟周期。

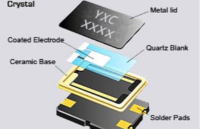

1.无源晶振的等效电路

如图1-1所示,石英晶体的压电谐振现象可以用等效电路来模拟,等效电路包括静态电容C0、动态电容C1、谐振电阻R1、以及动态电感L1,等效电路图如图:

图1-1:无源晶振等效模型

静态电容C0

静态电容C0是指晶体两引脚之间的电容,以水晶为介质,由两个金属电极形成的电容,和晶片电极面积(晶体体积)大小和频率大小呈正比。静电容C0太高会产生较大的副波,影响频率稳定性。在实际测数据中,C0值控制在2pF上下时,晶振的输出稳定性可以得到保障。

如果负载电容CL很大,静态电容C0的改变对频率变化的影响很小,频率更加稳定,所以负载高,远端相位噪声好;相反,如果负载电容CL很小,静电容C0的微小变化就会造成频率的明显变化,但近端相位噪声好,容易调整频率,晶振容易起振。

动态电容C1

动态电容C1表征振荡能力,与晶片电极面积(或晶体体积)和频率大小呈正比。

谐振电阻R1

谐振电阻R1表示晶体在固有谐振频率下的等效阻抗,与Q值成反比,而Q值是由生长的水晶料品质决定的。

朝着无源晶振越来越小型化,谐振电阻R1也会增大,负载电容CL会降低。

内阻RR和ESR

RR:晶振内阻/晶振电阻,是晶振本身的电阻值。RR越大,起振需要的功耗大,如果激励电平不变,内阻过大会造成起振困难。

ESR:表征能耗,与Q值成反比。Q值是由生长的水晶料品质决定的,Q值越高,固有频率则越稳定。

动态电感L1

动态电感L1表征振动质量,与频率大小成反比。

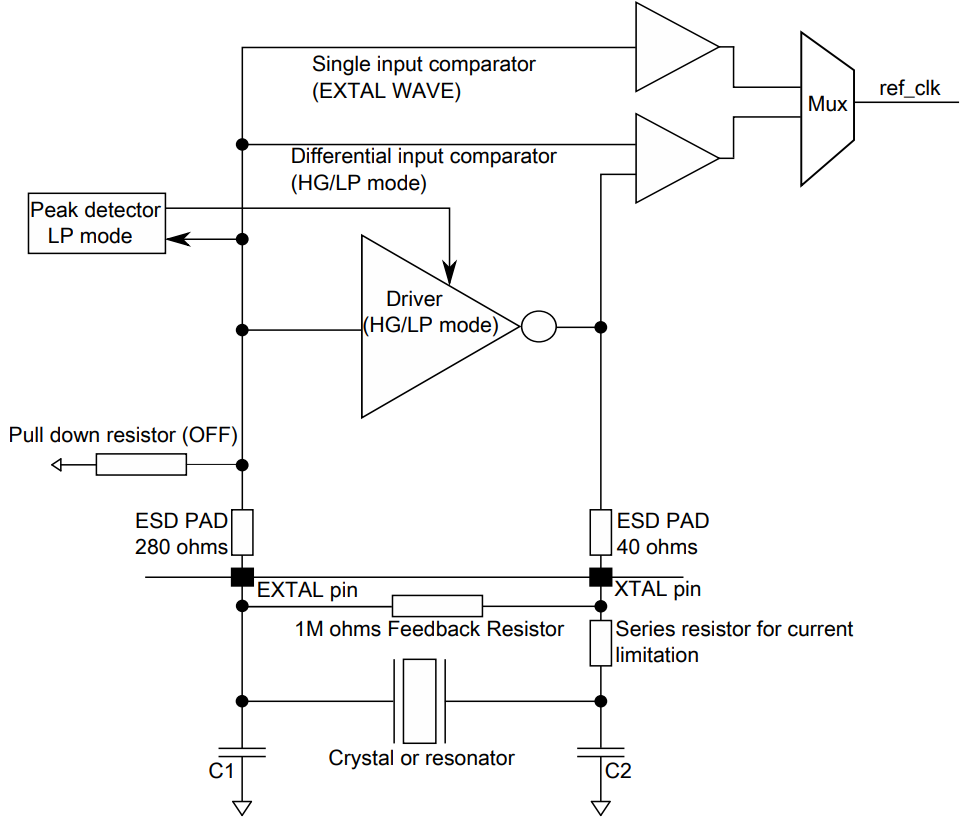

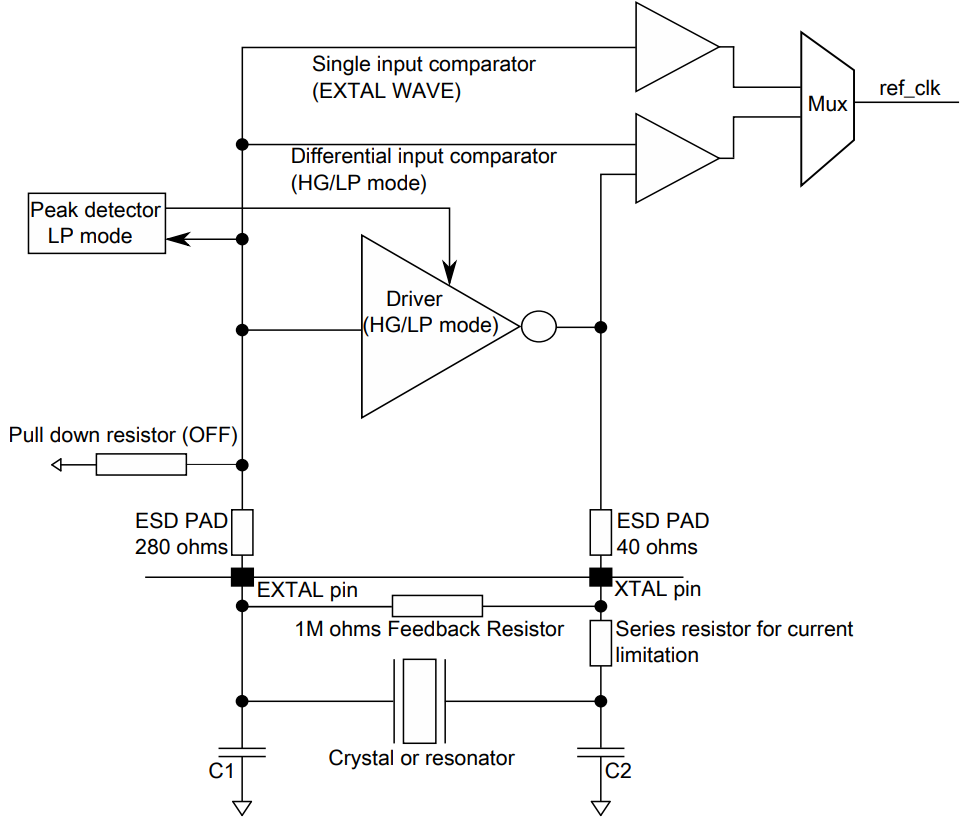

2.无源晶振的电路结构

无源晶振由于自身无法输出频率,需要搭配外部放大电路输出频率。在并联型振荡器电路中,皮尔斯电路是射极接地的并联振荡电路,工作有效且稳定。

如图1-2,皮尔斯振荡器Pierce Oscillator由晶振、芯片内部的反相放大器(Amp)、匹配电容C1和C2、以及电阻RF和Rd组成。

图1-2:无源晶振的典型结构

其中反相部分形成一个放大电路Amp,驱动电流从XTAL流出,经过晶体自身从EXTAL流入,因此C1也叫Cg,C2叫Gd。

负载电容CL

负载电容是设计晶体电路最为重要的参数之一,在串联谐振型电路中,不需要负载电容。晶体的频率会根据串联的电容电抗而改变,但在并联型谐振电路中必不可少。

CL的值大,远端相位噪声好,如果过大,则会难调整到标称频率,不易起振。CL的值小,近端相位噪声好,容易调整频率,容易起振。晶体时钟的负载电容(CL)建议为8pF ~ 20pF。

如果晶体两端的等效电容和标称负载电容存在差异,晶体输出的频率将会和标称工作频率产生偏差,叫做频偏。所以为了更接近晶体的负载电容CL,使晶体输出的频率则越精准,电路需要增加匹配电容CL1、CL2并考虑电路的杂散电容Cstray。电容器CL1和CL2靠近晶体XTI和XTO引脚,CL1和CL2可以由以下公式(公式1是通用公式,公式2是精确公式,建议使用公式2)来确定:

其中CL是总的负载电容,CL1和CL2是匹配电容,Cs(Cstray)包括XTI/XTO引脚和PCB的寄生电容,通常预估为3 ~ 8pF。

反馈电阻RF

反馈电阻RF有内置和外置两种,图1-2所示为外置,有的则是内置于主芯片中,此时晶振两端就不需要再加反馈电阻RF。

芯片Xin和Xout内部一般是施密特反相器,反相器不能驱动晶体振荡,需要并联一个电阻,即RF。电阻完成输出信号反向180度反馈到输入端进行负反馈,构成负反馈放大电路(Amp)。如果没有加RF,晶振电路也可能会起振,但存在不起振或者停振的风险,反馈电阻RF需要确保晶振启动并保持其稳定,通常RF推荐值为1MΩ-2MΩ。

小结:

1:配合IC内部形成负反馈

2:防止晶体被过分驱动

3:降低谐振阻抗,容易启动

4:电阻影响波形的脉宽

限流电阻Rd

外部限流电阻Rd作用是限制晶振电路的驱动大小,防止晶体被过分驱动,导致晶体老化或者早期失效,并且阻尼电阻Rd还可以用于抑制电磁干扰辐射。

Rd太小,晶振会承担太多功耗;Rd太大,电路起振条件不能满足,晶振无法正常工作。Rd的值不大,通常推荐值为0Ω-33Ω。根据主芯片的晶振波形幅度要求值,可以通过调整Rd的大小来调整晶振输出波形的振荡幅度。

小结:

1:降低激励功率防止损坏

2:限制振荡幅度。

-

放大器

+关注

关注

143文章

13583浏览量

213367 -

无源晶振

+关注

关注

1文章

831浏览量

15942 -

晶振

+关注

关注

34文章

2859浏览量

68004 -

等效电路

+关注

关注

6文章

292浏览量

32756

发布评论请先 登录

相关推荐

无源晶振的等效电路讲解 无源晶振的电路结构介绍

无源晶振的等效电路讲解 无源晶振的电路结构介绍

评论