FIFO,先进先出。在FPGA中使用的FIFO一般是指对数据的存储具有先进先出的缓冲器,FIFO与普通的存储器的不同在于它没有读写地址线。举个例子,当FPGA从外部传感器读取到一连串数据时,首先被写入FIFO中,然后FPGA再以UART串口通信依次将数据发送出去。因为传感器采集数据的速度很快,比如当传感器使用SPI通信协议,以2M的SPI数据速率读取时,串口使用9600的波特率肯定跟不上,因此需要先将从传感器处采集的数据使用FIFO缓存起来,然后再使用串口缓慢发送出去。

01 单时钟FIFO

单时钟FIFO具有一个独立的时钟端口,所有输入信号的读取都是在该时钟端口信号的上升沿进行的,所有输出信号的变化也是在该时钟信号的上升沿的控制下进行的,单时钟FIFO的所有输入输出信号基本都是和时钟信号同步。

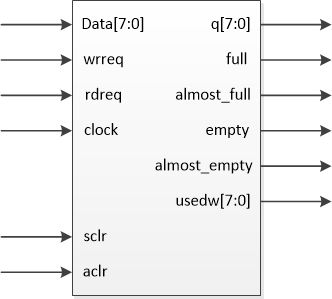

data为写入的数据,此处为8位。然后wrreq为请求写操作,rdreq为请求读操作,clock为时钟信号。q为输出端,8位数据的输出端。full为满标志,当fifo缓冲器存储数据溢满时,full端将输出高电平。almost_full为接近满标志信号,当存储的数据即将要满时,almost_full端将输出高电平以阻止写操作继续向fifo中写数据造成数据溢出。empty则为空标志位,当fifo中数据全部读取完后,empty端便会输出高电平用来标记,almost_empty便是在fifo即将要空时便会发出高电平,以阻止fifo的读操作继续从fifo中读取数据。usedw为fifo中的字数,sclr为异步清零端口。

02 IP核使用

首先创建一个FIFO的工程保持在prj下,并在prj下新建一个ip的文件夹。点击Tools -> MegaWizard Plug-In Manager。

选择创建一个新的,然后如下图,在左边搜索框输入FIFO,然后选择第一项,选择后在右边的路径中输入地址ip并以fifo.v保持。

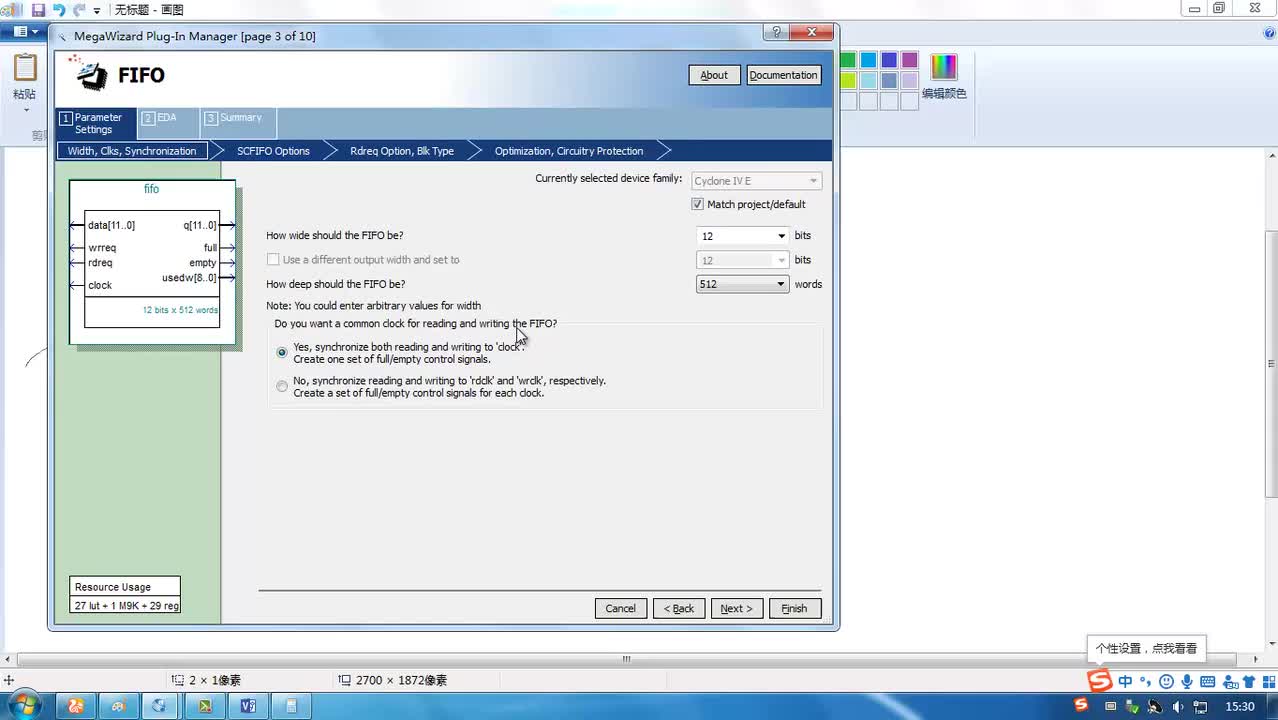

接下来如下图,首先设置数据的位宽及深度,此处设置数据位宽为8位,数据深度为256words(及多少个数据)。

然后接下来设置需要的端口,根据01中的结构图,这里需要选择full满、empty空、以及接近满almost_full、接近空almost_empty和异步清零端sclr。在接近满与接近空处需要设置阈值,即到达多少时接近满端口开始输出标志信号,这里设置数据写操作达到254words时接近满标志开始标记,数据读操作在usedw为2时接近空端口开始标记。

下图便是读操作请求确认信号的两种模式,一个是普通模式一个是前显模式。

选择器件优化方式是面积优先还是速度优先,更换可以看到资源占用率是不一样的,选择速度优先必然使用资源会上升。

然后便一直next后finish创建完成。

这时转回界面便可看到生成ip的fifo.v文件,然后便开始书写激励仿真文件。

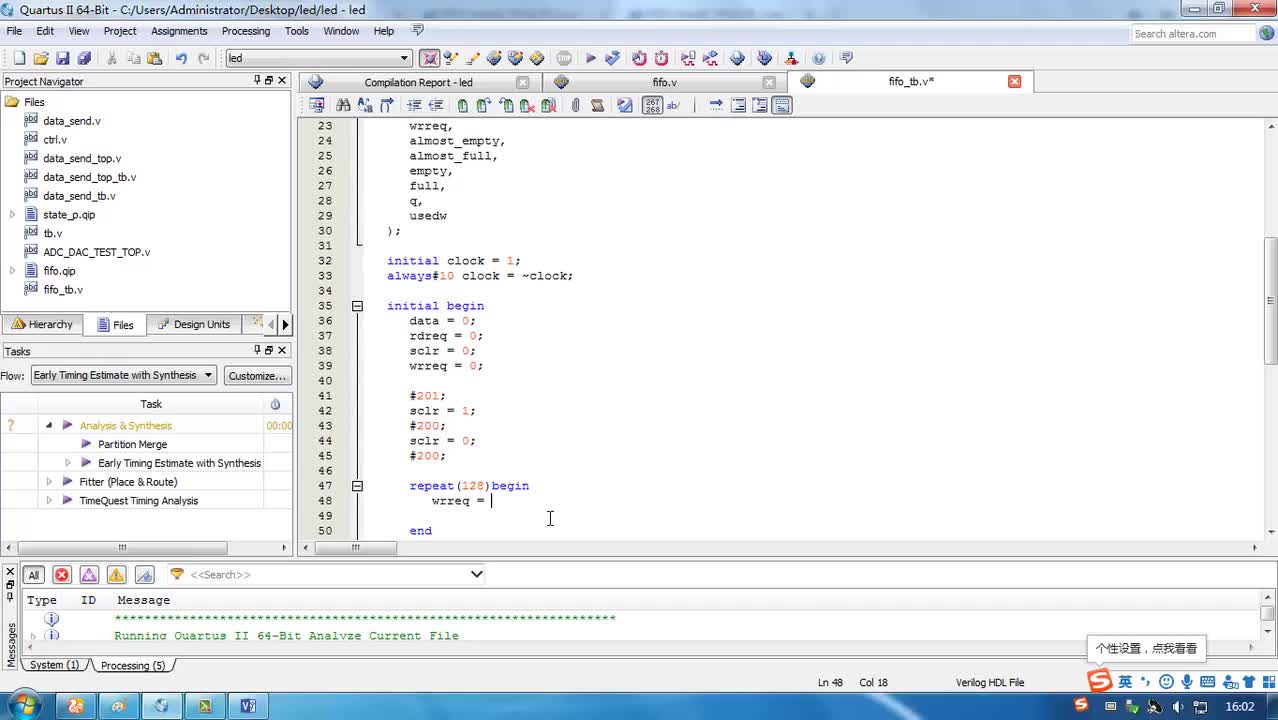

首先还是例化需要仿真的文件,然后仿真时钟并在仿真文件中与例化程序进行连线。

接下来便是定义常量i,写一个for循环,i自加写请求wrreq置1将i的值写入数据data中,usedw中数据深度开始依次增多,等256个words写完之后,写请求关闭,然后开始读操作,同样的i从零自加到255,然后将读请求置1开启,系统便开始从输出端q中依次输出data中的数据,同时usedw中的数据深度也开始一次减少。

接下来看仿真波形图:

此处是综合仿真图,前半部分是写操作的波形图,后半部分便是读操作的波形图。

上图这部分为写操作,图中可以看到i每个周期自加1,i的值便赋给数据data,然后usedw便是统计此时data中的数据多少即深度,在usedw为2时可以看到almost_empty接近空出现一个下降沿,在data中开始写入数据时,写请求wrreq产生高电平。

此处可以看出,在深度usedw自加至254时,接近满端almost_full便会产生上升沿用来标记,计满后full端产生上升沿,写操作结束。

上图为读操作,这里随着i的自加输出端q开始依次输出data中的数据,然后usedw随着data中的数据被读取便开始自减。

后面可以看出,当深度usedw为2时,接近空端almost_empty产生上升沿,清空后empty也产生上升沿,读操作结束。

-

传感器

+关注

关注

2551文章

51134浏览量

753830 -

fifo

+关注

关注

3文章

388浏览量

43691 -

时钟

+关注

关注

11文章

1734浏览量

131508 -

uart

+关注

关注

22文章

1237浏览量

101420 -

IP核

+关注

关注

4文章

327浏览量

49506

发布评论请先 登录

相关推荐

【锆石A4 FPGA试用体验】IP核之FIFO(一)创建与配置

XILINX FIFO IP核调用问题

以MIPI项目为例讲解Diamond FIFO生成和例化全过程

【正点原子FPGA连载】第十三章IP核之FIFO实验-领航者ZYNQ之FPGA开发指南

FIFO IP核的使用

基于MicroBlaze的AXI总线实时时钟IP核设计

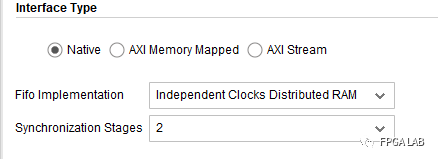

AXI STREAM FIFO如何设置双时钟

讲解几点关于FIFO IP核使用时的注意事项

XILINX FPGA IP之FIFO Generator例化仿真

使用IP核创建单时钟FIFO

使用IP核创建单时钟FIFO

评论