1总线的由来

很多人对总线和地址映射的概念都是一头雾水,但是我们如果知道为何需要总线和地址映射,他们是在什么背景下被衍化出来的,自然而然对此概念就清清楚楚了。

我们知道CPU都是通过总线访问外设,例如STM32使用AMBA规范的总线和外设进行交互,那么在总线的概念没有被提出来的时候,外设是怎样被访问的呢?

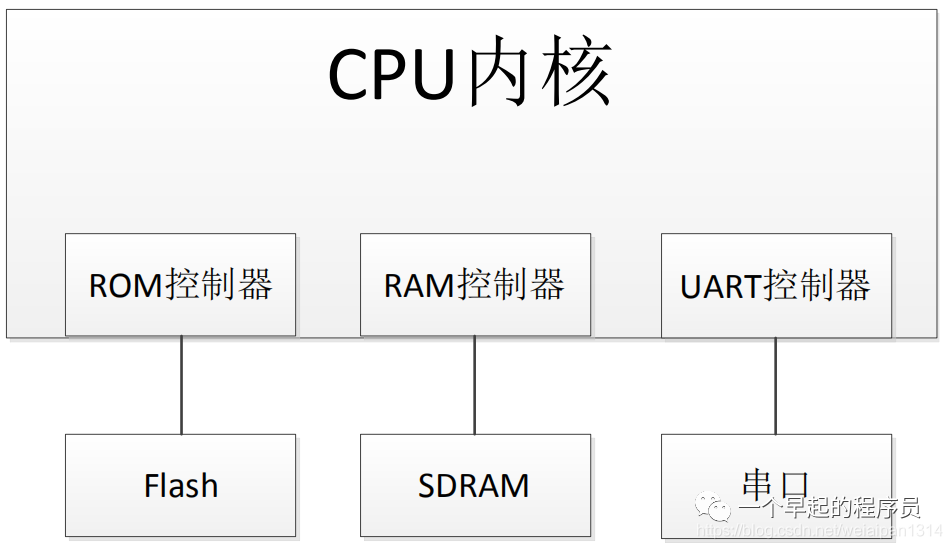

其实在最早期还没有总线概念的时候,CPU设计者会直接把CPU内核和各种接口控制器设计到一起,如果要访问一个硬件,直接在内核里面对各种接口控制器进行操作,从而操作相应的硬件。我们看下图。

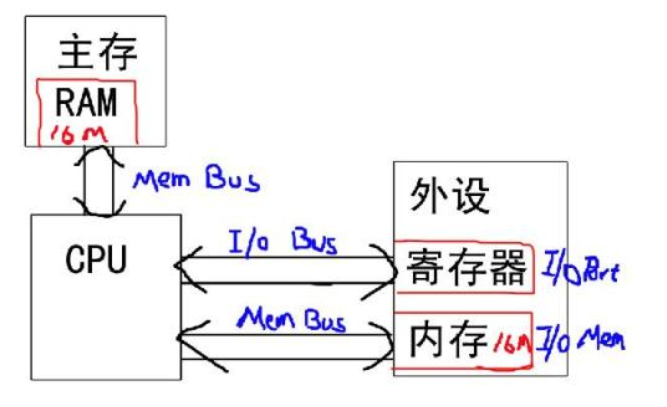

后来设计者发现如果每添加一个外设都要修改CPU内核,这样不具有很好的扩展性,为了使得外设的改变(增加、删除、修改)不影响CPU内核架构,衍化出了总线的概念,CPU内核可以通过总线访问各种各样外设,新的外设只需要挂接到总线上,就可被CPU内核访问控制。有了总线,CPU可以用统一的访问方式访问任何外设,实现了CPU内核和外设分开设计和维护。

如下图所示,下图和CPU内核交互的只有地址总线接口、数据总线接口、控制总线接口,这三个接口一个提供地址、一个提供数据,一个提供控制信息(读、写、其他控制信息),所有的外设连接到总线矩阵上。

2 STM32/CPU地址映射

外设怎么知道CPU内核发出的操作是给自己的呢?

其实每一个外设都具有自己的地址空间,当CPU内核通过总线访问外设时,对应地址空间的外设就知道CPU内核是在操作自己(外设被命中),然后外设去操作连接的硬件,如上图ROM控制器操作Flash设备。

外设的地址控制怎么分配呢?

答案就是地址映射,地址映射这个过程是在设计芯片的时候就要进行考虑的,地址总线接口如果是32位,则内核可访问的外设空间最大就是4Gbit,芯片设计者为每一个外设会映射一段地址空间,比如GPIOA映射到0x0000000-0x0000FFFF,则CPU在访问0x0000000-0x0000FFFF地址空间时会被GPIOA外设捕获到,至于外设想做什么由外设的硬件设计者来决定。地址总线接口如果是64位,则内核可访问外设的地址空间为2^64bit。

3 STM32的外设地址映射表

STM32地址总线接口为32位,则可以访问4Gbit的外设空间,下面为STM32F10X外设地址映射表。有很多还没有被映射的地址空间,ST公司后期可能用来扩展新外设,而扩展过程Cortex内核是不需要进行任何修改的。

-

cpu

+关注

关注

68文章

11364浏览量

226319 -

STM32

+关注

关注

2313文章

11205浏览量

375144 -

总线

+关注

关注

10文章

3065浏览量

91951 -

地址映射

+关注

关注

0文章

6浏览量

2251

发布评论请先 登录

Linux内核地址映射模型与Linux内核高端内存详解

STM32外设地址映射有哪些?都是什么?

存储器映射与寄存器映射的原理分别是什么

STM32核心在Cortex的地址映射说明

STM32F103系列芯片的地址映射和寄存器映射原理,GPIO端口的初始化

STM32-寄存器地址名称映射分析

2020.4.14 第四次 寄存器地址名称映射

STM32 部分重映射和完全重映射

STM32/CPU地址映射的概念

STM32/CPU地址映射的概念

评论