1 DDS概念

DDS(Direct Digital Frequency Synthesizer) 直接数字频率合成器,本文主要介绍如何调用Xilinx的DDS IP核生成某一频率的Sin和Cos信号。

2 DDS IP使用

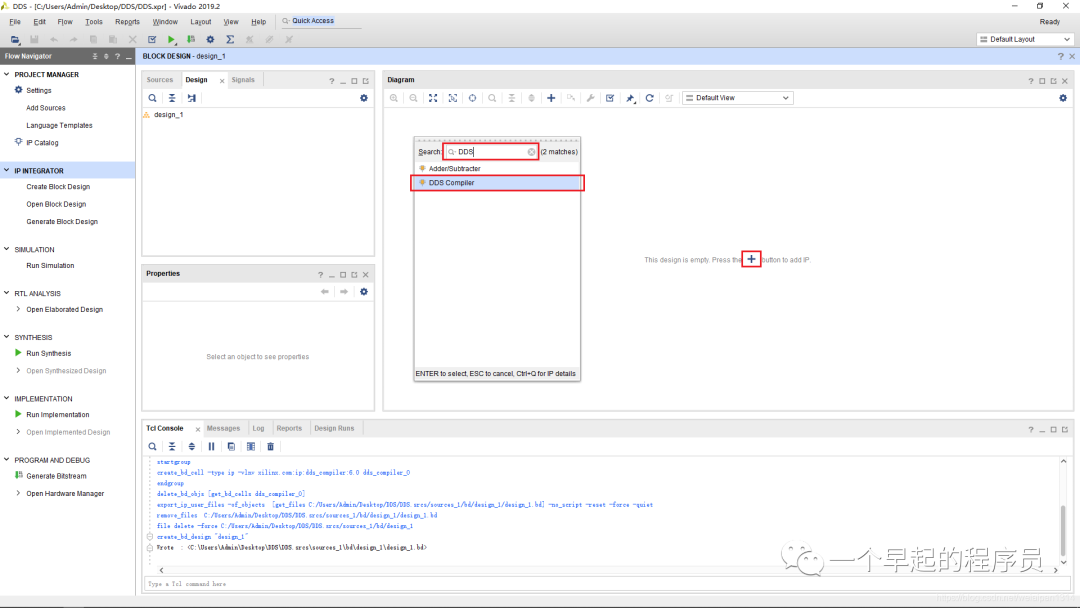

打开Vivado创建Block Design。

添加 DDS IP。

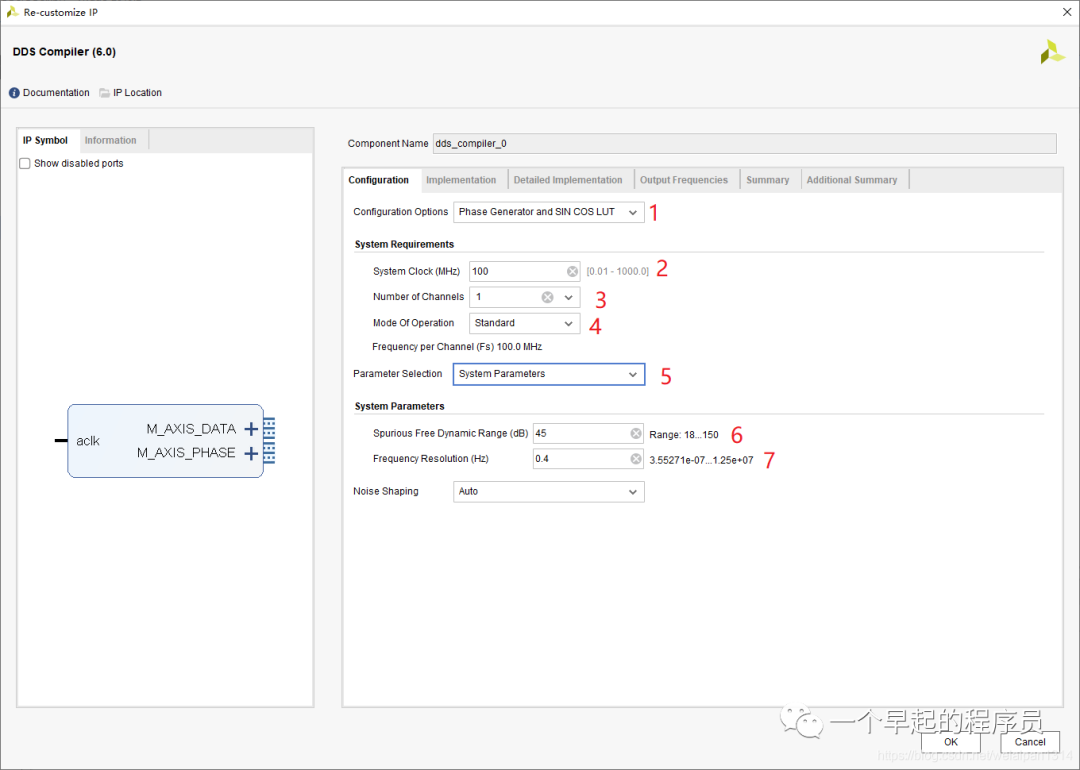

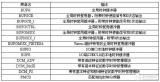

1、我们选择波形与相位同时存在的情况。

2、选择DDS IP输入的系统时钟频率,这里我们选择100MHz。

3、DDS通道的数目,我们这里选择一个。

4、整个IP配置的模式,我们这里选择标准模式即可。

5、参数选择的模式,我们这里选择系统参数,这个选择主要影响IP的定制界面所涉及到的参数。

6、频率的动态范围,主要和DDS内部RAM的数据位宽有关,计算方法是20log2n,其中n为RAM的位宽。

7、选择DDS的最小的频率分辨率。

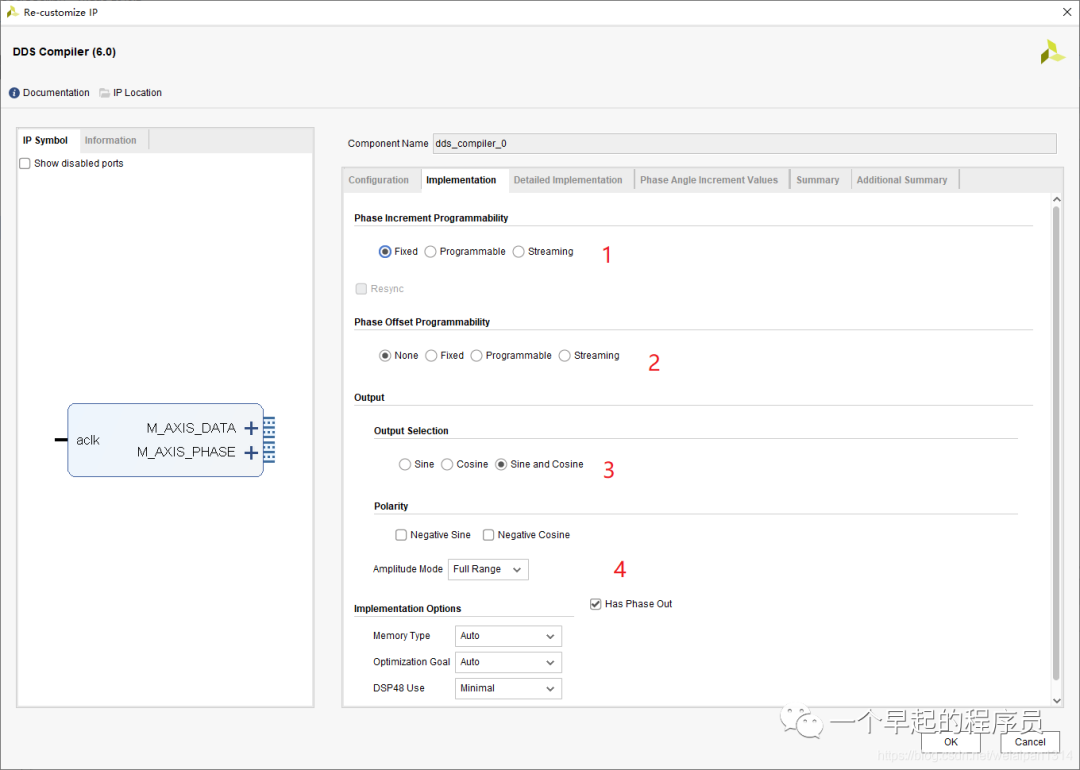

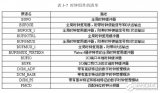

1、相位增量我们选择固定。

2、相位偏执我们也选择成固定,这两个参数可以动态控制输出的频率。

3、我们这里产生正弦波和余弦波。

4、因为我们只考虑正弦波的频率,所以这里不再输出相位信息。

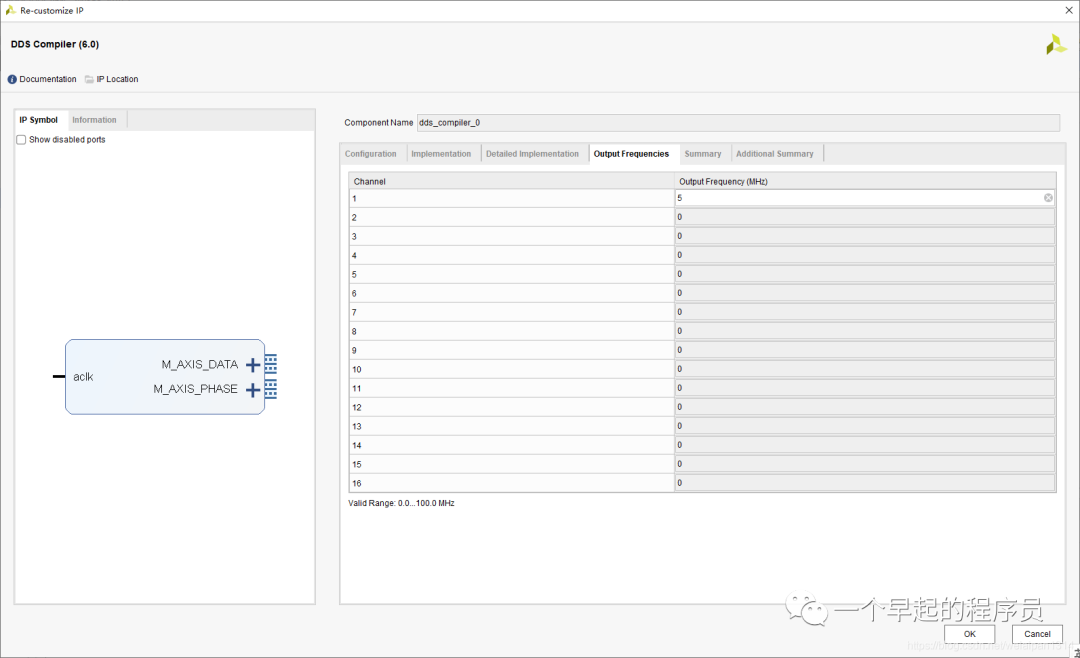

输入我们需要DDS输出的频率,这里我们输入5MHz,其余选项,我们选择默认即可。点击确定。

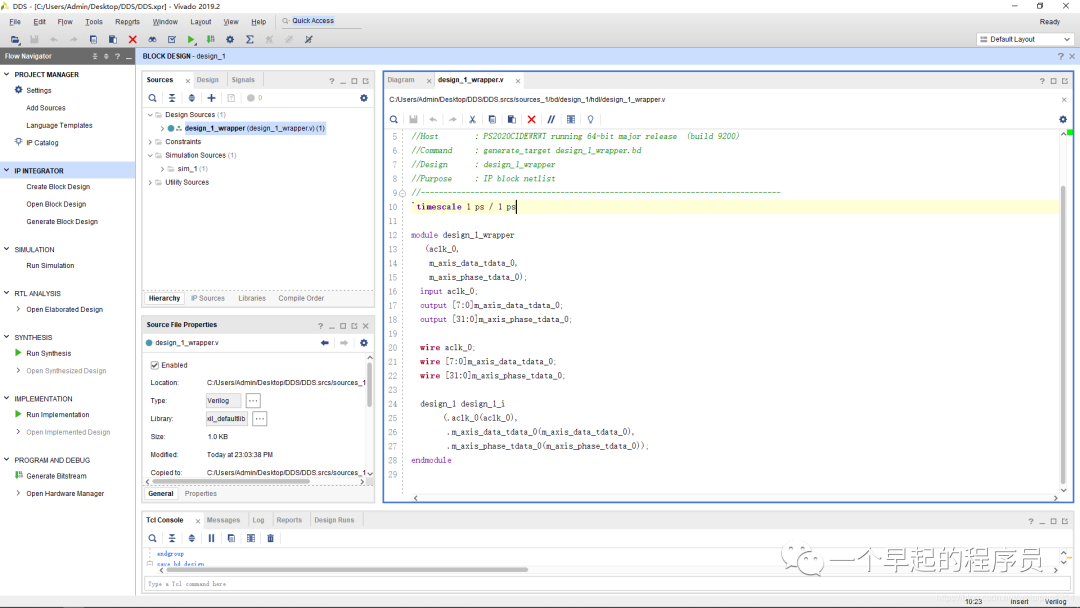

生成顶层文件。

添加仿真文件。

3 Testbench编写

`timescale 1ns / 1ps

//

// Company:

// Engineer: 一个早起的程序员

//

// Create Date: 2020/12/01 23:08:37

// Design Name:

// Module Name: sim

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module sim(

);

wire [7:0] m_axis_data_tdata_0 ;

wire [31:0] m_axis_phase_tdata_0 ;

reg aclk ;

initial begin

aclk = 1'b0;

end

always #5 aclk = ~aclk;

design_1_wrapper design_1_wrapper_u0(

.aclk_0 (aclk ),

.m_axis_data_tdata_0 (m_axis_data_tdata_0 ),

.m_axis_phase_tdata_0 (m_axis_phase_tdata_0 )

);

endmodule

4 波形分析

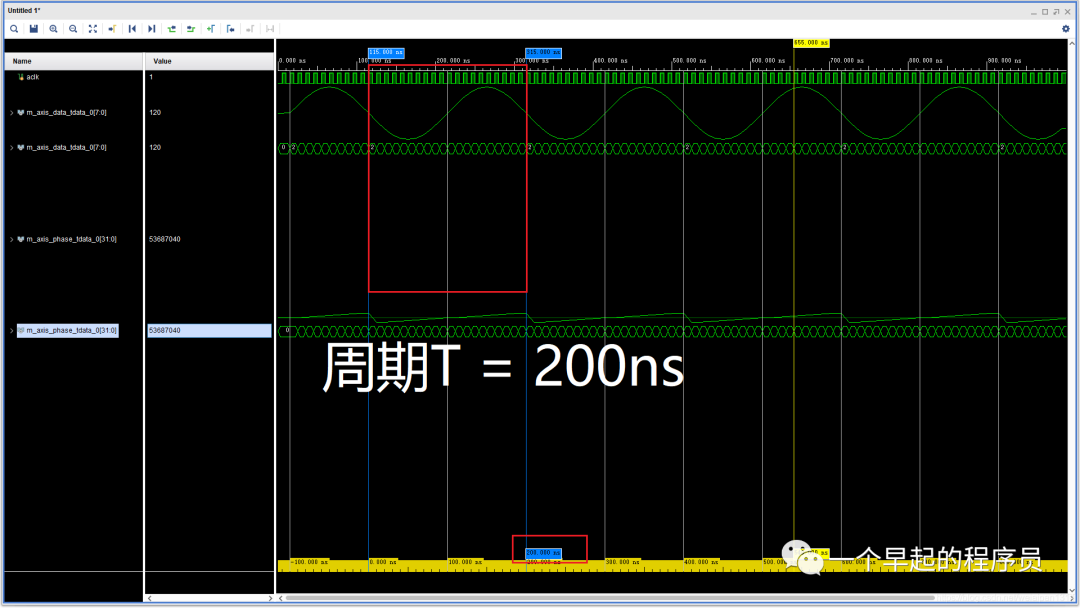

1.核心的核心:5M的波形周期则为200ns,因为时钟只有100M,所以一个周期只能输出20个点。

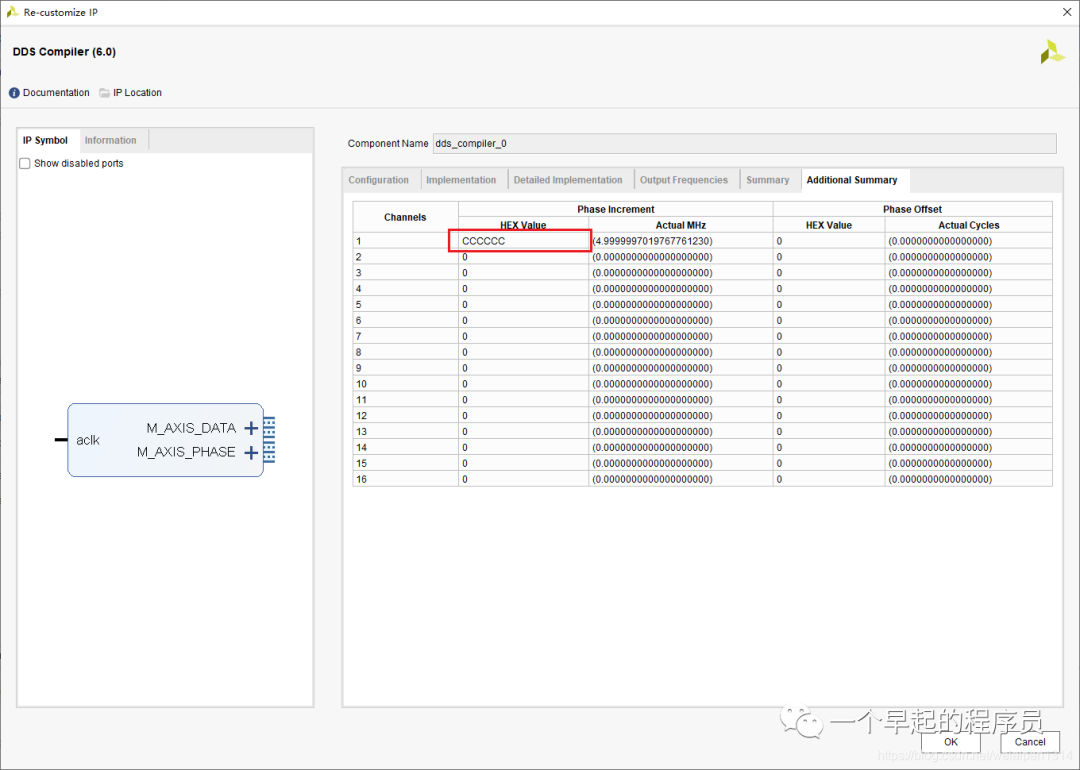

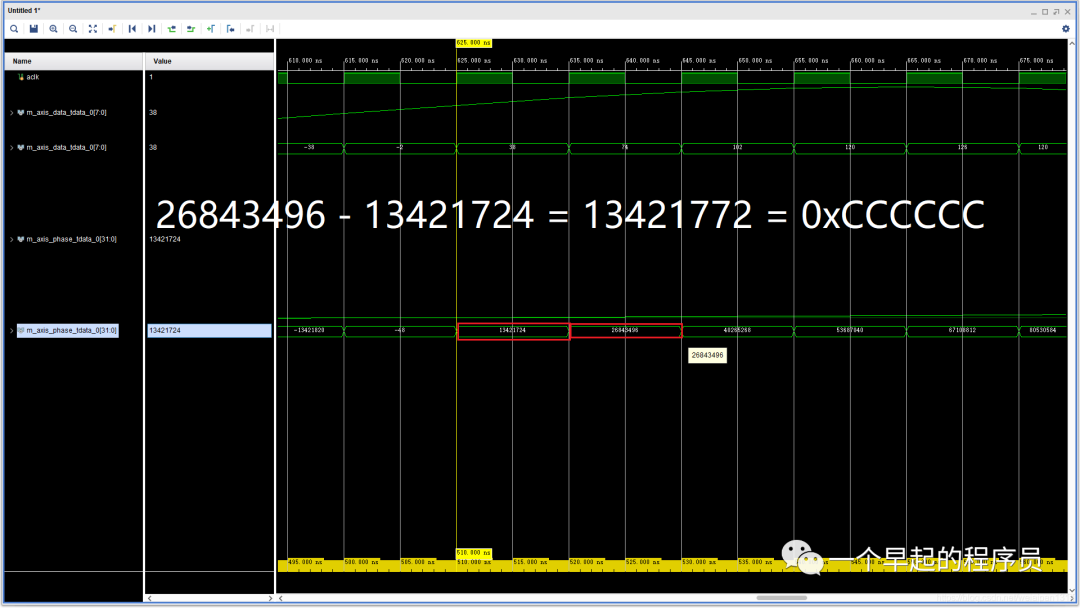

2.核心的核心:设置界面Summary显示Phase Increment值为0xCCCCCC,从波形上也可以看出,两个点角度差0xCCCCCC。

-

Xilinx

+关注

关注

71文章

2173浏览量

122715 -

时钟

+关注

关注

11文章

1756浏览量

132124 -

DDS

+关注

关注

21文章

639浏览量

153205 -

Vivado

+关注

关注

19文章

819浏览量

67191

发布评论请先 登录

相关推荐

使用VIVADO IDE设计的最有效方法是什么?

Gowin DDS IP用户指南

Xilinx Vivado的使用详细介绍(3):使用IP核

Vivado将模块封装为IP的方法介绍

解析Vivado如何调用DDS的IP进行仿真

关于Xilinx中DDS IP的运用与讲解

Xilinx-DCM的使用方法技巧

Xilinx Vivado DDS IP使用方法

Xilinx Vivado DDS IP使用方法

评论