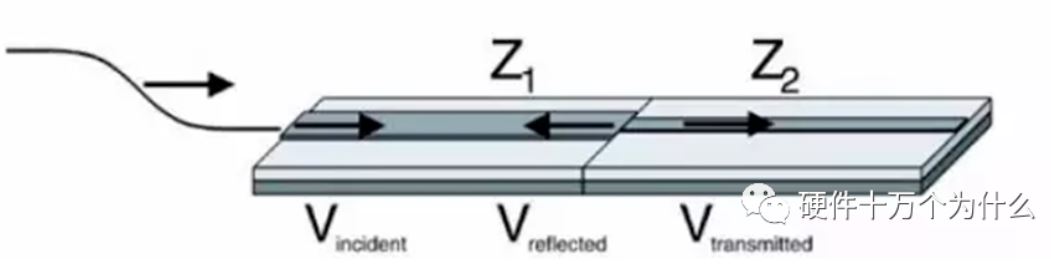

由于电信号在PCB上传输,我们在PCB设计中,可以把PCB走线认为是信号的通道。当这个通道的深度和宽度发生变化时,特别是一些突变时,都会产生反射。此时,一部分信号继续传播,一部分信号就可能反射。而我们在设计的过程中,一般都是控制PCB的宽度。所以,我们可以把信号走在PCB走线上,假想为河水流淌在河道里面。当河道的宽度发生突变时,河水遇到阻力自然会发生反射、旋涡等现象。

同样的,信号在PCB上走线当遇到PCB的阻抗突变了,信号也会发生反射。

我们以光的反射类比信号的反射。光的反射,指光在传播到不同物质时,在分界面上改变传播方向,返回原来物质中的现象。光在碰到介质界面时,其折射率和反射率由。光线在临界面上的反射率仅与介质的物理性能,光线的波长,以及入射角相关。

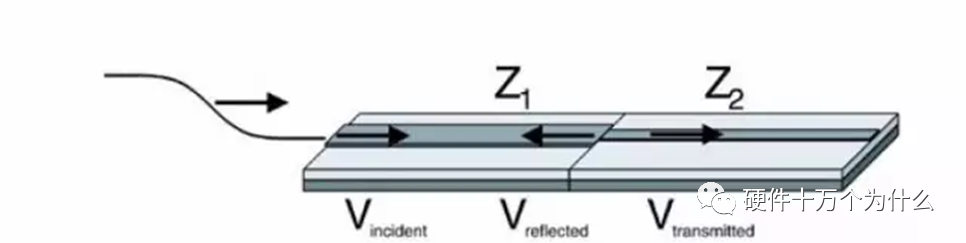

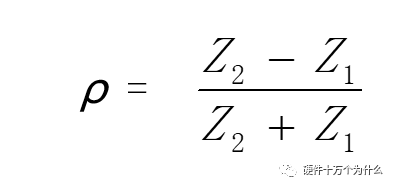

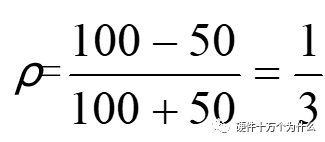

同样的,信号/电磁波在传输过程中,一旦传输线瞬时阻抗发生变化,那么就将发生反射。信号的反射有一个参数叫作反射系数(ρ),计算公式如下:

式中,Z1为变化前的阻抗;Z2为变化后的阻抗。假设PCB线条的特性阻抗为50Ω,传输过程中遇到一个理想的100Ω的贴片电阻接地,那么反射系数运用公式计算得到:

信号有1/3被反射回源端。反射系数ρ计算公式的推导过程,此处不展开。

信号沿传输线向前传播时,每时每刻都会可能发生阻抗变化,如PCB走线宽度变化、PCB厚度变化、换层、电阻、电容、电感、过孔、PCB转角、接插件、器件管脚;这个阻抗可能是传输线本身的,也可能是中途或末端其他元件的。对于信号来说,它不会区分到底是什么,信号是否反射,只会根据阻抗而变化。如果阻抗是恒定的,那么他就会正常向前传播,只要阻抗发生了变化,不论是什么引起的,信号都会发生反射。

不管是COMS电路,还是SSTL电路,抑或是射频电路,电路设计工程师希望整个传输链路阻抗都是一致的,最理想的情况就是源端、传输线和负载端都一样。但实际总是事与愿违,因为发送端的芯片内阻通常会比较小,而传输线的阻抗又是50Ω,这就造成了不匹配,使信号发生反射。这种情况在并行总线和低速信号电路中常常出现,而通常对于高速SerDes电路而言,芯片内阻与差分传输线的阻抗是匹配的。

如果确实出现了阻抗不匹配,通常的做法是在芯片之外采用电阻端接匹配来实现阻抗一致性。常用的端接方式有源端端接、终端并联端接、戴维宁端接、RC 端接、差分端接等。那端接电阻要使用几颗?端接电阻怎么放置?阻值是选择多大呢?

1、点对点拓扑结构

在介绍端接之前,先了解下电路的拓扑结构。电路的拓扑是指电路中各个元件之间的连接关系。常见的电路拓扑结构包括点对点的拓扑、星型拓扑、T型拓扑、菊花链拓扑等,最简单的拓扑就是点对点拓扑结构的连接设计。点对点设计也是最常见的电路拓扑设计,尤其是在高速电路中几乎都是点对点的连接设计。

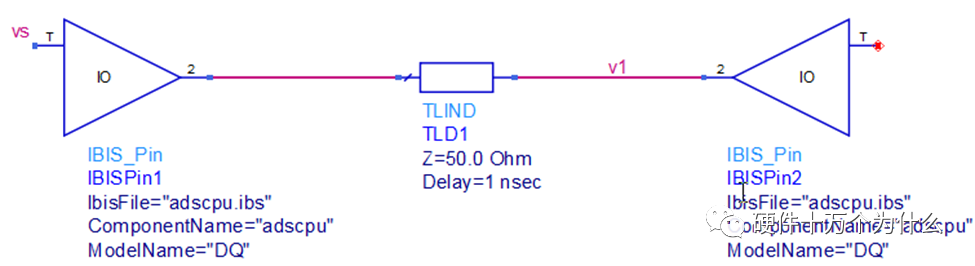

点对点虽然简单,但这种拓扑设计限制了带负载的数量。点对点设计,由于驱动端的内部阻抗与传输线的阻抗常常不匹配,很容易就会形成信号反射,使信号失真。这就是一个信号完整性问题。

如下图所示,是点对点的拓扑结构,由驱动端、传输线和接收端组成。

▲点对点无端接拓扑结构

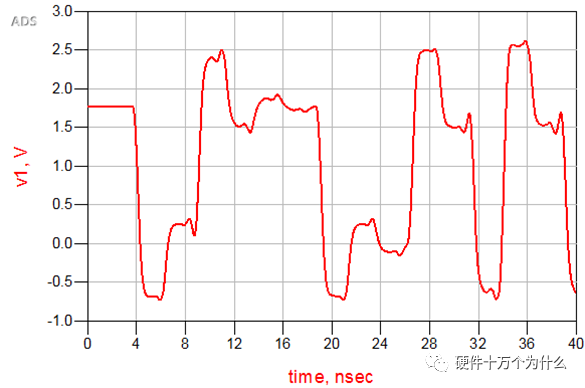

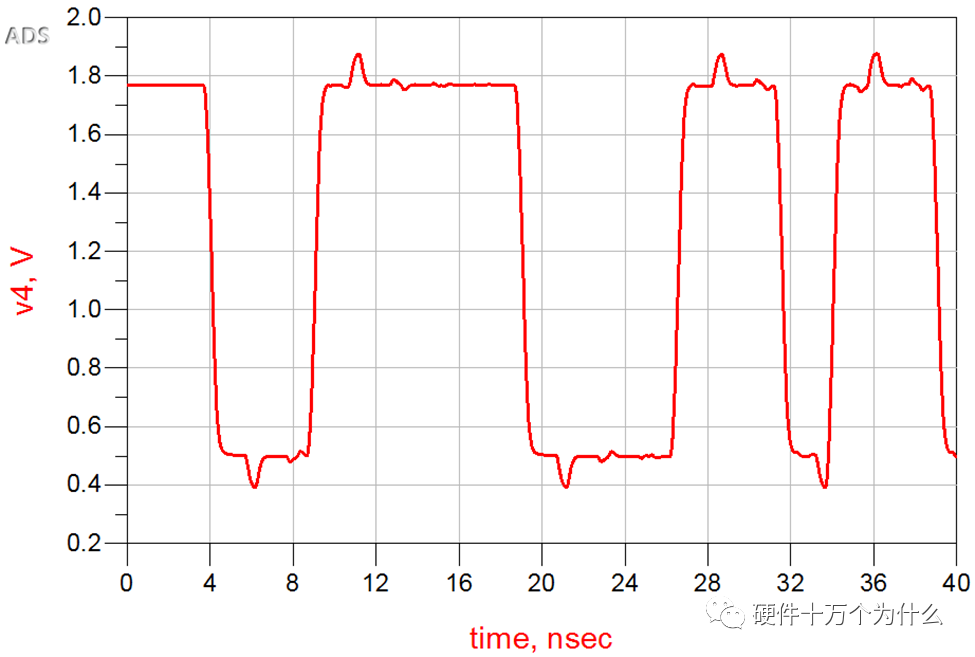

在这个电路拓扑中,其接收端的信号波形,如下图所示:

▲点对点无端接的信号波形

从波形上分析,信号在高电平时稳定电压在1.8V,但是最大值达到了2.619V,有819mV的过冲;最小值达到了-731mV,低于0V达到了731mV。这种情况在电路设计中需要尽量避免,因为这么大的过冲很容易损毁芯片,即使不损毁,也存在可靠性的问题。

所以,在设计中需要把过冲降低,尽量保证电压幅值在电路可接受的范围内,如此案例尽量保证满足1.8V+/-5%,这时就需要通过 端接电阻来改善信号质量。

2、源端端接

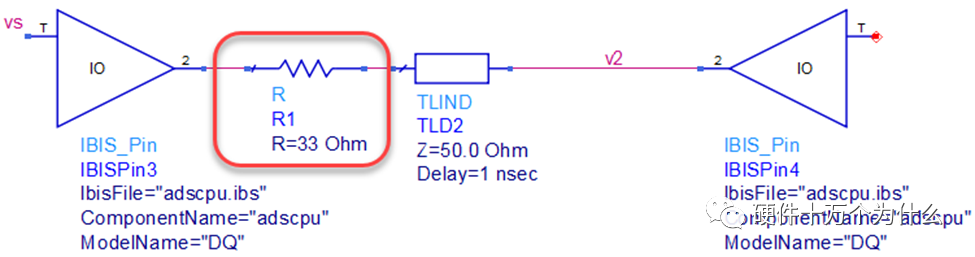

源端端接设计也叫串联端接设计,是一种常用的端接设计。端接方式是只在芯片端出来之后添加一颗端接电阻,尽量靠近输出端。在此电路结构中,关键的是加多大阻值的电阻,需要根据电路的实际情况进行仿真或计算确认。

计算的原则是源端阻抗Rs与所加端接电阻R0的值等于传输线的阻抗Z0。在前面的点对点拓扑结构中,加入端接电阻值为33Ω的R1,其电路拓扑结构,如下图所示。

▲源端端接拓扑结构

此时在接收端获得的信号波形,如下图所示:

▲源端端接后的波形

使用源端端接后,原本的存在的过冲已经基本消除,信号质量得到极大的改善。在加入源端端接电阻之后,信号的上升沿变缓,上升时间变长。

源端端接在电路匹配时,可以使电路匹配得非常好,但并不是适合于每一种电路设计。源端端接有自身的一些特性,大致归纳如下:

(1)源端端接非常简单,只需要使用一颗电阻即可完成端接。

(2)当驱动端器件的输出阻抗与传输线特性阻抗不匹配时,使用源端端接在开始就可以使阻抗匹配;当电路不受终端阻抗影响时,非常适合使用源端端接;如果接收端存在反射现象,就不适合使用源端端接。

(3)适用于单一负载设计时的端接。

(4)当电路信号频率比较高时,或者信号上升时间比较短(特别是高频时钟信号)时,不适合使用源端端接。因为加入端接电阻后,会使电路的上升时间变长。

(5)合适的源端端接可以减少电磁干扰(EMI)辐射。

3、并联端接

并联端接即把端接电阻并联在链路中,一般把端接电阻在靠近信号接收端的位置,并联端接分为上拉电阻并联端接和下拉电阻并联端接。电路图如下:

▲并联端接拓扑结构

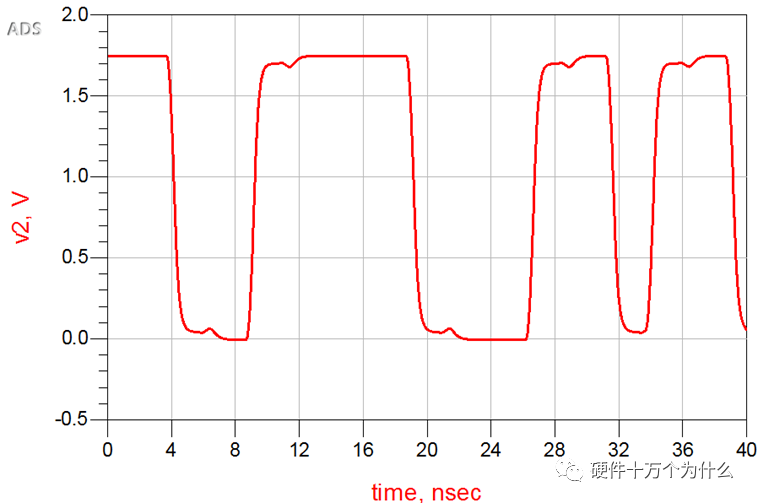

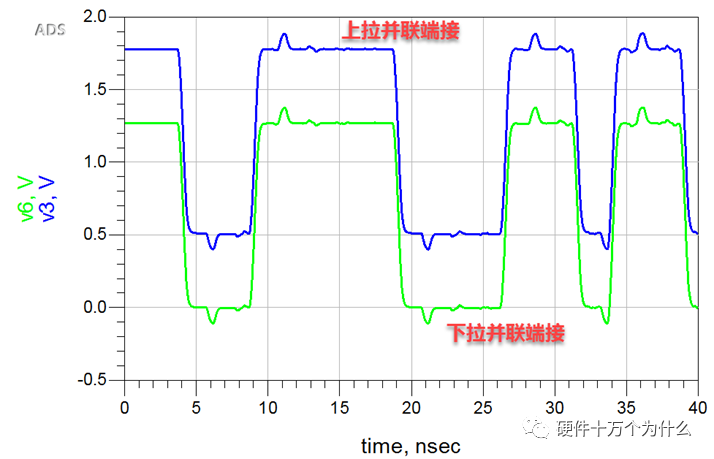

端接电阻值R0与传输线的阻抗一致。使用并联端接后,其接收端的信号波形,如下图所示:

▲并联端接后的信号波形

从波形上分析,过冲基本被消除。上拉并联端接的波形低电平有很明显的上移,下拉并联端接的波形高电平有很明显的下移。不管是上拉并联端接还是下拉并联端接,信号波形的峰峰值都比使用源端端接时要小一些。

并联端接放在接收端,所以能很好地消除反射,使用的元件也只有电阻。

从电路结构就可以看出,即使电路保持在静态情况,并联端接依然会消耗电流,所以驱动的电流需求比较大,很多时候驱动端无法满足并联端接的设计,在特别是多负载时,驱动端更加难以满足并联端接需要消耗的电流。所以,一般并联端接不用于TTL和COMS电路。同时,由于幅值被降低,所以噪声容限也被降低了。

4、戴维宁端接

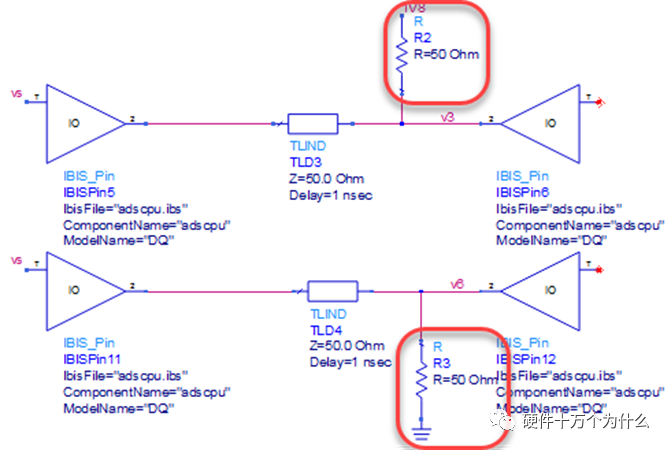

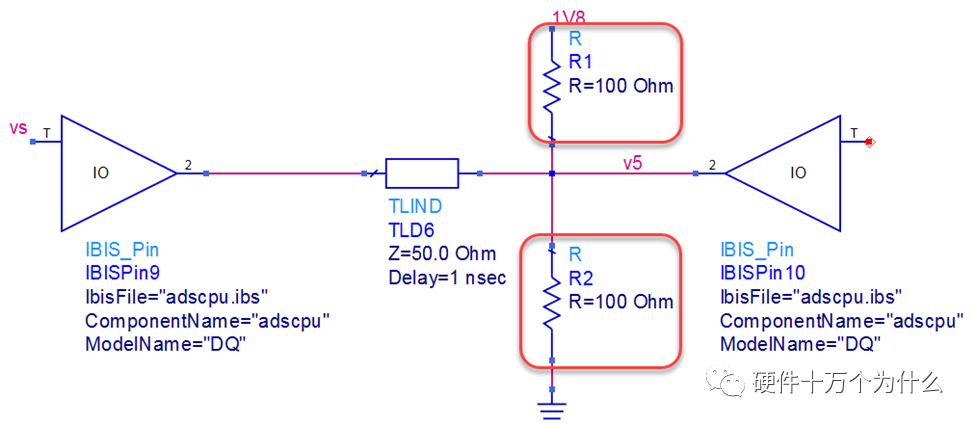

戴维宁端接就是使用两颗电阻组成分压电路,即用上拉电阻R1和下拉电阻R2构成端接,通过R1和R2吸收反射能量。戴维宁端接的等效电阻必须等于走线的特性阻抗。电路拓扑结构,如下图所示:

▲戴维宁端接拓扑结构

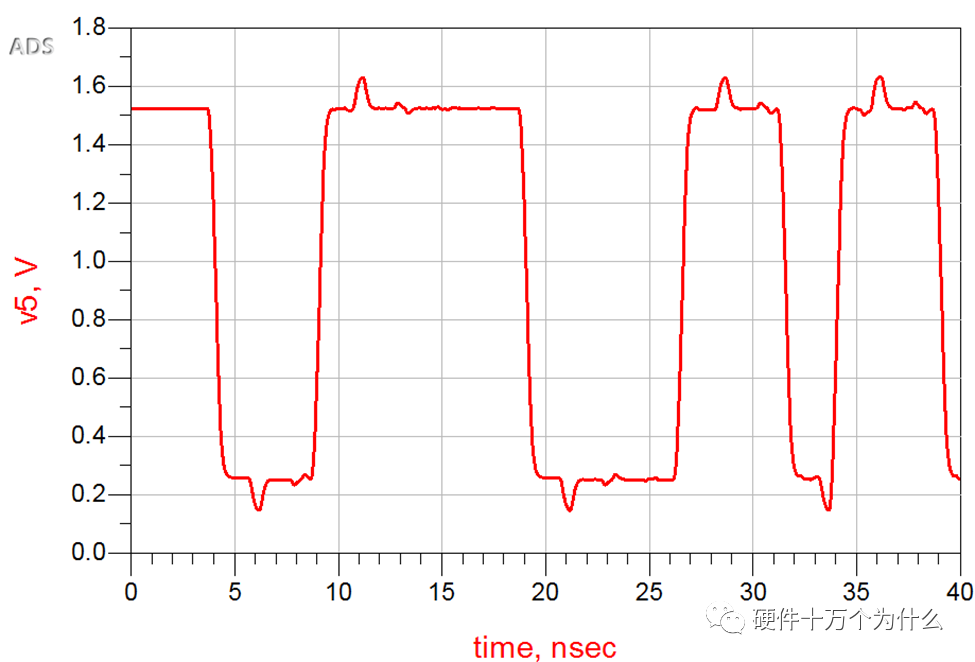

使用戴维宁端接后,其接收端的信号波形,如下图所示:

▲戴维宁端接后的信号波形

从上述信号波形分析,戴维宁端接匹配的效果也非常好,也基本能消除过冲的影响。

戴维宁端接方式,由于一直存在直流功耗,所以对电源的功耗要求比较多,也会降低源端的驱动能力。从信号接收端的波形可以看出,戴维宁端接的幅度降低了,所以噪声容限也被降低。同时,戴维宁端接需要使用两颗分压电阻,电阻的选型也相对比较麻烦,使很多电路设计工程师在使用这类端接时总是非常谨慎。

DDR2和DDR3的数据和数据选通信号网络的ODT端接电路就采用了戴维宁端接。

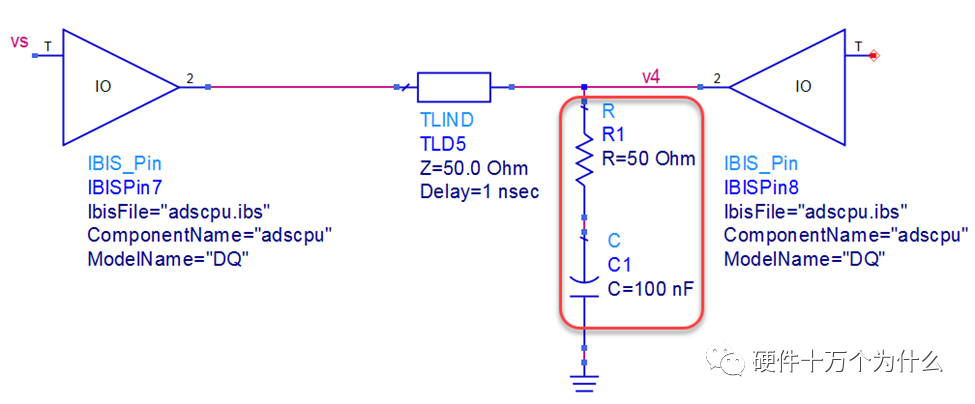

5、RC端接

RC端接在并联下拉端接的电阻下面增加一颗电容,并下拉到地,所以RC端接是由一颗电阻和一颗电容组成的端接。RC端接也可以看作是一种并联端接。电阻值的大小等于传输线的阻抗,电容值通常取值比较小。RC端接电路的拓扑,如下图所示:

▲RC端接拓扑结构

使用RC端接后,其接收端的信号波形,如下图所示:

▲RC端接后的信号波形

从接收端的波形分析,RC端接也使过冲基本被消除了。RC端接能非常好的消除源端带来的反射影响,但是RC电路也有可能导致新的反射。由于RC端接电路中有电容存在,所以电路静态时的直流功耗非常小。

信号波形的低电平电压提升了很多,所以RC端接后电路的噪声容限被降低。RC端接后,由于引入了RC延时电路,所以信号波形边沿也明显的变缓慢,其变化程度与RC端接的电阻值和电容值有直接关系。所以,RC端接并不适合非常高速的信号及时钟电路的端接。同时,RC端接方式需要使用电阻和电容两颗器件。

从上面分析的几种电阻端接类型来看,基本都能达到电路匹配端接的效果,使信号在传递过程中保持信号不失真,即满足信号完整性的设计要求。对于电子产品设计而言,这是一个系统工程,其中涉及各个方面,包括信号完整性设计与电源完整性,也包括电磁兼容性、电路可靠性、可加工性、成本等。那么,在使用电阻端接来解决反射问题时,也要考虑到这些方面的原因。在实际项目的应用中,就需要根据项目工程的应用选择电阻端接的类型。

总而言之,从电气性能的角度来讲,电阻端接匹配不仅仅可以改善信号质量,还可以用于控制信号边沿变化的速率,即控制信号的上升时间;也可以改变信号电平的类型,即起到转换的作用。

来源:硬件十万个为什么

审核编辑:汤梓红

-

电阻

+关注

关注

86文章

5507浏览量

171919 -

pcb

+关注

关注

4319文章

23080浏览量

397494 -

信号

+关注

关注

11文章

2789浏览量

76730 -

拓扑结构

+关注

关注

6文章

323浏览量

39189

原文标题:为什么在PCB走线上串个电阻?有什么用?

文章出处:【微信号:mcu168,微信公众号:硬件攻城狮】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

信号线上串个小电阻干啥用的?

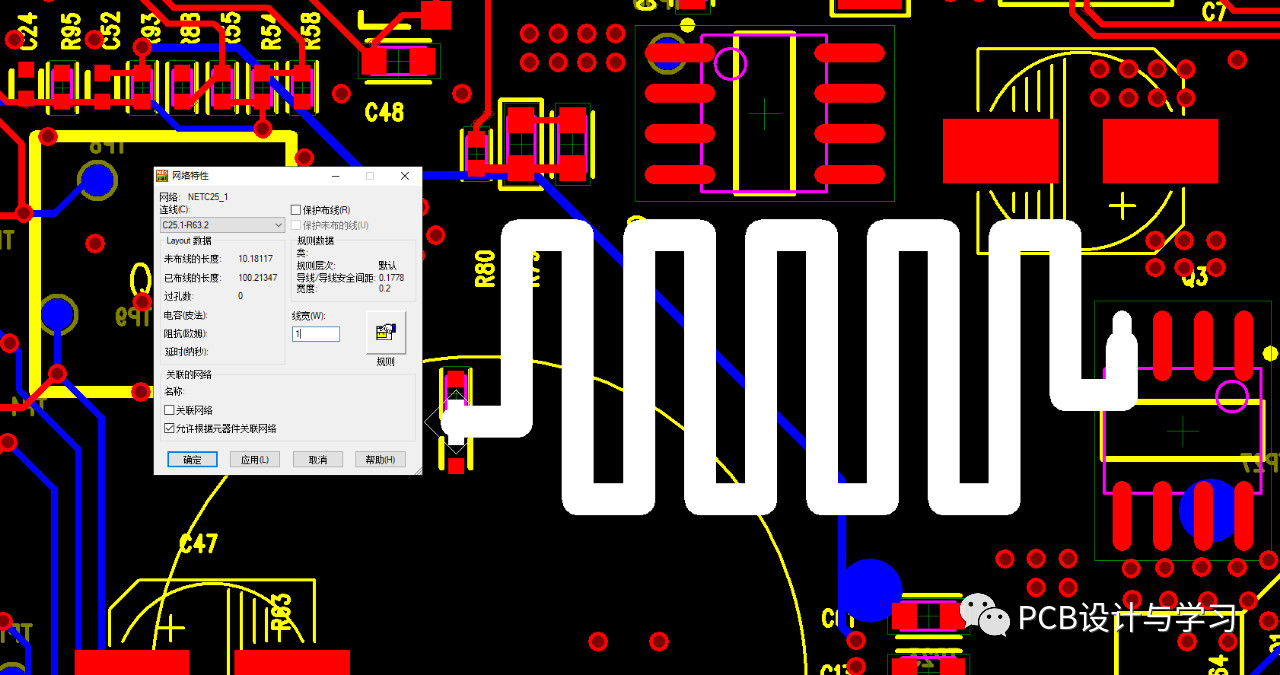

PCB布局之蛇形走线

用PCB走线来设计一个采样电阻

如何利用PCB走线设计一个0.05欧姆的采样电阻?

PCB走线上串个电阻的作用

PCB走线上串个电阻的作用

评论