串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是独立的ASSP 或ASIC 器件。在过去几年中已经看到有内置SERDES 的FPGA 器件系列,但多见于高端FPGA芯片中,而且价格昂贵。

本方案是以CME的低功耗系列FPGA的HR03为平台,实现8/10b的SerDes接口,包括SERDES收发单元,通过完全数字化的方法实现SERDES的CDR(Clock Data Recovery,时钟数据恢复),完成100~200Mhz的板间SERDES单通道通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。

1 硬件接口:

硬件的接口如上图所示,主要包括发送与接收模块。

发送模块包括8b/10b编码器,并串转换器,锁相环(PLL)频率合成器和发送器,接收模块包括 8b/10b解码器,Comma 检测器,串并转换器,时钟数据恢复器(CDR)和接收器。

8b/10b编码器用于将从上层协议芯片发送过来的字节信号映射成直流平衡的 10 位8b/10b 编码,并串转换用于将 10 位编码结果串行化,并串转换所需的高速、低抖动时钟由锁相环提供,发送器用于将 CMOS 电平的高速串行码流转换成抗噪声能力较强的差分信号,经背板连接或光纤信道发送到接收机。

在接收端,接收器将接收到的低摆幅差分信号还原为 CMOS 电平的串行信号,CDR 从串行信号中抽取时钟信息,完成对串行数据的采样,串并转换利用 CDR 恢复的时钟,将串行信号转换成 10 位的并行数据,Comma 检测器检测特殊的 Comma 字符,调整字边界,字边界正确的并行数据经过 8b/10b 解码,还原为字节信号,传送到上层协议芯片,完成整个信息传输过程。

实际的设计中,CDR部分是由纯逻辑电路完成的,为设计的的部分,下面将介绍数字CDR在HR03的实现方案。

2 数字CDR:

CDR模块作用是从数据中恢复嵌入的时钟,然后接收器按照恢复的时钟进行数据位对齐并通过comma进行字对齐。,将数据进行8b/10b解码,供系统使用。

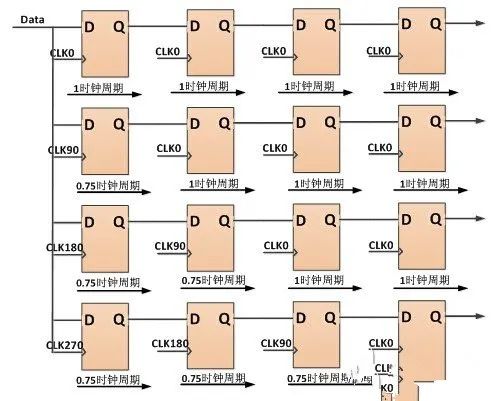

本方案采用同频多相的时钟采样方法,具体实现过程利用PLL产生4个时钟频率相同,相位相差90度的时钟,分别为clk0、clk90、clk180、clk270,这四个时钟输出完全同步,利用4个时钟对数据进行采样,以获得4倍过采样的效果,具体的实现过程如下图所示:

在数据时钟恢复时,将到来的数据分别输入到四个触发器,分别用4个不同的相位进行采样,要注意保证从输入引脚到四个触发器的延迟基本一致。

列触发器的触发分别由时钟CLK0、CLK90、CLK180、CLK270的上升沿触发,按照这样的方式来触发就可以得到四个数据采样点。这样就将原始时钟周期分成了四个单独的90度的区域,如果系统时钟为200MHz,上图所示的电路就相当于产生了800MHz 的采样速率。

仅通过一阶的触发器,输出的采样数据存在亚稳态的问题,因此需对采样点作进一步的处理。这里可将四个采样点通过进一步的触发,除掉亚稳态的问题,从而使采样点移到下一个相同的时钟域。通常,亚稳态的去除要经过两三级的处理,这就使得在有效数据输出前会有数位无效的数据,在数据采样的个阶段,电路检测数据线上数据的传输。当检测到有数据传输时,对传输数据的有效性进行确认。确认数据有效后,输出高电平来指示采样点有数据传输。

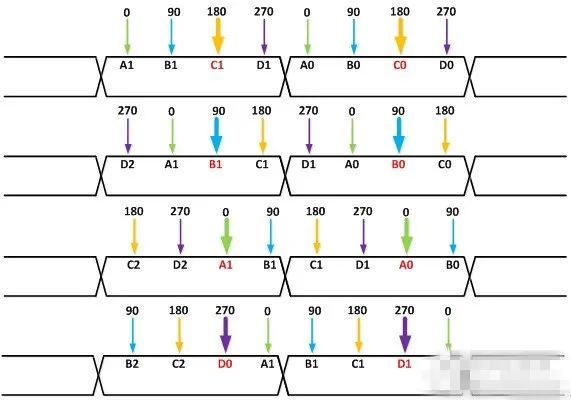

因为终有四个输出,所以需要一个复用器来选择数据。发送数据与采样时钟的对应关系如上图所示,其对应关系分为4种情况,每种情况下对应一个的采样时钟,系统通过对数据边沿位置信息的判断,来确定哪路时钟为采样时钟,并利用复用器从选定的时钟域中选择数据位,例如检测电路确定从时钟域A中采样的数据有效,那么将时钟域A中采样的数据通过输出端输出。

3 结束语:

通过对纯数字电路的CDR电路,在没有硬核的支持下,完成了FPGA上SERDES的接口设计,并通过实验的传输测试,在HR03的FPGA上,可完成100~200Mbps的数据传输。

扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:基于FPGA芯片的SERDES接口电路设计

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1631文章

21806浏览量

606681

原文标题:基于FPGA芯片的SERDES接口电路设计

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

JESD204B有专用于ADC/DAC和FPGA或ASIC的接口吗?

使用FPGA对40G以太网接口芯片Serdes进行测试的方法

使用FPGA的LVDS_serdes模式驱动DP83867E,可以不使用PHY芯片上自带的SGMII_SCO(625MHz)的时钟吗?

lvds接口和HDMI的区别 lvds接口电路设计技巧

国科微斩获“强芯中国创新IC”奖项,车载SerDes芯片渐入佳境

接口芯片的译码电路设计一般采用什么方法

ASP4644在FPGA SERDES供电中的应用

FPGA电路设计的一些技巧

FPGA的sata接口设计时需要注意哪些问题

纯干货!RS485接口电路设计攻略

RS485接口电路设计攻略

基于FPGA芯片的SERDES接口电路设计

基于FPGA芯片的SERDES接口电路设计

评论