新思科技一直致力于打造“人人都能懂”的行业科普视频,传播更多芯片相关小知识,解答各类科技小问题。每周3分钟,多一些“芯”知识。

这一期,我们聊一聊芯片封装的那些事儿。

芯片需要封装,就像行李需要打包一样。因为我们都知道,集成电路是把各种电子元件集成在了一个小小的裸片上,如果不经过封装,别说焊接使用了,就是空气中的灰尘、水分以及射线,就足以对芯片电路造成损伤。

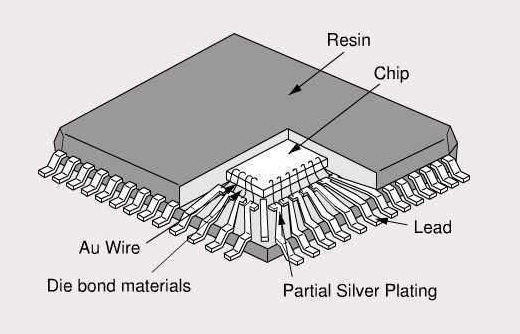

为了保护芯片,我们就得把芯片裹得严严实实的,光是裹上并不难,裹上之后还得能用,那就需要把金属引脚(Lead)拉出来。但这引脚也不能随便拉。本来芯片就不大,引脚间隔过近,难免互相影响。引脚如果太长,又容易导致延迟变高。另外芯片在使用过程中会发热,如果这些热量来不及散发,还可能影响到芯片的使用寿命。所以封装很基本,但是不简单。

因此,我们对封装提出了几个要求:

第一,体积要小;第二,引脚要短,而且不能打架;第三,散热性要好!

本着对这三点的不懈追求,越来越多的封装技术被开发了出来。

传统芯片封装

传统封装通常是指先将圆片切割成单个芯片,再进行封装的工艺形式。主要包含SIP、DIP、SOP、SOT、TO、QFP、QFN、DFN、BGA等等不同形式。就像打包行李可以用双肩包、编织袋、行李箱、纸箱子等等,光是传统的具体封装形式就多达几十种。

但传统封装太过于“传统”,它没办法允许多个芯片封装在一起。这就决定了行李不能被打包成一个大件,只能被装成多个小件。这本来不是什么大问题,而且传统封装也在不断创新,出现了各种新型的封装结构。但随着电子产品及设备的高速化、小型化、系统化、低成本化要求的不断提高,传统封装的局限性就显露出来了。

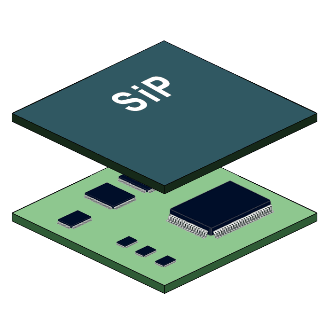

我们知道著名的摩尔定律:集成电路上可以容纳的晶体管数目在大约每经过18个月便会增加一倍。但随着芯片工艺的不断演进,半导体先进制程不断向更小的纳米级别迈进。事情开始变得没那么简单了。受制于其物理瓶颈,多次革新的技术也终于难以维持摩尔定律了。好在异构整合这一概念出现了!异构整合说白了,就是把不同的小芯片统统放进一个大封装里。比如将处理器、存储器等多种功能芯片集成在一个封装内的系统级封装(SiP, System in Package)。

系统级封装

我们之所以能够把不同行李都装进同一个箱子,简单来讲,就是靠的三个字:叠!高!高!

那芯片到底能叠多“高”呢?这么说吧,在不到芝麻粒大小的1平方毫米内可以集成1亿只以上的晶体管!而指甲盖大小的芯片上能够集成超过500亿个晶体管,这可是目前地球上人类数量的6倍左右多!

(顺带一提,先进封装这一概念是指处于当前最前沿的封装形式和技术,也许等几十年后,现在的先进封装就会变成传统封装了。)

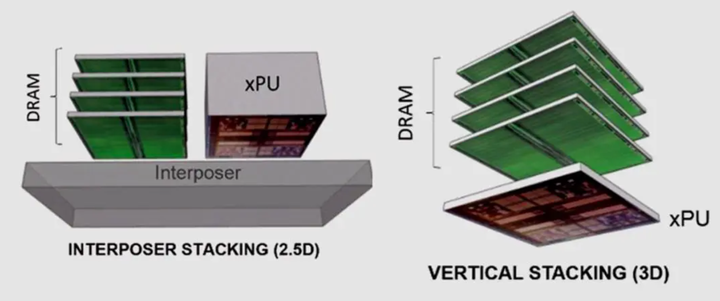

3D封装和2.5D封装就是特别能装的两种:如果比喻成盖房子,3D封装是直接一层一层往上盖,盖成高楼。2.5D封装则是在同一个地基上盖几排房屋。

3D封装在原理上相当简单粗暴:盖楼不就是管它是logic还是memory,往上叠就完事儿了!但在实际技术中的难度却相当高。

“盖高楼”并不简单,实现3D封装的一个关键技术叫做通孔工艺中的TSV技术。借助TSV技术,通过铜、钨、多晶硅等“导线”的填充,可以穿过硅基板实现硅片内部垂直电互联。硅基板就像是钢筋搭出来的一层层楼面;前面这些“导线”就像是贯通整栋楼的水管、燃气管、电路等等系统。将每层楼的供能系统串在一起,同时保障家家户户的用电用水等都随时供给。

因此,这种技术能够有效减小芯片间的互联长度和信号延迟,实现芯片间的低损耗和高速通讯,从而大幅保证芯片性能。随着高效能运算、人工智能等应用的兴起以及TSV技术的逐渐成熟,越来越多的CPU、GPU和记忆体都开始采用3D封装。

那2.5D封装,是不是就是简化版的3D封装呢?还真可以这么讲!

为了解决3D封装中的散热和成本问题,基于硅中介层的2.5D封装设计出现了。2.5D封装最大的区别是在同一基板上安装所有芯片和无源器件,再通过基板进行电气连接。

在2.5D封装中,裸片或堆叠或并排放置在硅中介层(Interposer)的顶部,通过在同一硅中介层上布线和打孔,实现芯片之间的互联。硅中介层是一种由硅和有机材料制成的硅基板,是多芯片模块传递电信号的管道。借助其四通八达的通道,可以让多个芯片自由组合在一起,就像是一个巨型地下交通网络。在TSV技术的加持下,2.5D封装也得以像3D封装那样实现高密度互联。当然对2.5D封装来说,省钱是关键。成本高、难度高的TSV技术并不是必须的。

2.5D封装和3D封装图示

芯片封装技术发展到现在,根据技术细节的差别,各大厂商都有自己的不同命名的封装技术,而业界对于封装的具体分类也并没有一个统一的共识。3D封装的TSV技术和2.5D封装的硅中介层也只是这些封装最显著的特征而已。

出于成本和设计难度的考虑,2.5D集成更适合用于移动设备、笔记本电脑、可穿戴电子设备等应用。3D集成(3DIC)往往更适合用于高性能计算,如数据中心、网络、服务器等。

3DIC这种多层堆叠,就像搭积木,任意一层出现松动都可能导致塌房;互连导通只要出现一环异常,电路即会表现失效。器件密度大大增加,功能复杂性增强;纳米级半导体器件对热量指数性敏感,发热问题一定不可避免。这些都增加了3DIC设计里可靠性设计的挑战难度。

然而各个单一的工具只能解决设计3DIC的部分复杂挑战,这就形成了巨大的设计反馈回路。无法及时将这些反馈整合在一起,就难以得到每立方毫米PPA的最佳解决方案。所以说,3D封装也不是光“封装”就可以的!

在多裸晶(multi-die)环境中,设计工程师需要对完整系统进行分析和优化,孤立地对单个裸晶进行功耗和热量分析是不全面的。更有效的解决方案是采用统一的平台,将整个系统的信号、功耗和热量分析有机整合到单个紧密耦合的解决方案中。这正是新思科技3DIC Compiler的用武之地——通过一套完整的功耗和热量分析能力实现早期分析。该解决方案可通过全面的自动化功能减少了迭代次数,同时提供功耗完整性、热量和噪声感知优化。这有助于开发者更好地了解系统性能,并围绕系统架构、在何处插入TSV以及最高效的裸晶堆叠方法进行探索。另外,它还有助于更有效地了解如何将各种设计要素组合在一起,甚至以某些方式将开发者与传统的2D设计技术联系起来。

尽管使用集成设计平台设计3D架构时会出现新的细微差异,但以最低功耗实现最高性能的可能性(没想到吧,还有这种好事!)使3D架构成为极具吸引力的选择。3DIC也势必将在芯片行业得到更广泛的应用。

-

新思科技

+关注

关注

5文章

796浏览量

50334

原文标题:【了不起的芯片】3D封装:我很能装,只是有点难装

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

2.5D/3D封装技术升级,拉高AI芯片性能天花板

两个wson8封装的dac80501有误差是什么原因?

如何在SOT-563封装和SOT-236封装之间实现共同布局

【了不起的芯片】3D封装:我很能装,只是有点难装

【了不起的芯片】3D封装:我很能装,只是有点难装

评论