背景

随着NAND Flash技术发展,存储厂商通过降低存储单元的大小、采用多阶存储技术(比如MLC、TLC、QLC)或者使用三维堆叠技术,来提高存储密度的目的。但是此举也会带来可靠性问题,比如降低存储单元的大小会导致存储单元中存储的电子数量的减少;多阶存储技术会导致存储单元中代表不同信息的电压区间缩小而影响NAND Flash的可靠性。

在NAND Flash的众多特性里,其中读干扰(Read Disturb)表现为如果对NAND闪存中某个位置进行多次读取,会对同一个块中其它未操作的页造成干扰(数据误码率会越来越高),这种特性的影响程度和读取次数、NAND闪存的架构、块的擦除写入次数、是否满块编程等密切相关,如果不及时处理,会导致误码率超过纠错引擎的范围引发数据丢失。

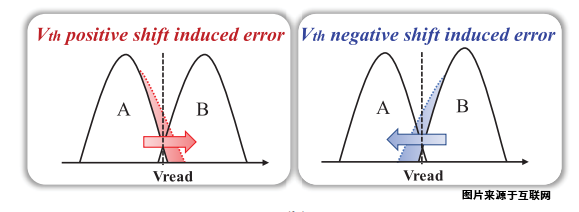

图1:NAND Flash阈值错误

01

固件处理策略

当前业内一般的做法是记录块的读取次数,当达到阈值时就把对应块上面的数据进行搬移,即读回收(Read Reclaim)的操作。然而,在读密集的应用上,读干扰可能会触发大量的数据搬移,提高写放大,且影响前端的响应速度。

得一微电子基于对NAND Flash深入的研究和丰富的处理经验,形成了一套成熟的固件处理方案有效解决读干扰问题,有效提升客户的存储产品体验。

快速扫描干扰块

由于NAND Flash每个block的读耐受程度差异,如果使用单纯记录块计数的办法会不太准确,取一个保守的值会导致无效的读回收,取一个过大的值会导致读回收不及时。

得一微固件团队深入分析NAND Flash的页编码规则,找到对应读干扰造成最大影响的页,固件通过扫描块中的这些页来确认读干扰造成的影响程度,然后把受到干扰的page remap到其它block上,或者对整块进行读回收。

智能选取读参考电压

同样的,在NAND Flash导入时对其特性进行全面分析:包括读干扰对NAND Flash的影响情况,并且找出合理的Vread值。固件在读取目标页的时候,会参考该块受到读干扰影响的情况去选择对应的Vread,从而降低读取数据的出错比特,减少甚至避免read retry,提高指令的响应时间。

热读数据分离

在读密集的应用上,如果热读数据和冷读数据编程在同一个NAND block上,读回收会导致冷读数据回收搬移,带来无效的NAND写入。可以使用得一微自研仿真平台对被测样品的操作序列进行分析,使用有效的策略区分热读数据和冷读数据,把热读数据编程到SLC mode块上,从而降低读回收带来写放大。

02

方案效益分析

测试场景

抓取方式介绍:在平台使用过程中,我们在eMMC中增加log输出,输出内容包括读、写、擦除地址和长度、指令间空闲时间等。在模拟器测试的时候,可以重复注入同一个激励:

日常使用:模拟日常高强度使用手机,包括使用微信、拍照、浏览网页等行为,使用时长10天。

休眠唤醒:使用工具,定期对手机进行休眠唤醒。

读干扰测例:我们内部为专门验证读干扰特性所编写的测试用例,可以快速触发读干扰问题。

实验结果和分析

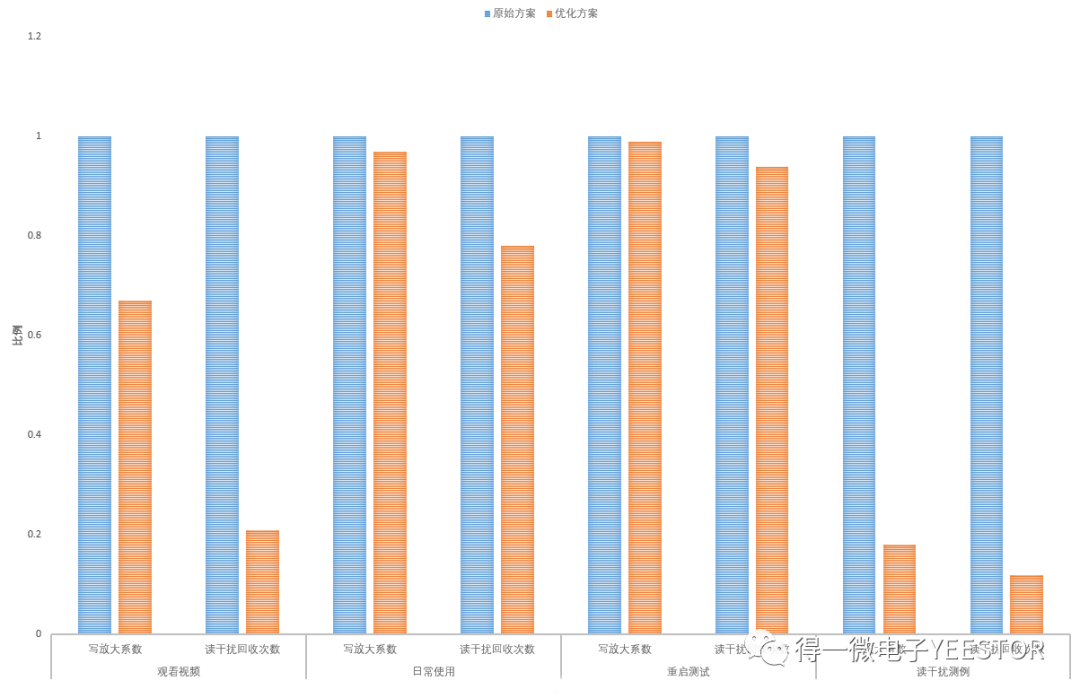

实验对比两个读干扰策略,分别是应用了常规读回收方案的原始方案和应用了固件处理策略的优化方案,对比两个方案的写放大和读干扰触发回收的次数。

实验以原始方案的写放大和读干扰回收次数为基准,比较优化方案和原始方案的对应参数,从而画出图2。

图2:不同读干扰方案参数效益比对

由上述的实验结果我们可以直观的看到,应用了新策略方案的结果较原始方案会更好。在观看视频和读干扰的测例上,读干扰方案优化的效果非常明显;在重启测试上,由于重复读取固定地址的占比不大,所以读干扰方案优化的效果不明显。

总结

得一微自研的算法模拟器是一套完善、高效的固件仿真器,可以把平台对eMMC的操作序列作为激励注入。模拟器拥有完整的NAND Flash模型来模拟读干扰特性,可以快速验证固件处理策略的效果。正是基于此算法模拟器,让得一微的固件团队能够轻松构建NAND Flash读干扰的特征(读耐受次数、影响邻近页的稳定性、Wordline中容易出错的页等),使用不同场景的操作序列作为激励,最后比较采用不同策略固件的关键参数,从而判定策略的适配性。

-

闪存

+关注

关注

16文章

1805浏览量

115173 -

嵌入式

+关注

关注

5096文章

19199浏览量

308300 -

emmc

+关注

关注

7文章

219浏览量

52989

原文标题:嵌入式eMMC存储读干扰应对方案

文章出处:【微信号:SSDFans,微信公众号:SSDFans】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

存储芯未来 视听新生活 | 佰维携嵌入式存储产品亮相CCBN 2023

移动嵌入式WinCE电源管理应对的技巧

国产嵌入式存储新技术助力终端发展

江波龙旗下品牌FORESEE,高稳定性的嵌入式eMMC

eMMC浅析:嵌入式多媒体卡的应用与特性

嵌入式eMMC存储读干扰应对方案

嵌入式eMMC存储读干扰应对方案

评论