LEF和DEF是APR工程师工作中经常会碰到的两类文件,也会对APR的基础配置和APR的flow产生直接的影响。基本相当于APR物理设计的基础建设。

LEF/DEF释义和使用场景

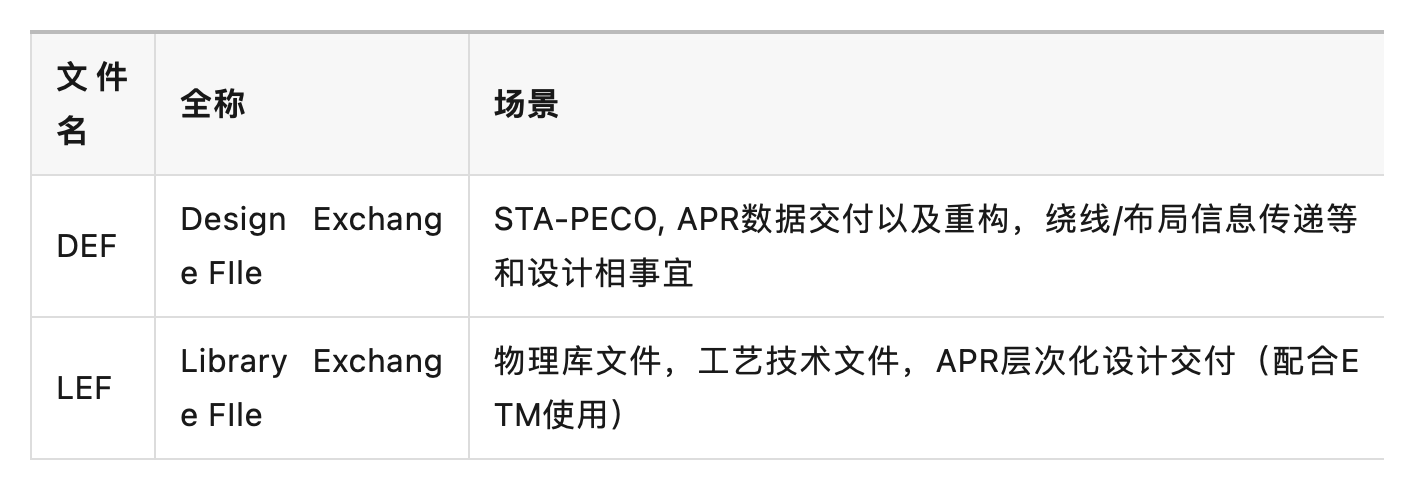

APR工程师碰到的LEF和DEF文件,具体对应的全程和应用场景如下pic_center

| 文件名 | 全称 | 场景 |

|---|---|---|

| DEF | Design Exchange FIle | STA-PECO, APR数据交付以及重构,绕线/布局信息传递等和设计相事宜 |

| LEF | Library Exchange FIle | 物理库文件,工艺技术文件,APR层次化设计交付(配合ETM使用) |

由上可见,里那个文件首字母不同也表征了他们之间的异同:LEF更偏重于库,DEF则侧重于设计。

APR工程师,经常会用到各种库或者库的各种版本进行交互,今天这里就对LEF里边的一两个和APR有关的点滴做一些讨论和解惑。

tech-LEF 通常是FAB交付,这方面通常都是很严谨的,不会有太多意外发生。但是对于IP的交付,不同vendor的策略有时候不太一样,而且IP的LEF对floorplan,placement和routing通常会有直接的影响,在出现问题的时候,需要APR工程师进行定位。所以,如果能掌握LEF中的几个关键信息,甚至在导入flow工具之前,可能就会有一些发现;或者flow出现了一些异常,那么从阅读LEF入手,可能也会得到比较快速的解决办法。基于上,大家一起来看看和APR相关的LEF信息。闲言少叙,ICer Go!

tech-LEF的浅析

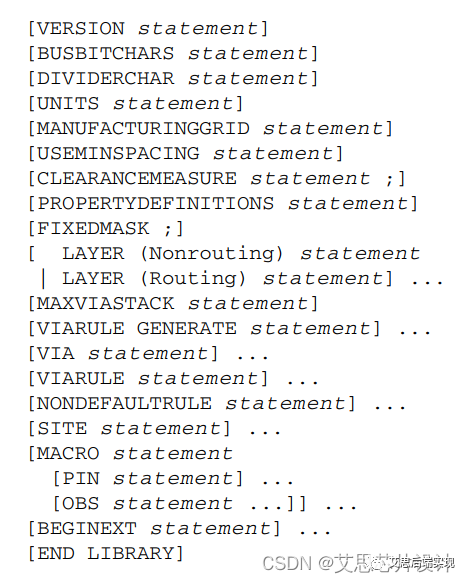

通常一个标准的LEF文件具备以下的格式

这个格式是兼顾了tech-LEF和IP LEF两种应用场景的。IP LEF的定义则是从字段MACRO开始,对于tech-LEF的主要字段,这里用一个简单列表进行快速罗列

| 字段 | 释义 | 示例 |

|---|---|---|

| VERSION | LEF 的版本 | 5.7 |

| BUSBITCHARS | 总线分割符 | [] |

| NAMESCASESENSITIVE | 大小写敏感 | ON |

| UNITS | 定义设计中各种单位的DBU(database unit)和Standard International转换关系 | DATABASE MICRONS 1000 |

| USEMINSPACING | 定义minspacing的应用场景 | USEMINSPACING OBS OFF |

| MANUFACTURINGGRID | 工艺生产格点,cell和routing需要保证的最小grid | MANUFACTURINGGRID 0.001 |

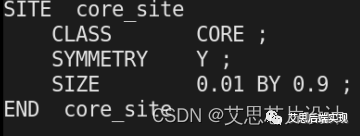

| SITE | 对于std-ecll row的高度和宽度步进的约束 |

|

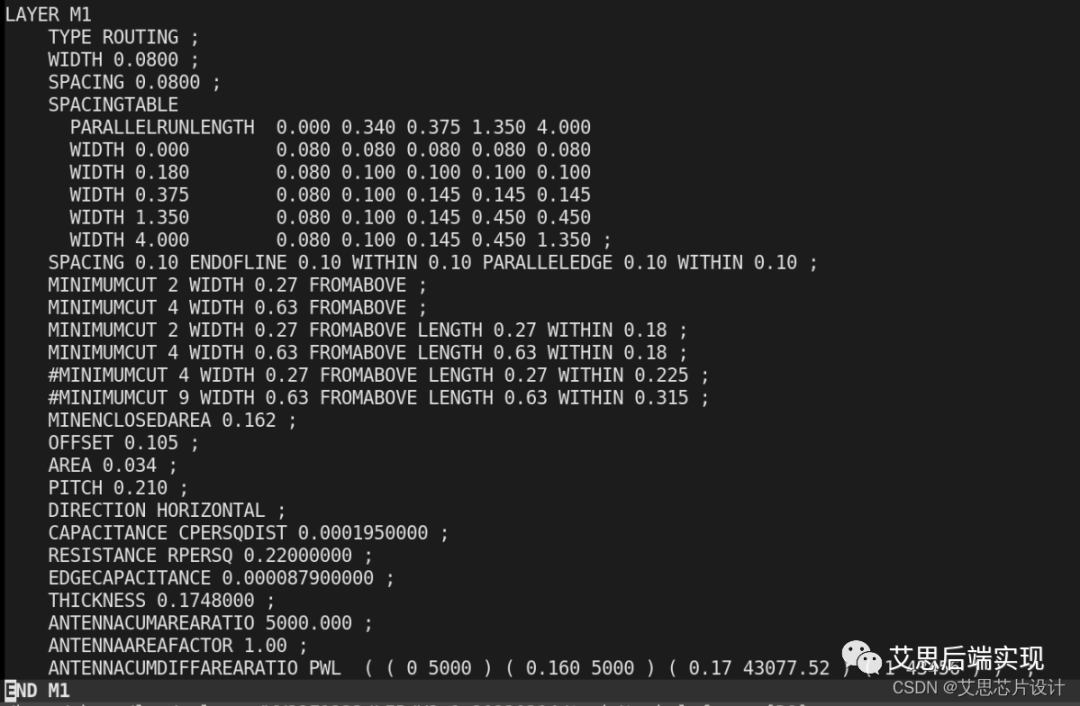

| LAYER |

APR用到的各个层的定义,包括但不限于: 类型(TYPE) 间距(SPCING) 宽度(WIDTH) 面积(AREA) 中心距(pitch)等。 主要是用于约束router绕线规则和checker对绕线质量评估 |

|

对于C家的工具,同学们直接用tech-LEF就好了;如果是S家工具(ICC和ICC2),都需要用到FAB格外提供的technology file (TF)文件,这个文件基本可以等同于tech-LEF,只是流程不同而已。

tech-LEF更像是一个基于FAB-node的物理强需求,这些规则都会对APR工具对各种资源加以权衡和评测,包括但不限于:

| APR资源 | 相关LEF设定 |

|---|---|

| std-cell row | SITE |

|

track per-layer (包括对NDR影响) |

LAYER PITCH |

| layer schame | LAYER |

| layer prefer routing direction | LAYER DIRECTION |

| grid检查 | MANUFACTURINGGRID |

APR工具会对tech-LEF进行解析,从而创建对应的物理设计约束。可以看到,在单位芯片面积下,tech-LEF的上述配置会决断芯片最终的可用资源数量,工艺尺寸(SITE/PITCH/MANUFACTURINGGRIDetc.)越小的tech-LEF文件在各个定义点的数值也就会小,对应的片上资源就会越多。

IP LEF的浅析

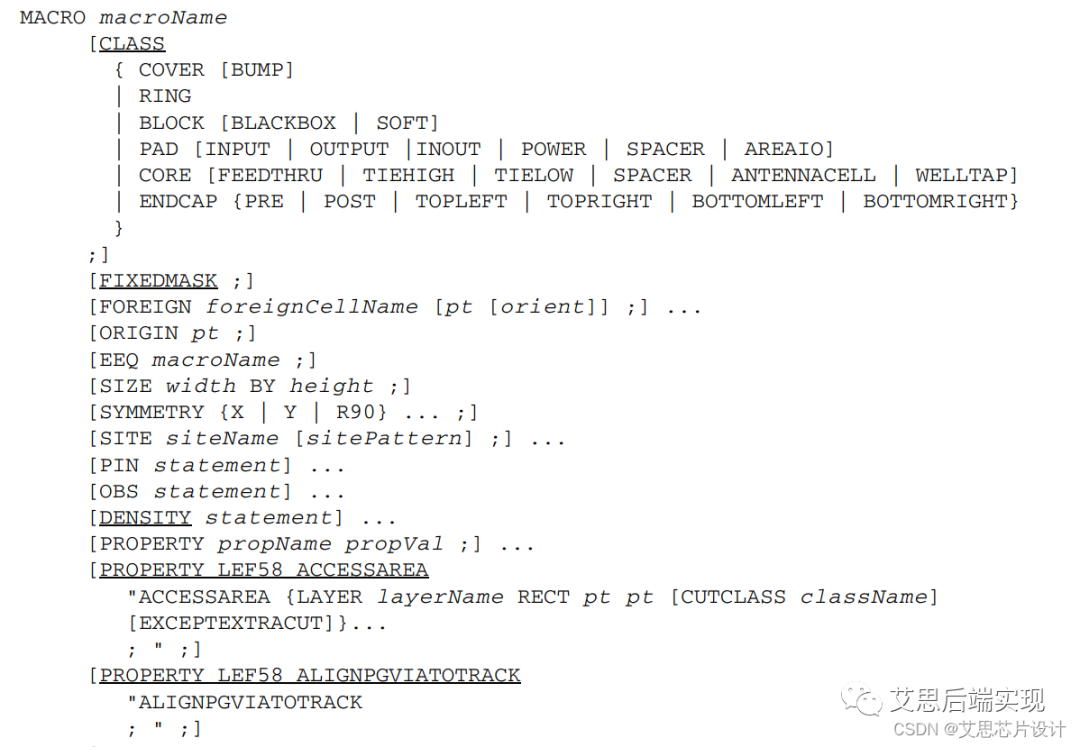

对于IP的LEF文件,通常的会有遵循下述模板

为了兼容LEF5.8,在这个标准模板的后半段,会看到PROPERTY LEF58的字段,通常只有复杂工艺的复杂设计会用到,通常的IP交付,用非LEF5.8字段是足够的。

类似的,APR工具会对IP的LEF进行解析,从而带入IP 对布局,绕线等资源的影响,并在此影响下,完成对IP的集成和最终的GDS 合并(merge)。

CLASS

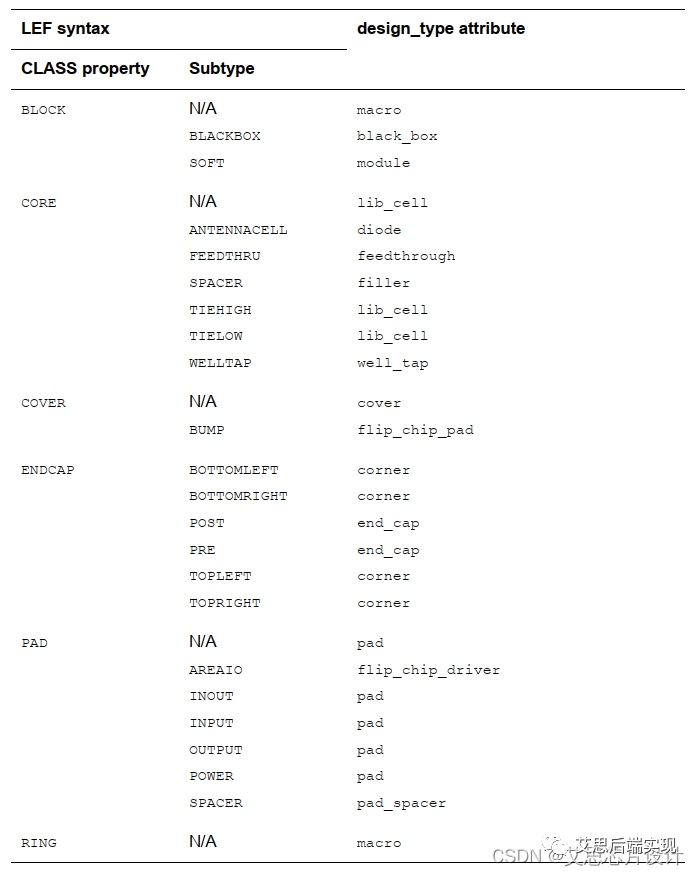

通常是多这个MACRO进行基本分类,这里罗列出他们的释义以及对应S家,C家的工具标记

| 关键字 | S家标记 | C家标记 |

|---|---|---|

| BLOCK | mask_layout_type==macro | cell.subClass ==block |

| RING | mask_layout_type==macro | cell.subClass ==blockRing |

| CORE | mask_layout_type==std | cell.subClass == core |

| PAD | mask_layout_type==io_pad | cell.subClass == pad |

| PAD SPACER | mask_layout_type==io_pad | cell.subClass == padSpacer |

由于C家的flow是直接利用LEF,通常通过cell.subClass既可以直接得到LEF相关的信息,S家的是通过MW/NDM来基于LEF文件来创建的FRAME view提供给ICC/ICC2工具使用,这里会有一些语法正常的转移,以ICC2为例,下表罗列了LEF到NDM FRAME 之间信息映射关系

FOREIGN

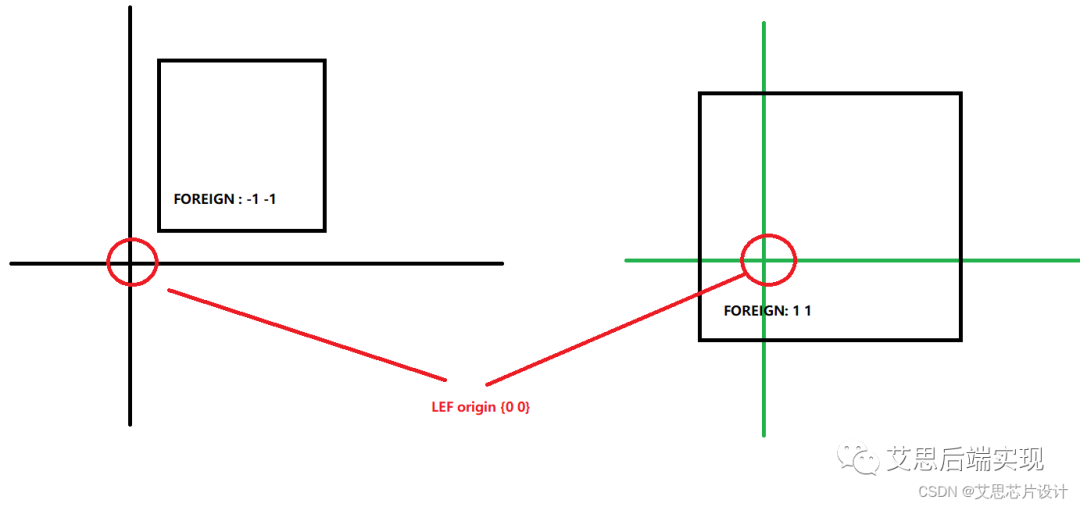

这个是一个标记LEF和GDS之间的偏移量,如果IP的GDS设计的origin 没有落在坐标原点,那么这里可能就会有一个非零数值,GDS起点是在第一象限则FOREIGN为负值,如果是在第三象限,则为正值,具体见下图示例

ORIGIN

这个是指IP在放置的时候,相对于当前origin的偏移量,

假设有下列的IP 配置:

MACRO B1 ...... ORIGIN X1 Y1 FOREIGN B1 X2 Y2

在APR的放置的坐标是:X3 Y3

那么最后B1的GDS polygon抽取的起点是 (X1+X2+X3 Y1+Y2+Y3)

对于通常的IP而言:X1=Y1=X2=Y2=0 。

对于有个GDS相对位移的IP而言:X1 + X2 =0 , Y1+Y2=0

从个人角度理解,这样做的好处是可以缝合GDS偏移和顶层集成的误差,让最后的GDS-out 保持稳定输出。(如有理解偏颇,还望指正)

SIZE

这个字段是描述IP的宽度和高度的,语法格式是:SIZE WIDTH BY HEIGHT. 对于一个矩形的IP而言这个字段可以很方便的通过宽度和高度表达出这个IP的面积:SIZE=WIDTH*HEIGHT

细心的同学可以看到,这里对BLOCK的描述只能是一个简单的矩形,这是LEF规则的一个限制。对于一个多边形的MACRO需要有LAYER的支持。这个后面会讲到。

SYMMETRY

定义IP的朝向(orientation)的限制因素。IP设计者需要关注自己IP在被顶层集成的时候可能会遇到反转、镜像等操作,通过这个句柄可以限制APR工具对IP进行有控制的反转,这样可以有效地避免IP朝向错误所导致的base DRC错误。这个对于IP用户是非常重要的。可配置的选项如下:

| 朝向 | 解释 |

|---|---|

| 如果不定义SYMMETRY,仅允许朝向N | |

| X | 允许水平反转 |

| Y | 允许垂直反转 |

| R90 | 允许90度反转,由于poly 的限制,这种只会在比较大的工艺节点构造里被允许可以 (memory可能会被排除) |

对于常见的std-cell,通常都是可以水平和垂直反转的,那么对应的SYMMETRY的写法是:SYMMETRY X Y

SITE

对于比较规则的IP,SITE会比较有用,譬如std-cell和IO的site,这样APR工具在创建core或者IO-ring的时候,就可以基于site对std-cell和IO进行自动布局,这也是APR placer工具做布局,合规化(legalized)基础,对于普通IP这里也可以不做定义。但是对于先进工艺,

由于coloring/grid的问题,所以在IP上面(尤其是较有规律的SRAM)这个site的应用场景会变得更加丰富了。

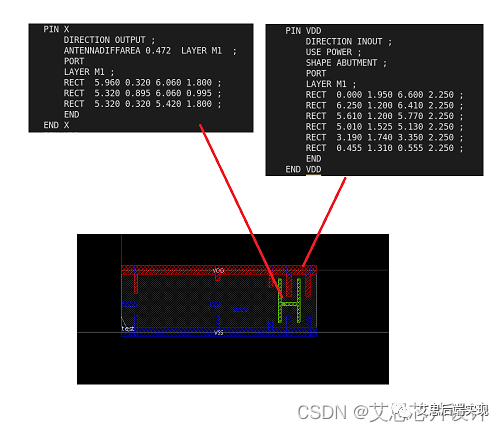

PIN

这里是IP描述的主要部件,给用户提供访问IP的pin的物理位置信息,所有的坐标都是相对于当前IP的左下角(N 朝向)而言的。

这里分别给出信号pin和电源pin两个示例。

对于信号pin,上述示例的信号pin是一个std-cell,为了M1的pin形状需要用三个矩形来描述(rectangle),对应的VDD需要有多达六个矩形来描述

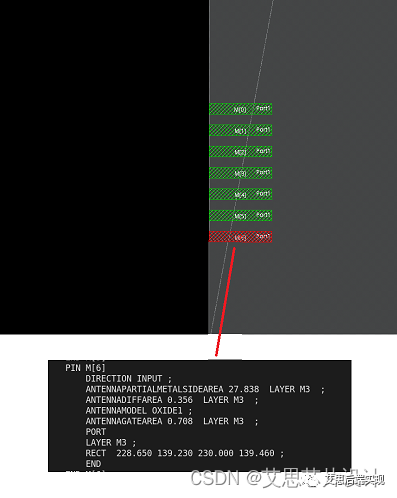

对于IP,通常的pin是abut到boundary的,而且是单rectangle的。示例如下

这个是用户使用IP LEF较常用的一种格式。这里有几个地方需要注意

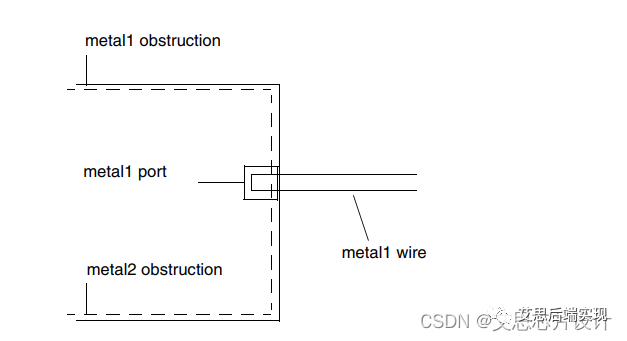

IP的pin需要和IP的boundary贴合,方便外界访问,如果做不到贴合。那么OBS的创建需要注意,至少保证pin可以通过drop via进行访问

IP的pin的width需要满足当前层的min-width需求,长度建议1um,方便绕线和GUI观察

pin和pin之间需要至少控制一个track,这样可以满足潜在的HV spacing 需求

从上述例子可以看出,LEF也是支持antenna的信息的,这样可以支持APR工具在只有LEF的时候也可以对antenna进行评估和修复。

OBS

OBS是Obstruction的缩写,故名思意是对IP的遮挡,对于IP的应用,通常会牵扯到两类遮挡,这个和APR的常规的处理非常相似,

放置遮挡(placement OBS):对APR工具的放置进行阻止

绕线遮挡(routing OBS):对APR工具的绕线进行阻止

由于IP都要自己的SIZE(boundary),如果用户不在这里OBS的句柄里边额外定义,那么IP的SIZE描述的区域都是不能放置其他器件的。

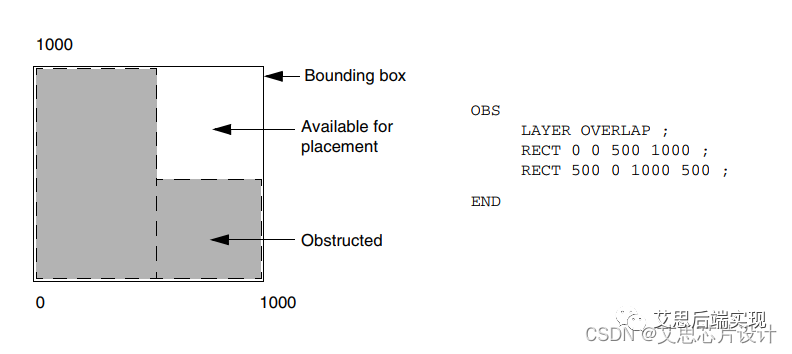

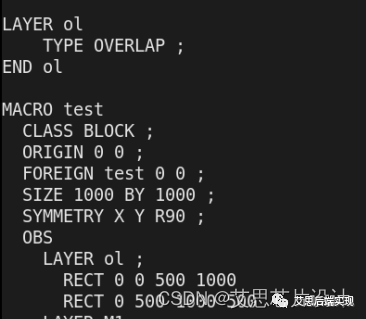

在前文有说道,SIZE只支持矩形,但是如果有了OBS配合就可以支持多边形了。

这里使用OBS调用OVERLAP 类型的LAYER对IP的SIZE进行切割,这样就形成了一个多边形了。这里的OVERLAP是一个特殊层,需要在tech-LEF里边进行预先定义,具体实例如下

这样在APR工具里边就可以看到一个多边形IP了。

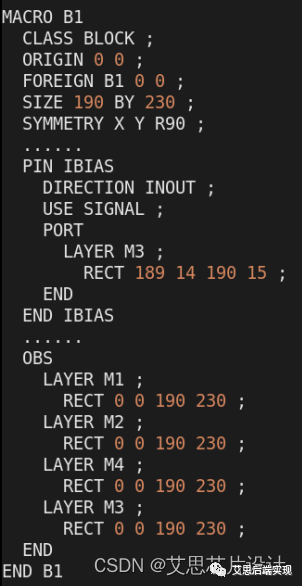

对于绕线遮挡,OBS通过调用routing /cut LAYER 来进行定义。通常如果IP的顶层是M4,那么IP的出pin 也会在M4 和 M3(M4-1)层。这样的规则和APR的partition策略比较相像。

但是通常,出pin的位置都是需要外界绕线直接访问的,所以出pin的位置是不能就想遮挡的,如果IP的顶层是M4,那么最多有一些M4的资源可以始放出来,M4一下的M3/2/1都应该进行遮挡,否则APR工具会在上边走线,这也是OBS存在的重要价值所在。

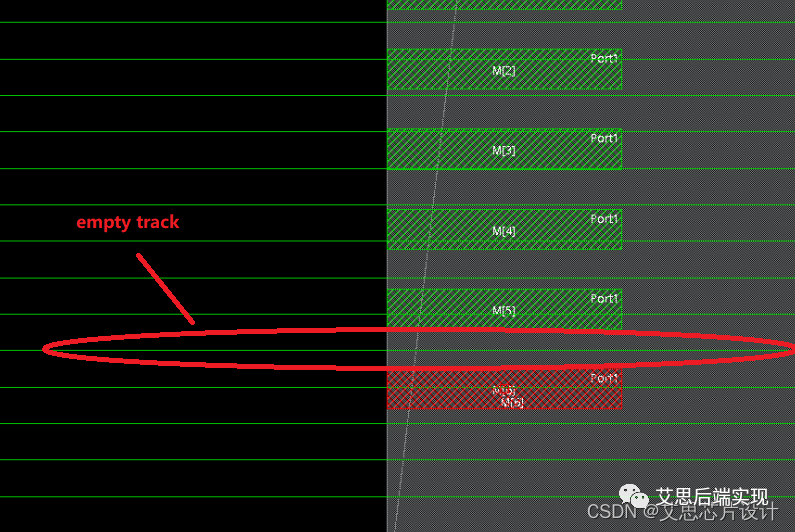

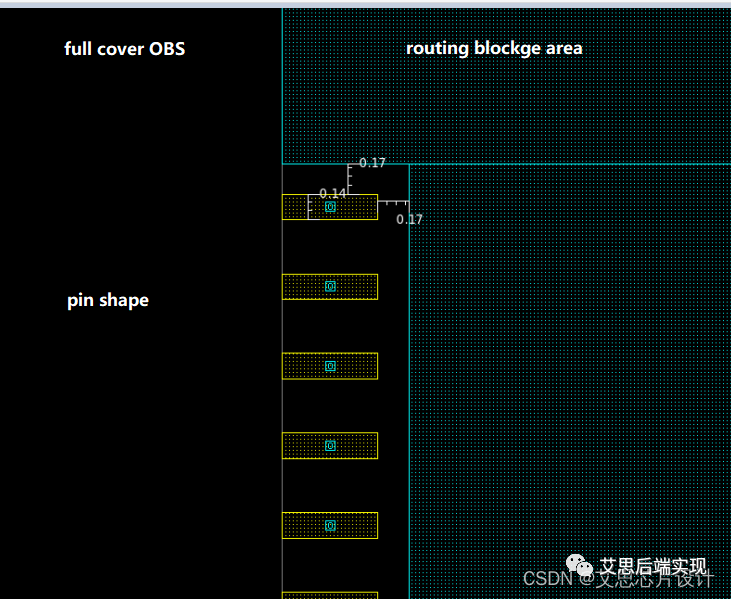

废话不说,有图有真相

从上图可见,这里的IP有一个M1贴合boundary的pin,同时这个IP被M1的OBS覆盖了,但是在LEF规则里,pin bbox拥有覆写OBS的特性,所以在M1 品德周遭,会产生一个OBS空白区,具体跟进pin widh和对应的spacing来调整,这个通过S家的MW,可以很明显的看到

结合上边的理论,一个比较简单的IP的OBS的写法如下

无论是tech-LEF还是IP LEF,都是遵循LEF语法的,可以合并到一起,但是通常由于vendor不同,IP的LEF只关注MACRO 以内的信息,剩下的基本都交由tech-LEF完成,如果用户需要全局的定义更改,请移步tech-LEF进行优化。如果是VIAGEN rule或者NDR rule的更新,也可以项目/工艺的角度进行追加,这种配置更偏向于tech-LEF。

LEF里的关键字有很多。LEF通常也是使用abstract工具从GDS里边抽取出来的,由于APR工具对LEF的强依赖,对于APR工程师,需要可以看到常规的语法就可以,在出现问题的时候可以找到对应的原因和解法,最终还是为了更为高效的推进APR工作。

【敲黑板划重点】

能够阅读LEF是一个APR工程师锦上添花的一个技能,对于快速定位工艺,交付问题可以起到事半功倍的效果。

审核编辑:汤梓红

-

芯片

+关注

关注

457文章

51345浏览量

428260 -

芯片设计

+关注

关注

15文章

1031浏览量

55066 -

IP

+关注

关注

5文章

1724浏览量

150094 -

文件

+关注

关注

1文章

571浏览量

24849

原文标题:芯片设计中的LEF文件浅析

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

支持MC33662LEF的通信收发器

FAT32文件系统浅析

stm32启动文件浅析(二)

浅析芯片设计中的LEF文件

浅析芯片设计中的LEF文件

评论