理解了寄存器的原理,在了解实际电路设计方法之前,先让我们了解一下,在数字集成电路设计时,需要处理一些什么样的信号类型,并且如何通过常用的电路结构实现对这些信号的处理,以便应用到实际电路的设计工程中。

时钟信号

RTL设计以同步电路设计为基础,这意味着在某个局部电路中,所有寄存器都被同一个时钟驱动。

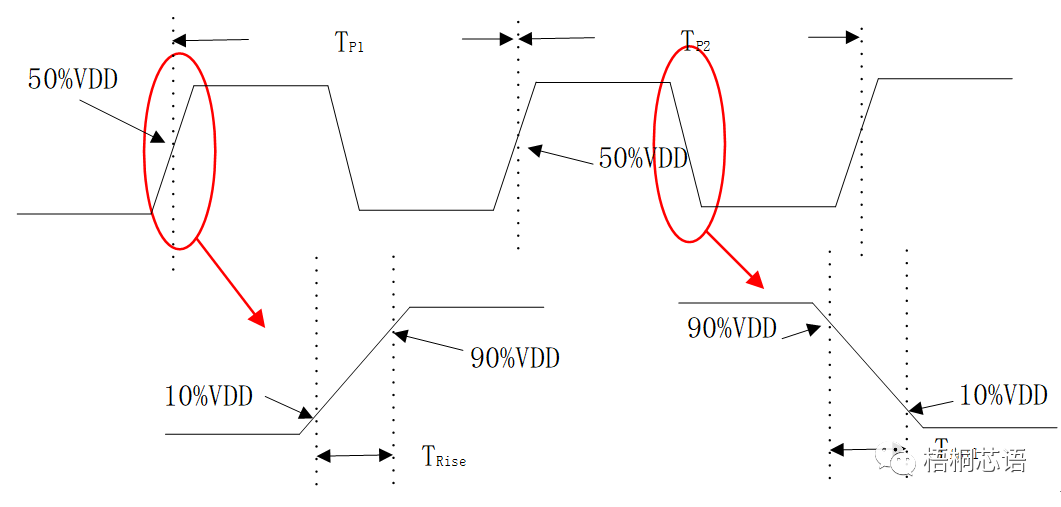

这里所说的时钟,是一种规律性的逻辑电平信号,每隔一个固定周期,就会进行一次电平的翻转。如下图所示:

一般说来,时钟信号包含以下四个关键属性:

- 周期(Period)/频率(Frequency)

时钟信号一次逻辑1和随后一次逻辑0总共持续的时间,被称之为该时钟的时钟周期(Clock Period),测量时一般是从某个上升沿50%VDD到下一个上升沿50%VDD之间的时间,如上图中的TP1和TP2。而周期的倒数,则称之为该时钟工作频率(Clock Frequency)。

比如说,一个时钟信号的时钟周期如果是1ns,则其工作频率就是1/1ns=1GHz。 - Duty Cycle

在一个时钟周期内,该时钟信号电平信号保持为逻辑1的时间,占用整个时钟周期的比例。比如说,一个时钟信号的时钟周期是1ns,而逻辑1的持续时间是0.3ns,则该时钟信号的duty cycle为0.3/1=30%。

一般来说,我们希望使用的时钟,是一个duty cycle为50%的驱动信号。原因是如果使用该时钟的反相时钟,则其反相时钟的duty cycle仍然能保持50%,这在电路设计或时序收敛时,会更容易实现,电路设计的工作频率也更容易提高。 - 时钟抖动(Jitter)

时钟抖动,Jitter,有2种概念:

一种是相邻周期时钟抖动,即相邻2个周期的时钟周期差值。以上图所示,即为,这种差值主要会影响时序分析中setup timing的计算,需要添加在时钟路径上。

另一种是时钟源最大抖动,即某时钟产生源,比如说晶体振荡器(Oscillator)、锁相环(PLL、DLL)等,在不同工作环境(如温度、电压、湿度、负载等)、不同生产批次(生产工艺偏差),同一个配置条件下,可能产生的最大时钟周期与最小时钟周期的差值。该数值主要用于评估时钟产生源的质量。 - 变换时间(Transition Time)

字面理解transition time即时钟变换时间,可以理解为时钟上升或下降需要的时间,这与其他逻辑信号中transition time是一个概念。如图中所示TRise以及TFall,分别表示时钟信号的上升时间和下降时间。一般工程上认定的测量方式,是10%VDD与90%VDD之间的变换时间。实际在标准单元库的时序建模时,一部分测量点使用了30%VDD和70%VDD并进行数学延展,可以参考标准单元库的使用说明文件来进一步理解。

与普通逻辑信号的transition time相比,为了更好的控制时钟质量,需要尽可能减小其数值,以减小对setup或hold时序违背的影响。其次在设计时钟驱动电路时,需要尽可能的平衡输出端PMOS和NMOS的驱动能力,已获得相当的上升沿和下降沿变换时间,由此提高驱动电路输出信号的噪声容限。

在RTL设计当中,只要是驱动时序逻辑元件(如寄存器、锁存器)时钟输入端的信号,都会被默认为时钟信号。如下图所示,流经S-D1和S-D2两段路径的信号都会被看做时钟信号,

而针对驱动每一个时序逻辑元件的时钟输入端,则额外存在以下2个关键属性:

- 时钟延时(Clock Latency)

时钟延时,即从时钟源到达该元件时钟驱动端的延时。如T1与T2,会因为经过不同的逻辑,到达所需驱动时序元件的延时有所不同。控制T1和T2以及同样从S端到达其他寄存器延时尽量相同,叫做时钟树平衡(Clock Tree Balance),是时序收敛的重要手段。

- 时钟延时差(Clock Skew)

可以看出,从同一个时钟源,到达不同元件的时钟驱动端,都会有所不同。则T1与T2的差值,就可以看成两个寄存器的时钟延时差,即Clock Skew,当然对于从S端到达所有需要驱动的寄存器,时钟延时最大值与最小值只差,就是这颗时钟树的Clock Skew。

刚才说了,为了做时钟树平衡,需要尽量减少Clock Skew,不过,在具体工程时,可能会因为功耗设计、特殊路径优化等的需要,在时钟树上,为某些特定的叶部(对于时钟树来说,把源头看成根部root,则每一个时序逻辑终点叫做叶部,即leaf)增加Latency,以加大clock skew。

电平信号与脉冲信号

RTL的设计是建立在同步电路基础上的,因此寄存器与寄存器之间的通讯,都是通过时钟作为同步信号来实现的。这里所说的电平信号,一般指信号宽度大于等于2个时钟周期的数据。而脉冲信号,这里指只有1个时钟周期信号宽度的数据。

而对于远远小于1个时钟周期信号宽度的数据,行业内多数称之为毛刺,是不可靠的数据。

-

寄存器

+关注

关注

31文章

5390浏览量

121874 -

数字信号

+关注

关注

2文章

984浏览量

47797 -

RTL

+关注

关注

1文章

386浏览量

60164 -

VDD

+关注

关注

1文章

313浏览量

34076 -

PLL电路

+关注

关注

0文章

92浏览量

6538

发布评论请先 登录

相关推荐

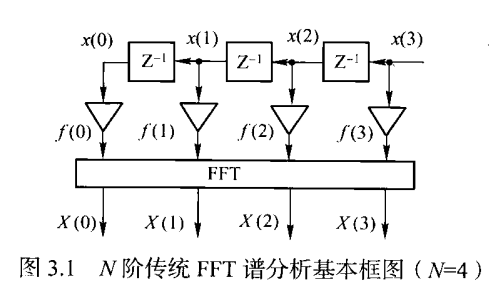

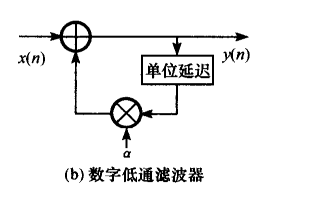

数字信号处理实践方法——EC.Ifeachor著,罗鹏飞等译

数字信号的纠错原因及解决方法

数字信号全相位谱分析与滤波技术的PDF电子书免费下载

RTL设计方法学及设计原理之数字信号的类型分析

RTL设计方法学及设计原理之数字信号的类型分析

评论