目录预览

1 引言2 STM32 DCMI3 小结

1. 引言

随着市场对更高图像质量的需求不断增加,成像技术持续发展,各种新兴技术(例如3D、计算、运动和红外线)的不断涌现。如今的成像应用对高质量、易用性、能耗效率、高集成度、快速上市和成本效益提出了全面要求。为了满足这些要求,STM32 MCU 内置的数字照相机接口(DCMI),能够高效连接并行照相机模块。 对于使用STM32 DCMI 开发相机应用的客户,经常有以下问题:STM32 DCMI 最大支持的像素时钟是多少?STM32F4/F7/H7/U5 能支持1280×720 的相机分辨率吗?最大的帧率是多少?如何判断所设计的应用产生的带宽是否能充足?相机输出是选择8 位、10位、12 位、还是14 位? 针对这些问题,本文档从DCMI 使用的几个方面,介绍了STM32 DCMI 在连续抓取模式下带宽的估算,以及提升性能需要注意的事项。客户在设计相机应用时可以参考。2.STM32 DCMI

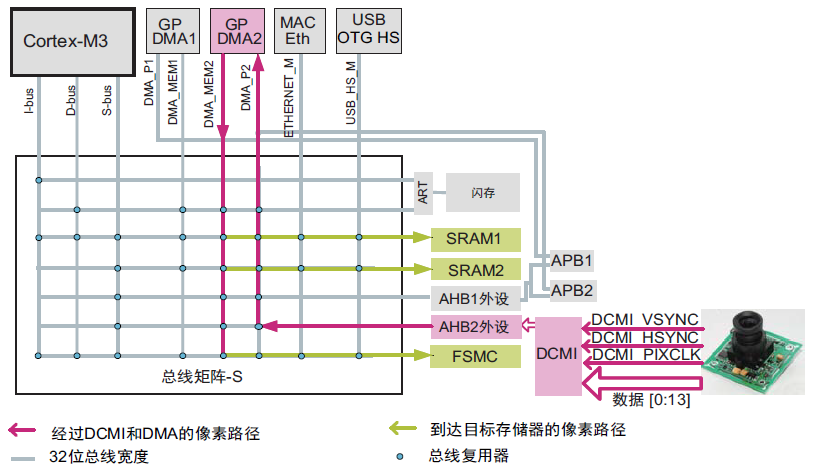

STM32 数字照相机接口(DCMI)采用同步并行数据总线。它可以轻松集成并适应相机的特殊应用要求。DCMI 可连接8、10、12 和14 位CMOS 照相机模块,并支持多种数据格式:8/10/12/14 位逐行视频、YCbCr42 逐行视频、RGB565 逐行视频、JPEG 等。像素最大支持16 位色深。 2.1. STM32 智能架构中的DCMI DCMI 应用需要用帧缓冲区来存储采集的图像。必须根据图像大小和传输速度使用合适的目标存储区。在某些应用中,必须连接外部存储器(SDRAM),以便提供较大的数据存储空间。对于支持DMA2D(Chrom-ART Accelerator控制器)的STM32 系列,也可以用它做色彩空间转换(例如RGB565 至ARGB8888),或使用DMA 从一个存储区到另一个存储区的数据转移。 下面图1 是STM32F2x7 系列智能架构中DCMI 的例子。这里DCMI 通过AHB2 外设总线连接到AHB 总线矩阵。DMA2 主控访问DCMI,将DCMI 接收到的图像数据传输到内部RAM 或外部SDRAM 中,具体目标位置取决于应用。 图1. STM32F2x7系列智能架构中的DCMI从设备AHB2外设2.2. DCMI 最大像素时钟频率STM32 DCMI支持的像素时钟频率,与AHB时钟频率比值必须小于0.4。具体的像素时钟频率最大值要查询所用STM32的数据手册。下面表1中列出了部分STM32系列DCMI最大像素时钟频率及相关可用资源的信息。如需更详细信息,请参考相应的参考手册/数据手册。

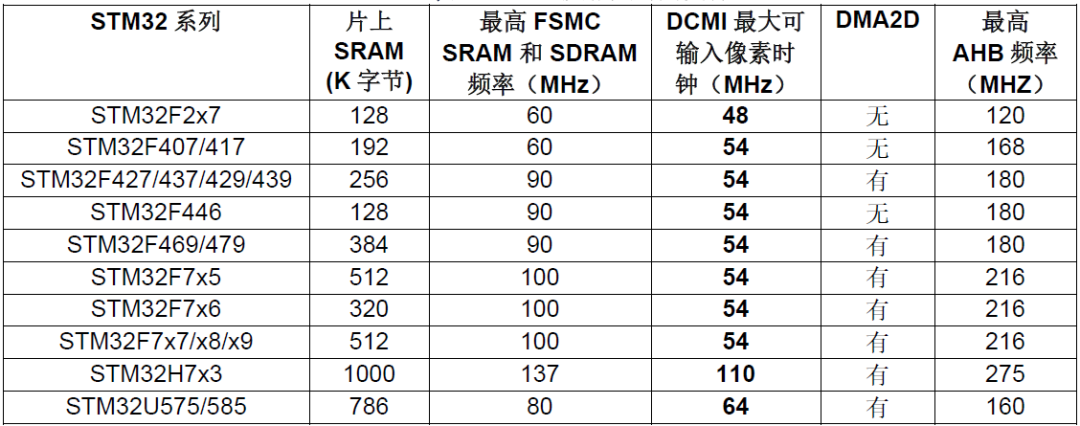

图1. STM32F2x7系列智能架构中的DCMI从设备AHB2外设2.2. DCMI 最大像素时钟频率STM32 DCMI支持的像素时钟频率,与AHB时钟频率比值必须小于0.4。具体的像素时钟频率最大值要查询所用STM32的数据手册。下面表1中列出了部分STM32系列DCMI最大像素时钟频率及相关可用资源的信息。如需更详细信息,请参考相应的参考手册/数据手册。 表1. DCMI及相关可用资源2.3. DCMI 支持的图像分辨率STM32 DCMI仅对输入像素时钟频率有硬件限制(DCMI_PCLK / fHCLK 最大0.4),对图像的分辨率没有限制。DCMI连续抓取模式下,图像分辨率会影响帧率(帧率的大小会影响视频的流畅度)。在固定的像素时钟频率下,高分辨率图像的带宽需求较高,对应的帧率则会下降。或者说,在相同的图像分辨率下,提高帧率需要相应地提高像素时钟频率。例如下表2(摘自三星S5K5CAGA CMOS Image Sensor的数据手册)所示,大家可以从中了解S5K5CAGA的像素频率、图像分辨率、帧率的关系(非RGB888,16位色深)。另外,图像分辨率主要通过设置相机的输出格式进行修改。

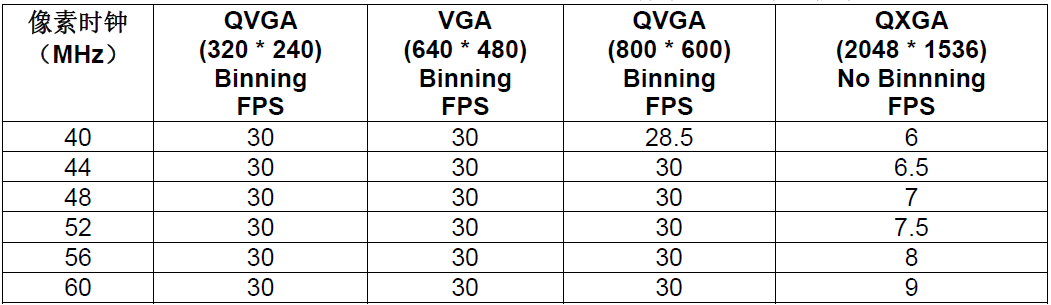

表1. DCMI及相关可用资源2.3. DCMI 支持的图像分辨率STM32 DCMI仅对输入像素时钟频率有硬件限制(DCMI_PCLK / fHCLK 最大0.4),对图像的分辨率没有限制。DCMI连续抓取模式下,图像分辨率会影响帧率(帧率的大小会影响视频的流畅度)。在固定的像素时钟频率下,高分辨率图像的带宽需求较高,对应的帧率则会下降。或者说,在相同的图像分辨率下,提高帧率需要相应地提高像素时钟频率。例如下表2(摘自三星S5K5CAGA CMOS Image Sensor的数据手册)所示,大家可以从中了解S5K5CAGA的像素频率、图像分辨率、帧率的关系(非RGB888,16位色深)。另外,图像分辨率主要通过设置相机的输出格式进行修改。 表2. S5K5CAGA YUV/RGB565像素时钟频率与帧率对于中高分辨率的图像,一般采用双缓冲区或多缓冲区模式。这个主要原因是因为DCMI使用的DMA计数寄存器SxNDTR使用了16位用于计数。最大0xFFFF,即 65535 ,单位为32位Word,当图像分辨率超过65535 Words(262140字节)时,则要使用双缓冲区或多缓冲区模式。双缓冲区地址由DMA_SxM0AR/DMA_SxM1AR设定。多缓冲区时,则需要动态交替DMA_SxM0AR/DMA_SxM1AR,使之指向图像缓冲区的不同存储位置,相当于分块存储。2.4. DCMI 带宽与性能使用DCMI的相机应用,使用连续抓取模式,功能往往是由相机连续输出所摄图像数据流到STM32,STM32 DCMI捕获视频流后,再输出到屏幕显示(如监控)或做图像数据处理、传输等。如果相机输出的是高像素高色深高帧率的视频流,DCMI在接收过程中,如不能及时处理,DCMI FIFO即会产生溢出错误(Overrun),进而导致图像数据丢失,帧率下降等问题。2.4.1. DCMI 带宽与性能DCMI带宽计算公式为:带宽 = 分辨率 * 色深 * 帧率。以三星S5K5CAGA为例,如表2中第1行数据(这里相机采用RGB565,16位/像素,8位输出格式),则QXGA输出的带宽需求 =(2048 * 1536)* 2 * 6 ≈ 38MBps。像素时钟为40MHz,8位输出,每2个CLK传输1个像素数据,对应的最大输出能力为40 MBps。则QXGA在40MHz的像素时钟频率下是可以以6帧/秒的帧率输入到DCMI的。DCMI捕获图像数据流,再由DMA传输到图像缓冲区,该例中,图像缓冲区(帧缓冲区)的大小为:2048 * 1546 * 2 ≈ 6.3 MByte。高像素高色深的图像,对应的图像缓冲区较大。当MCU内置的SRAM不能满足DCMI图像缓冲区需求时,则需要用外部SDRAM来存储。例如STM32F469 MCU(见表1,第6行数据),其FSMC支持的最大频率为90MHz,宽度32位,则SDRAM的带宽 = 90 * 4 = 360 MBps,能够满足DCMI带宽的需求。一般,DCMI图像缓冲区中的数据是需要再次传输或由CPU进行计算处理的,理论上DCMI输入的带宽需求最大不应超过SDRAM的带宽的50%。这里需要注意SDRAM可能存在多个主控(如CPU、DMA、LTDC等)的访问,如遇到SDRAM性能瓶颈问题,可考虑下列方面进行优化:(1)将各主控设备访问的存储器尽量分开,以减少竞争访问;(2)将CPU访问的SDRAM Bank 与DCMI图像缓冲区的Bank分开;(3)将DCMI图像缓冲区区域设为不可缓冲,CPU 访问的区域则可以设为可缓冲。对于性能,另外一个重要因素是总线竞争问题。DCMI DMA申请的AHB总线访问(即使在使用FIFO的情况下)并非长Burst的访问。如果AHB总线上存在其它长Burst访问(最大1KByte),会造成DMA延迟访问DCMI,令其不能及时将DCMI FIFO中的数据传输出去。可以认定:DCMI需要传输数据时的总线繁忙是造成 其FIFO 溢出错误的根源。解决办法除了直接为设备分配不同SDRAM之外(将长Burst访问放在其他SDRAM),还可以考虑在内部SRAM增设DCMI LineBuffer,化零为整,巧妙避开AHB 长Burst 访问造成的DCMI延迟问题。数据流如下:(1)DCMI(经DMA)=> 内部SRAM(LineBuffer) ;(2)内部SRAM(LineBuffer)=> 外部SDRAM(图像Buffer)。由LineBuffer 到SDRAM的数据中转传输请求,可使用DCMI IT_LINE 中断(行结束)触发。这里MCU如果是STM32F7/H7系列,还可使用MDMA 充分发挥AXI总线的优势,但要注意LineBuffer 最好是8字节的倍数(64位总线)。2.4.2. DCMI 图像大小调整功能当考虑了上面的措施,仍无法满足应用对高分辨率需求时,用户可以通过设置相机,修改相机输出分辨率,配合DCMI调整图像大小功能,找到合适的折中方案。DCMI提供的相关功能如下:(1)窗口裁剪:使用寄存器DCMI_CWSTRT指定起始坐标;使用寄存器DCMI_CWSIZE指定窗口大小。(2)图像数据调整(详见寄存器DCMI_CS中LSM/BSM等位域):- 行选择:可选择2选1,行数减半;- 数据选择:字节流上可进行2选1、4选1已经4选2 (注意:对于RGB565格式, 只能4选2可选,2选1及4选1会造成色彩数据错乱)。

表2. S5K5CAGA YUV/RGB565像素时钟频率与帧率对于中高分辨率的图像,一般采用双缓冲区或多缓冲区模式。这个主要原因是因为DCMI使用的DMA计数寄存器SxNDTR使用了16位用于计数。最大0xFFFF,即 65535 ,单位为32位Word,当图像分辨率超过65535 Words(262140字节)时,则要使用双缓冲区或多缓冲区模式。双缓冲区地址由DMA_SxM0AR/DMA_SxM1AR设定。多缓冲区时,则需要动态交替DMA_SxM0AR/DMA_SxM1AR,使之指向图像缓冲区的不同存储位置,相当于分块存储。2.4. DCMI 带宽与性能使用DCMI的相机应用,使用连续抓取模式,功能往往是由相机连续输出所摄图像数据流到STM32,STM32 DCMI捕获视频流后,再输出到屏幕显示(如监控)或做图像数据处理、传输等。如果相机输出的是高像素高色深高帧率的视频流,DCMI在接收过程中,如不能及时处理,DCMI FIFO即会产生溢出错误(Overrun),进而导致图像数据丢失,帧率下降等问题。2.4.1. DCMI 带宽与性能DCMI带宽计算公式为:带宽 = 分辨率 * 色深 * 帧率。以三星S5K5CAGA为例,如表2中第1行数据(这里相机采用RGB565,16位/像素,8位输出格式),则QXGA输出的带宽需求 =(2048 * 1536)* 2 * 6 ≈ 38MBps。像素时钟为40MHz,8位输出,每2个CLK传输1个像素数据,对应的最大输出能力为40 MBps。则QXGA在40MHz的像素时钟频率下是可以以6帧/秒的帧率输入到DCMI的。DCMI捕获图像数据流,再由DMA传输到图像缓冲区,该例中,图像缓冲区(帧缓冲区)的大小为:2048 * 1546 * 2 ≈ 6.3 MByte。高像素高色深的图像,对应的图像缓冲区较大。当MCU内置的SRAM不能满足DCMI图像缓冲区需求时,则需要用外部SDRAM来存储。例如STM32F469 MCU(见表1,第6行数据),其FSMC支持的最大频率为90MHz,宽度32位,则SDRAM的带宽 = 90 * 4 = 360 MBps,能够满足DCMI带宽的需求。一般,DCMI图像缓冲区中的数据是需要再次传输或由CPU进行计算处理的,理论上DCMI输入的带宽需求最大不应超过SDRAM的带宽的50%。这里需要注意SDRAM可能存在多个主控(如CPU、DMA、LTDC等)的访问,如遇到SDRAM性能瓶颈问题,可考虑下列方面进行优化:(1)将各主控设备访问的存储器尽量分开,以减少竞争访问;(2)将CPU访问的SDRAM Bank 与DCMI图像缓冲区的Bank分开;(3)将DCMI图像缓冲区区域设为不可缓冲,CPU 访问的区域则可以设为可缓冲。对于性能,另外一个重要因素是总线竞争问题。DCMI DMA申请的AHB总线访问(即使在使用FIFO的情况下)并非长Burst的访问。如果AHB总线上存在其它长Burst访问(最大1KByte),会造成DMA延迟访问DCMI,令其不能及时将DCMI FIFO中的数据传输出去。可以认定:DCMI需要传输数据时的总线繁忙是造成 其FIFO 溢出错误的根源。解决办法除了直接为设备分配不同SDRAM之外(将长Burst访问放在其他SDRAM),还可以考虑在内部SRAM增设DCMI LineBuffer,化零为整,巧妙避开AHB 长Burst 访问造成的DCMI延迟问题。数据流如下:(1)DCMI(经DMA)=> 内部SRAM(LineBuffer) ;(2)内部SRAM(LineBuffer)=> 外部SDRAM(图像Buffer)。由LineBuffer 到SDRAM的数据中转传输请求,可使用DCMI IT_LINE 中断(行结束)触发。这里MCU如果是STM32F7/H7系列,还可使用MDMA 充分发挥AXI总线的优势,但要注意LineBuffer 最好是8字节的倍数(64位总线)。2.4.2. DCMI 图像大小调整功能当考虑了上面的措施,仍无法满足应用对高分辨率需求时,用户可以通过设置相机,修改相机输出分辨率,配合DCMI调整图像大小功能,找到合适的折中方案。DCMI提供的相关功能如下:(1)窗口裁剪:使用寄存器DCMI_CWSTRT指定起始坐标;使用寄存器DCMI_CWSIZE指定窗口大小。(2)图像数据调整(详见寄存器DCMI_CS中LSM/BSM等位域):- 行选择:可选择2选1,行数减半;- 数据选择:字节流上可进行2选1、4选1已经4选2 (注意:对于RGB565格式, 只能4选2可选,2选1及4选1会造成色彩数据错乱)。2.5. DCMI 10/12/14数据线输入

DCMI 支持最多14条数据线(D13 - D0),如果将DCMI配置为接收10、12或14位数据,DCMI将用2个像素时钟周期捕获一个32位数据。以12位数据宽度为例,DCMI在第1个像素时钟捕获12位LSB(忽略D[13 :12]),存于DCMI_DR寄存器低16位字中低12位,高4位(D[15 :12)清零;第2像素时钟捕获的12位LSB则存于DCMI_DR高16位字的低12位,高4位(DCMI_DR的[31 : 28])清零。另外相机也必须配置为10/12/14位输出。具体情况则由应用决定。

3.小结

本文通过介绍STM32 DCMI支持的最大像素时钟频率,支持的图像分辨率及与帧率的关系,进而引出DCMI带宽与性能提升的注意事项。另外附带了DCMI图像大小的调整及10~14数据线的简介,为用户遇到相关问题时提供思路参考。完整内容请点击“阅读原文”下载原文档。

长按扫码关注公众号

更多资讯,尽在STM32

▽点击“阅读原文”,可下载原文档

原文标题:应用笔记 | STM32 DCMI 的带宽与性能介绍

文章出处:【微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

-

单片机

+关注

关注

6032文章

44521浏览量

633105 -

STM32

+关注

关注

2266文章

10873浏览量

354843

原文标题:应用笔记 | STM32 DCMI 的带宽与性能介绍

文章出处:【微信号:STM32_STM8_MCU,微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

应用笔记 | STM32 DCMI 的带宽与性能介绍

应用笔记 | STM32 DCMI 的带宽与性能介绍

评论