电子发烧友网报道(文/周凯扬)在半导体设计领域,IP公司拥有的各大优秀IP除了要经过客户的验证外,其实还有不少认证工作需要完成。比如在汽车领域,往往就需要通过ISO 26262的功能安全认证。而对于是否能经过生产制造认证,晶圆厂也准备了自己的一套标准或认证计划,比如台积电的TSMC9000计划。

台积电的IP认证

台积电从很早就开始和IP厂商达成合作,成立了台积电开放创新平台(OIP),该平台的关键组成之一就是IP联盟和TSMC9000 IP认证计划。该联盟将为半导体业界提供最大的流片生产认证且台积电专用的IP。IP联盟的成员会分配单独的客户经理,不仅可以访问台积电的技术数据用于设计IP,还可以获得台积电技术支持团队的专门支持。

至于早在2000年就开启的TSMC9000 IP认证计划,则是台积电为IP质量下限设定的一系列要求。IP合作伙伴必须提供数据,随后申请为其IP进行TSMC9000评估。评估项目包括DRC/LVS、数据一致性检验、ESD耐受性验证、设计余量验证等。

评估结果也会发布到TSMC的在线数据库,帮助客户对这一IP的可用性和风险性有一个了解。除了IP本身的质量外,TSMC9000还有额外的系统层级测试验证项目,从而确保整体的设计体验,且针对车规设计,台积电也准备了专门的TSMC9000A认证。

庞大的IP阵容

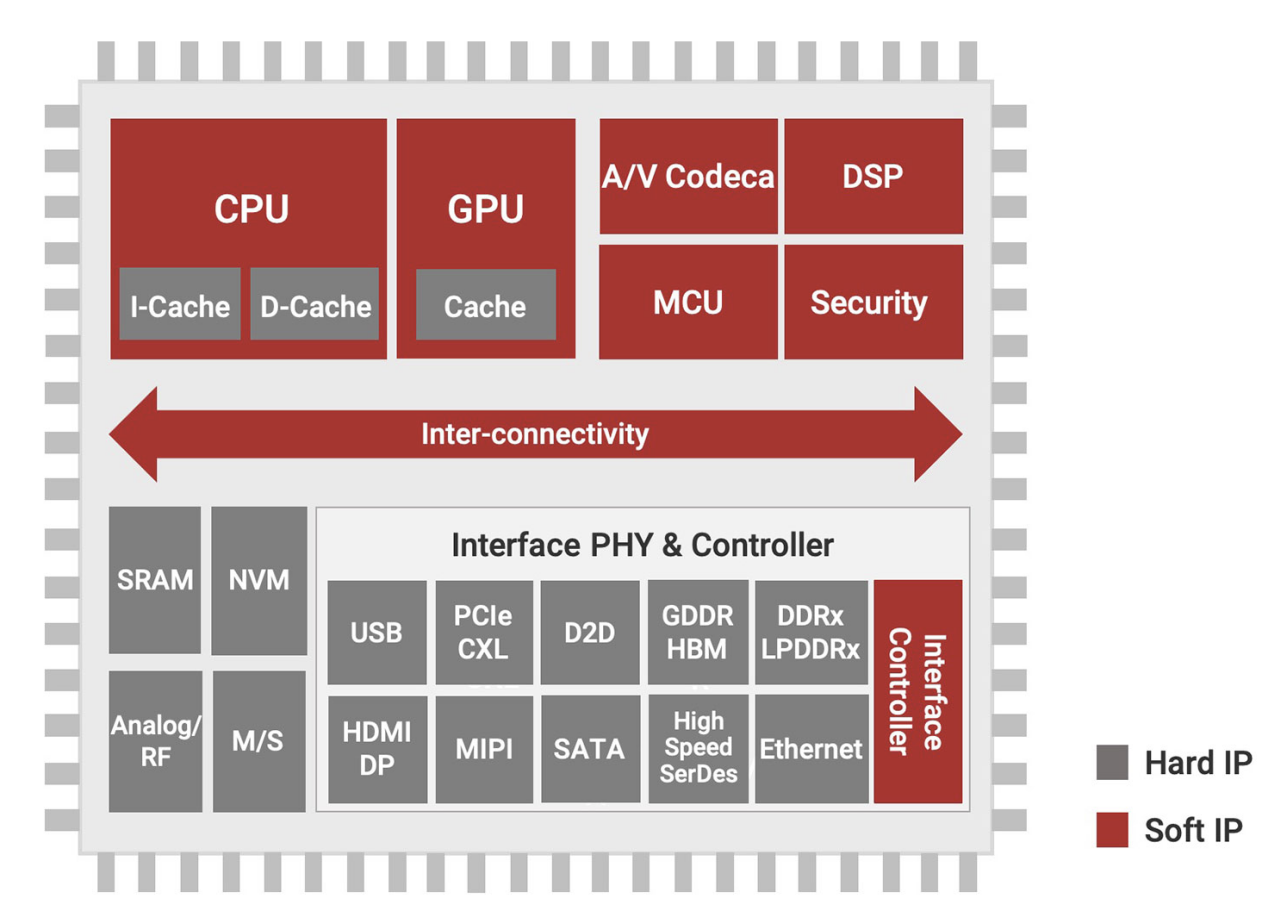

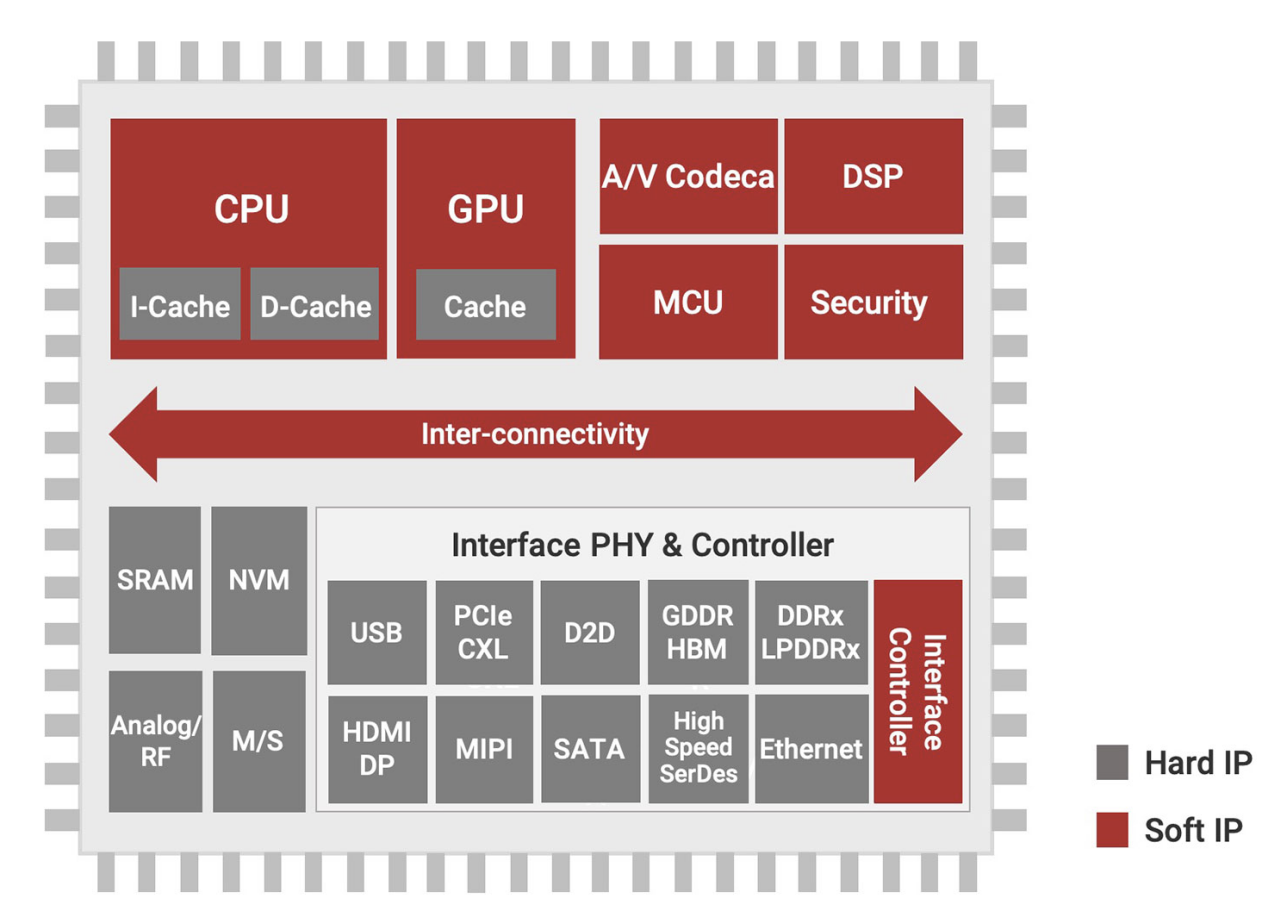

如今的TSMC9000在多年发展下来,已经拥有了极度完备的IP支持阵容。台积电也对这些IP做好了细致的分类,既有CPU、GPU、编解码器、DSP、MCU和互联之类的软IP,也有SRAM、HDMI、USB、以太网之类的硬IP。

现代SoC设计中的软硬IP划分 / 台积电

不少IP厂商将新IP正式投入商用供应时,往往都会先通过TSMC9000认证,然后公开这一消息,从而给到客户一个侧面的质量保证承诺。同时,台积电每年都会颁发年度IP合作伙伴奖,是否获得TSMC9000认证也是评选因素之一,此外还有客户反馈、流片次数、晶圆量和客户支持等。

就拿新思、Cadence等厂商来说,作为台积电的主要OIP合作伙伴,都会在TSMC9000上下大功夫,比如新思的DesignWare PVT、Cadence的Tensilica DSP IP等,都会针对台积电的最新工艺进行优化,从而通过TSMC9000的认证。

写在最后

可以看出,使得台积电成为芯片设计公司首选晶圆代工厂的原因,不仅仅只有其先进的制造工艺,还有它那成熟的OIP合作伙伴生态。早在2013年,就有39家厂商共9500个IP对台积电的各大工艺节点提供了支持,如今这个数量更是增加到了40多个IP厂商和49000多个IP,致使如今的厂商在开发新的IP时,也是优先考虑在台积电工艺节点上的流片可行性。在这样的IP合作生态和验证计划下,设计公司在选取IP时进行系统设计和制造上,也会更加放心。

台积电的IP认证

台积电从很早就开始和IP厂商达成合作,成立了台积电开放创新平台(OIP),该平台的关键组成之一就是IP联盟和TSMC9000 IP认证计划。该联盟将为半导体业界提供最大的流片生产认证且台积电专用的IP。IP联盟的成员会分配单独的客户经理,不仅可以访问台积电的技术数据用于设计IP,还可以获得台积电技术支持团队的专门支持。

至于早在2000年就开启的TSMC9000 IP认证计划,则是台积电为IP质量下限设定的一系列要求。IP合作伙伴必须提供数据,随后申请为其IP进行TSMC9000评估。评估项目包括DRC/LVS、数据一致性检验、ESD耐受性验证、设计余量验证等。

评估结果也会发布到TSMC的在线数据库,帮助客户对这一IP的可用性和风险性有一个了解。除了IP本身的质量外,TSMC9000还有额外的系统层级测试验证项目,从而确保整体的设计体验,且针对车规设计,台积电也准备了专门的TSMC9000A认证。

庞大的IP阵容

如今的TSMC9000在多年发展下来,已经拥有了极度完备的IP支持阵容。台积电也对这些IP做好了细致的分类,既有CPU、GPU、编解码器、DSP、MCU和互联之类的软IP,也有SRAM、HDMI、USB、以太网之类的硬IP。

现代SoC设计中的软硬IP划分 / 台积电

不少IP厂商将新IP正式投入商用供应时,往往都会先通过TSMC9000认证,然后公开这一消息,从而给到客户一个侧面的质量保证承诺。同时,台积电每年都会颁发年度IP合作伙伴奖,是否获得TSMC9000认证也是评选因素之一,此外还有客户反馈、流片次数、晶圆量和客户支持等。

就拿新思、Cadence等厂商来说,作为台积电的主要OIP合作伙伴,都会在TSMC9000上下大功夫,比如新思的DesignWare PVT、Cadence的Tensilica DSP IP等,都会针对台积电的最新工艺进行优化,从而通过TSMC9000的认证。

写在最后

可以看出,使得台积电成为芯片设计公司首选晶圆代工厂的原因,不仅仅只有其先进的制造工艺,还有它那成熟的OIP合作伙伴生态。早在2013年,就有39家厂商共9500个IP对台积电的各大工艺节点提供了支持,如今这个数量更是增加到了40多个IP厂商和49000多个IP,致使如今的厂商在开发新的IP时,也是优先考虑在台积电工艺节点上的流片可行性。在这样的IP合作生态和验证计划下,设计公司在选取IP时进行系统设计和制造上,也会更加放心。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

台积电

+关注

关注

44文章

5632浏览量

166419

发布评论请先 登录

相关推荐

OpenAI携手博通、台积电打造内部芯片

近日,据消息人士透露,OpenAI正在与博通和台积电展开合作,共同研发其首款内部芯片,旨在为其人工智能系统提供更强大的支持。 为应对基础设施需求的激增,OpenAI在芯片供应方面采取了

OpenAI携手博通台积电打造自主芯片

OpenAI正在与博通和台积电两大半导体巨头携手合作,共同打造其首款自主研发的“in-house”芯片,旨在为其人工智能系统提供更强大的算力

M31円星科技连续七年获颁「台积电OIP硅智财伙伴奖」,並發表ONFI5.1 I/O IP于台积电5奈米制程成功完成硅验证

M31的ONFI5.1 I/O IP在数据传输速度上的效能尤为突出,藉由台积电5奈米制程技术,该IP成功达到了3600MT/s的传输速率,已

Alphawave推出业界首款支持台积电CoWoS封装的3nm UCIe IP

的3nm Die-to-Die(D2D)多协议子系统IP。这一里程碑式的成果不仅标志着半导体互连技术的又一次飞跃,还通过深度融合台积电的Chip-on-Wafer-on-Substra

SK集团与台积电加强AI芯片合作

韩国SK集团与全球领先的半导体制造商台积电近日宣布加强在人工智能(AI)芯片领域的合作。据SK集团官方消息,集团会长崔泰源于6月6日亲自会见了台

新思科技与台积公司深化EDA与IP合作

新思科技近日与台积公司宣布,在先进工艺节点设计领域开展了广泛的EDA和IP合作。双方的合作成果已经成功应用于一系列人工智能、高性能计算和移动

Cadence与台积电深化合作创新,以推动系统和半导体设计转型

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)与台积电(TSMC)深化了双方的长期合作,官宣了一系列旨在加速设计的创新技术进展,包括从 3D-IC 和先进制程节点到设计

Marvell将与台积电合作2nm 以构建模块和基础IP

Marvell将与台积电合作2nm 以构建模块和基础IP 张忠谋于1987年成立的台湾积体电路制

十年新增四万个IP,台积电打造的IP合作生态

十年新增四万个IP,台积电打造的IP合作生态

评论