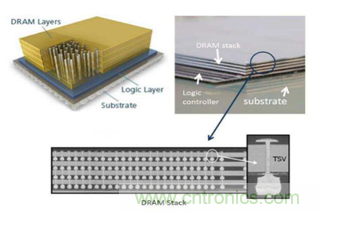

这篇文章简要介绍CEA-Leti发布用于Chiplet 3D系统的硅光Interposer工艺架构,包括硅光前端工艺 (FEOL)、TSV middle工艺、后端工艺 (BEOL) 和背面工艺。

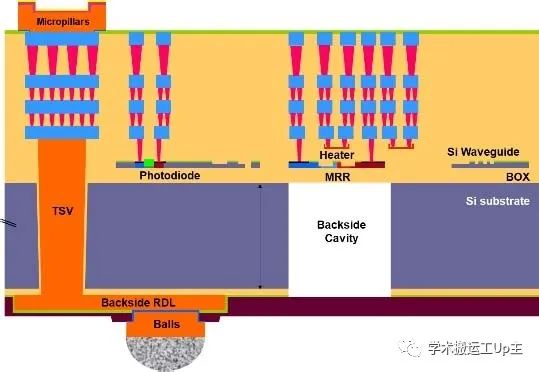

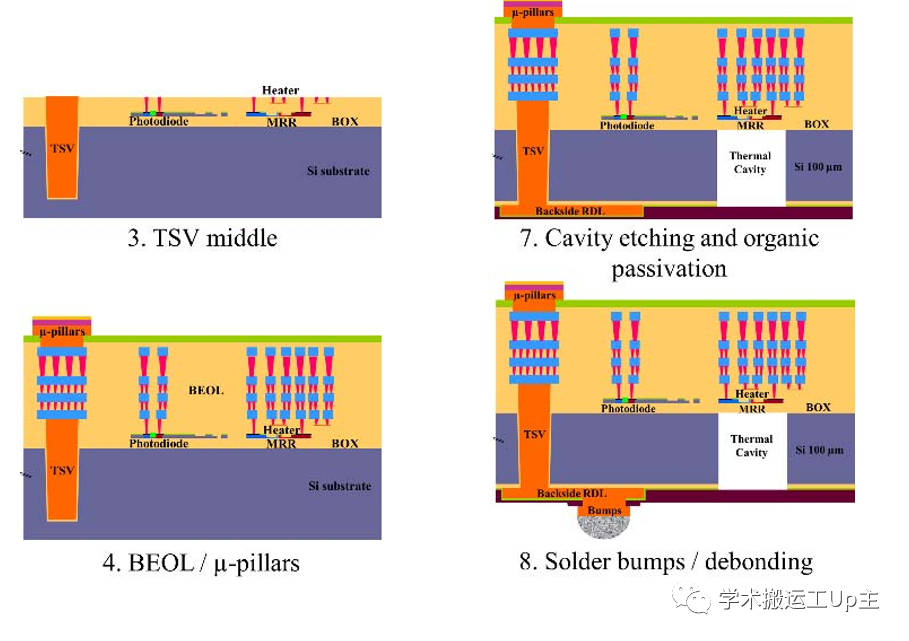

下图展示了Interposer的技术横截面,其中包括μ-pillars、BEOL层、有源光子器件、背面空腔、TSV、RDL 和焊球。

1. 硅光前端工艺

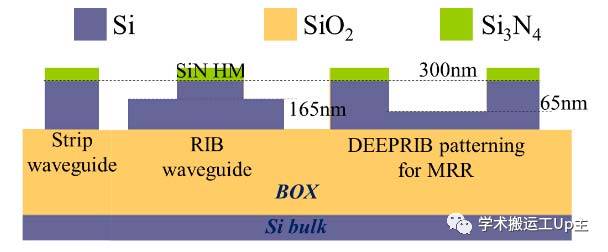

硅光子器件是在 CEA-LETI 的 200mm 工艺平台在绝缘体上硅 (SOI) 晶圆上制造的。该晶圆有 800nm 厚的埋层氧化物 (BOX)/顶部具有 310nm 厚的硅层。制造从各种注入步骤开始,主要用于定义 MRR 的 PN 和 PIN 结以及 MRR 和光电二极管的电气接触。然后使用 Si3N4 硬掩模对硅光波导进行图案化。采用3级DUV光刻(193nm和248nm)定义3种硅的厚度,获得波导走线和单偏振光栅耦合器(SPGC),共有300nm厚波导和165nm厚Rib-slab波导,以及具有300nm厚环形波导和65nm 厚的深刻蚀波导。下图展示了硅光子器件的不同硅厚度。

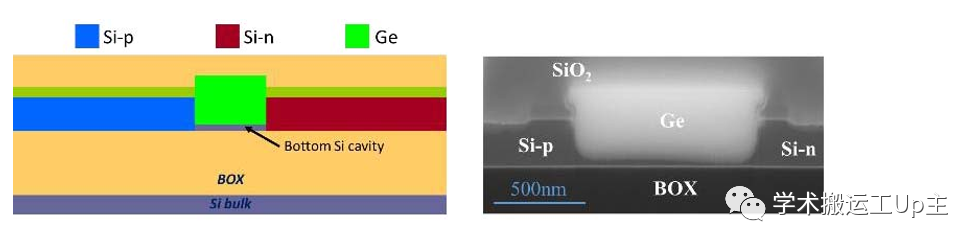

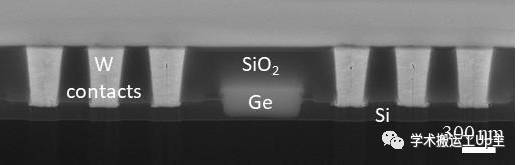

在硅图案化之后,在 MRR 的slab层中进行了额外的离子注入以增强调制性能。在对硅结构进行高密度等离子体化学气相沉积 (HDP-CVD) SiO2 包层并平坦化之后,使用 SiO2/Si3N4 电介质叠层作为硬掩模,通过在硅中形成空腔图案来制造butt 耦合的 SiGeSi 光电探测器。对硅中的空腔进行部分蚀刻并进行表面处理后,通过使用两步减压化学气相沉积 (RPCVD) 工艺进行选择性外延,在硅上生长锗。通过 CMP 去除多余的Ge并停在 SiO2 顶面。然后沉积一层 SiO2 以覆盖 Ge 光电探测器。下面显示了所得 Ge 光电探测器的示意性横截面,并显示了 SiO2 覆盖后 Ge 光电探测器的 FIB 横截面图像。

为了增强有源光子器件上的电接触,在定义为 MRR 和Ge PD的电接触的高掺杂硅区域的表面进行硅化(Silicidation)。将电介质叠层蚀刻至掺杂硅,并通过在硅上沉积薄的 Ti/TiN 叠层并随后进行热退火来形成 TiSi2 硅化物。湿法去除未反应的 Ti/TiN 后,进行第二次热退火以稳定 20nm 硅化物层。然后在 300 nm 厚的硅光子结构上沉积并平坦化 600nm 厚的厚 SiO2 层。

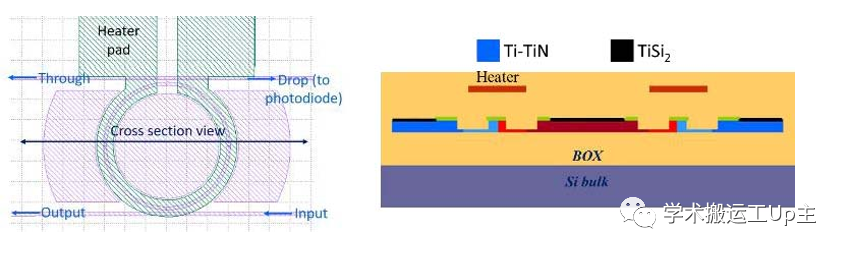

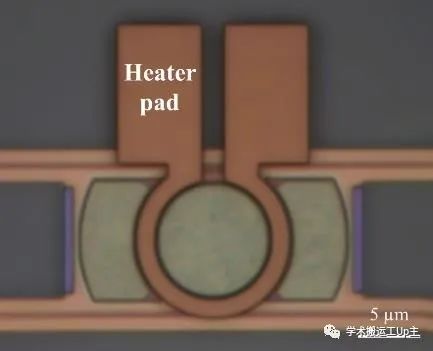

MRR 谐振频率通过使用 MRR 波导顶部的加热器heater进行控制,如下面的 MRR 设计和示意性横截面所示。

通过沉积 Ti 10nm/TiN 100nm 叠层来制造heater,并通过干法蚀刻进行图案化。下图显示了 MRR 顶部heater的显微镜图片。

加热器heater由 300nm 厚的平坦化 SiO2 层封装。首先,对加热器顶部 300nm 厚的 SiO2 层中的加热器触点进行干法蚀刻开始金属触点。然后,通过同时对 MRR 和Ge PD接触点进行处理,将电介质叠层蚀刻至硅光子器件顶部的 TiSi2 硅化物层。一步沉积钨以填充heater、PD 和 MRR 触点。通过 CMP 去除多余的 W。带有 W 触点的 Ge PD的横截面图如下所示。

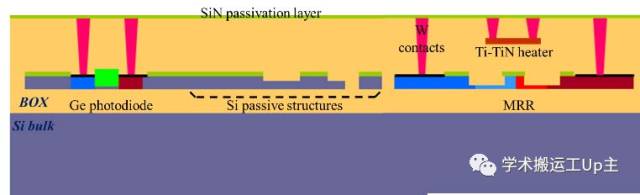

在 TSV 工艺之前沉积 60nm PECVD SiN 钝化层。下面给出了接触定义和钝化后完整光子集成电路 (PIC) 的示意性横截面。

2.TSV middle工艺

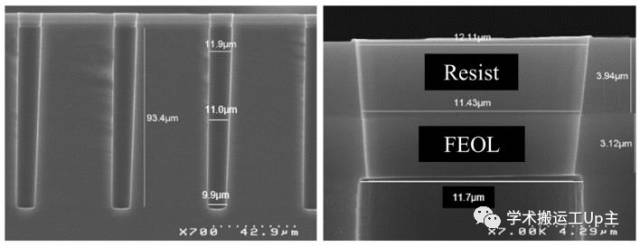

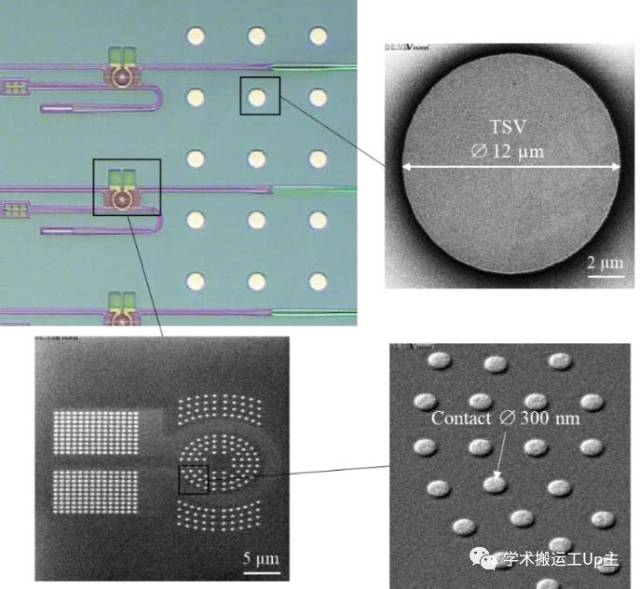

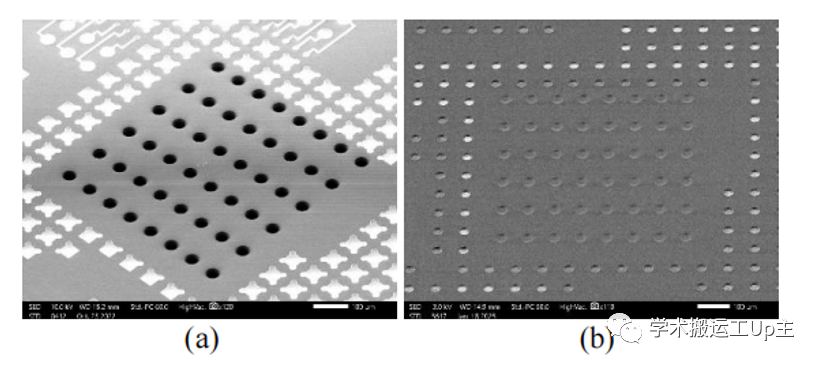

Interposer选择的TSV工艺是直径为12μm、厚度为100μm的TSV middle工艺。TSV蚀刻分两步进行。首先,采用反应离子刻蚀(RIE)工艺刻蚀介质光子叠层(SiN/SiO2)。其次,使用Bosch工艺的深反应离子蚀刻(DRIE)通过图案化光刻胶对硅进行蚀刻,如下所示。

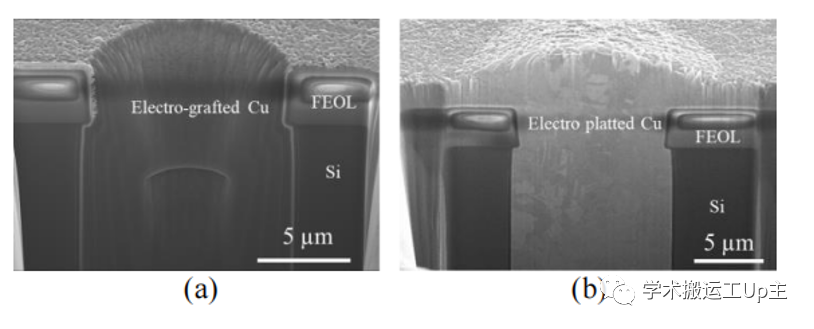

TSV 隔离是通过 300nm 低于大气压化学气相沉积 (SACVD) 和 100nm 等离子体增强 CVD (PECVD) 氧化硅实现的。然后沉积阻挡层和种子层。沉积顺序包括 Ti PVD 粘附层、TiN CVD 阻挡层和 Cu PVD 种子层。由于 Cu PVD 工艺的共形性受到限制,因此镀了额外的电接枝铜层,以确保穿过 TSV 的籽晶连续性,如下所示(a)。TSV 填充采用 Cu 电化学沉积 (ECD) 进行,并采用优化的自下而上填充配方。这允许用低于 3μm 的剩余铜表面厚度填充 TSV,如下所示(b)。

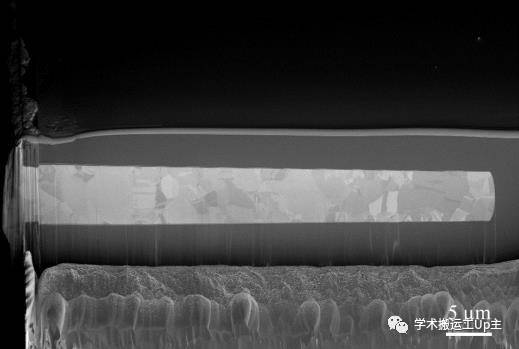

然后,TSV 在 400°C 下以特定的热曲线进行退火,以最大程度地减少如下所示的 Cu 应力, 如下图热退火后的图像。

最后的工艺是化学机械抛光(CMP)的两步。第一步专用于在 TSV 隔离氧化硅层上选择性蚀刻停止的 Cu 和阻挡层。第二步致力于在 300nm 直径的 W 触点上刻蚀停止的电介质 SiO2/SiN 层。此步骤具有挑战性,主要是因为 CMP 工艺期间存在 TSV Cu 开口,如下所示。

3. BEOL工艺

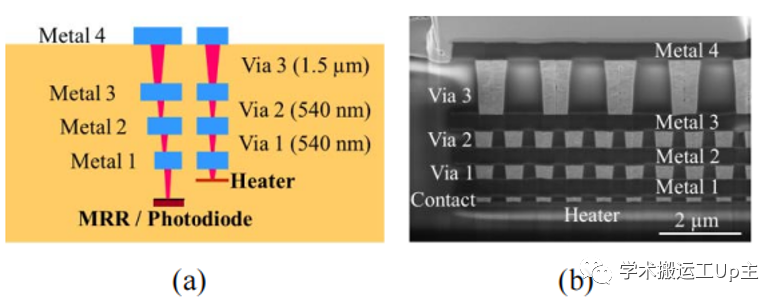

BEOL 叠层由 4 层金属布线组成。如图a所示,前3层相同,由PVD沉积的540nm Ti-TiN/AlCu/Ti-TiN多层金属叠层制成,并由PECVD SiO2中间层隔开。每个介电层均采用 CMP 工艺进行平坦化。在 SiO2 金属间层中通过 RIE 形成 300nm 宽度的方形接触图案,填充 W 并平坦化。第四金属层的厚度与第 3 个金属层的厚度相同,但通孔 3 的层间厚度增加到 1.5 μm,用于射频功能目的。因此,接触尺寸也增加到 750 nm 宽的方形接触。完整 BEOL 的横截面 FIB-SEM 图像显示在图b中。

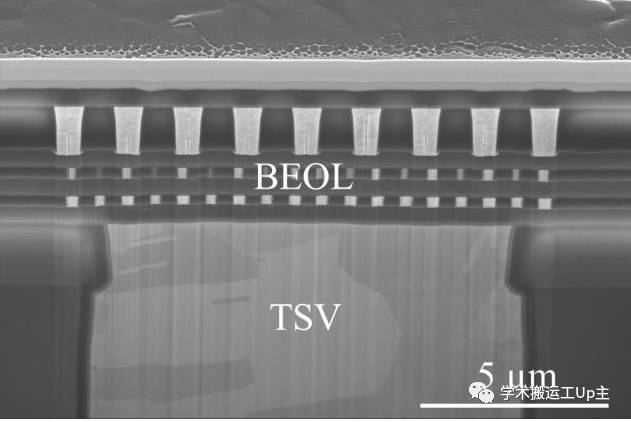

最终钝化采用平坦化 500nm SiO2 PECVD 和 600nm SiN PECVD 进行。Pad open采用正光刻胶完成,电介质叠层采用 RIE 工艺蚀刻,下图中FIB SEM显示TSV middle工艺及BEOL的4层金属线。

最终钝化采用平坦化 500nm SiO2 PECVD 和 600nm SiN PECVD 进行。Pad open采用正光刻胶完成,电介质叠层采用 RIE 工艺蚀刻,下图中FIB SEM显示TSV middle工艺及BEOL的4层金属线。

4.μ-pillars工艺

最后一个晶圆正面的工艺是μ-pillars工艺。首先,通过PVD分别沉积100nm和400nm的Ti/Cu种子层。光刻采用 12μm 厚的正光刻胶、临界尺寸 (CD) 为 20μm、节距为 20μm 来实现。μ柱通过电镀5μm Cu、2μm Ni和0.3μm Au来生长。然后strip光刻胶并通过湿法蚀刻去除种子层。

5. 背面工艺

1)晶圆减薄、Cu钉显露

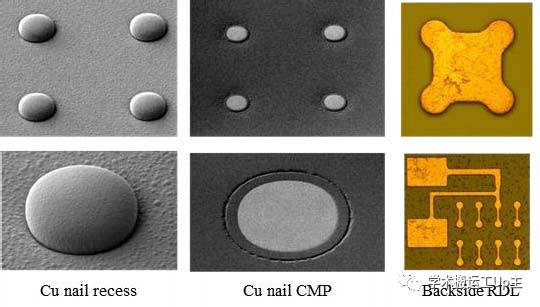

为了处理晶圆背面,使用 20μm 厚的粘合剂聚合物在 725μm 体硅carrier上进行临时键合。通过粗磨和精磨来实现Interposer晶圆的减薄。湿法硅应力释放最终将厚度降低至(110±1)μm。通过红外干涉测量法监测 TSV 上方的残余硅厚度。采用 SF6 RIE 工艺显露铜钉,厚度范围为 3 至 6μm。采用PECVD沉积2μm厚的低温氧化硅。最后,进行 CMP 工艺以去除电介质并打开 TSV 的 Cu。

2)背面RDL、腔体蚀刻和钝化

在正光刻胶 RDL 线/间距 10/10 μm 光刻之前,通过 PVD 工艺沉积由 100nm Ti 和 200nm Cu 组成的种子层。经过 O2 等离子体处理后,通过 ECD 电镀 3μm 厚的 Cu,并对种子层进行湿法蚀刻,如下所示。

通过 PECVD 沉积 100nm 的低温 SiN 层,以避免钝化中的 Cu 扩散并在等离子体步骤中对其进行保护。然后在环形谐振器上方从体硅到 BOX 蚀刻直径为 40μm 的空腔。使用掩模对准光刻技术在 RDL 上形成 8μm 厚的低温固化 (LTC) 钝化聚合物图案,并在 N2 气氛下在 230°C 下退火 3 小时。需开发专用旋涂工艺来覆盖空腔。下图中的SEM显示旋涂有机钝化层的RDL和空腔前后对比图(a旋涂前/b旋涂后)

3) 焊锡凸块和脱粘(Solder bumps & debonding)

首先,在LTC钝化层上沉积Ti 200nm/Cu 400nm种子层。旋涂正光刻胶以达到40μm的厚度。光刻是通过具有40μm凸块直径和40μm间距的掩模对准器完成的。凸块通过 5μm Cu、2μm Ni 和 17μm SnAg 的 ECD 生长。然后strip 光刻胶并蚀刻种子层。

最后将晶圆在切割胶带上裂解开,进行清洁以去除粘合剂残留物,并为封装过程做好准备。

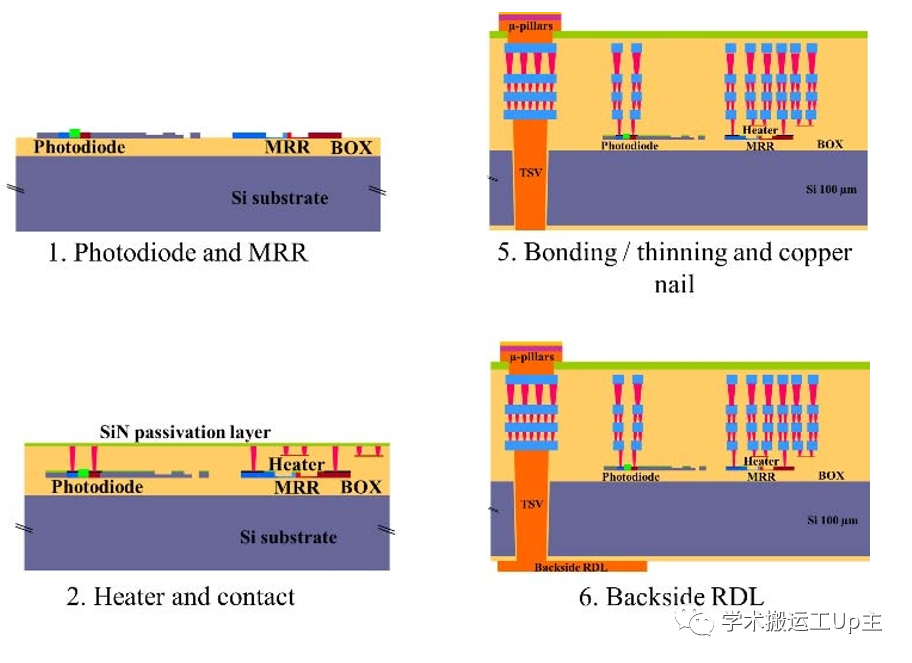

**下图显示CEA-LEti的Interposer工艺架构流程图

审核编辑:刘清

-

耦合器

+关注

关注

8文章

725浏览量

59686 -

光刻机

+关注

关注

31文章

1150浏览量

47376 -

硅光子技术

+关注

关注

0文章

15浏览量

6247 -

TSV封装

+关注

关注

0文章

12浏览量

2367 -

chiplet

+关注

关注

6文章

431浏览量

12584

原文标题:CEA-Leti 硅光工艺集成-Chiplet/Interposer

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

制造业革命——3D打印的主流工艺盘点

3D扫描的结构光

3D混合制造技术介绍

芯片的3D化历程

使用结构光的3D扫描介绍

3D封装与硅通孔(TSV)工艺技术

用于Chiplet 3D系统的硅光Interposer工艺架构介绍

用于Chiplet 3D系统的硅光Interposer工艺架构介绍

评论