寄生电路是一种隐蔽性的电路设计的缺陷,按正常的电路分析是不容易发现的 ,是在某种特定的情况下才会出现 ,发生意外接通的电路 。

时常是在某元器件的非正常状态 ,电路感谢结束后的运行中 ,在保护 原件动作状态的短暂时间里,才有可能出现并消失 。查找起来既费时又不方便 。

寄生电路容易导致维修人员在故障时发生误判和误处理,甚至扩大为事故 。

电友评论:见过有一种几个接触器公用一个远程旋钮,结果一个接触器远程吸合,火线的电顺着那个接触器的本地回路又走回去了,导致其他接触器吸合了都断开不了了。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

接触器

+关注

关注

63文章

1202浏览量

64800 -

状态机

+关注

关注

2文章

492浏览量

27694

原文标题:什么是寄生电路 ,你知道吗?

文章出处:【微信号:电气自动化控制网,微信公众号:电气自动化控制网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

智能功率开关:在汽车环境中应用

请参阅ISO 7637 定义)1. 虚地1-1 低端IPSs如果一个低边开关和地的连接断开,上面的负载将不会被启动。图1显示在这种情况下,IPS 内寄生的电路被启动。串联电阻Rin 用来限制流入微处理器的电流。该电阻阻值必须足够小(约1k),小到它上面的电压降可以忽略,以

发表于 10-06 14:49

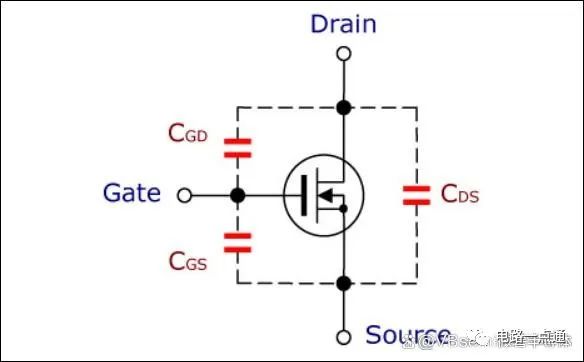

寄生电路的效应:Latch-Up(锁定)

Latch-Up(锁定)是CMOS存在一种寄生电路的效应,它会导致VDD和VSS短路,使得晶片损毁,或者至少系统因电源关闭而停摆。这种效应是早期CMOS技术不能被接受的重要原因之一。在制造更新和充分

发表于 08-23 06:06

全新Calibre xACT产品可满足先进工艺广泛的寄生电路参数提取需求

Mentor Graphics 公司(纳斯达克代码:MENT)今天宣布推出全新 Calibre® xACT™ 寄生电路参数提取平台,该平台可满足包括 14nm FinFET 在内广泛的模拟和数字电路参数提取需求,同时最大限度地减

发表于 04-24 13:42

•972次阅读

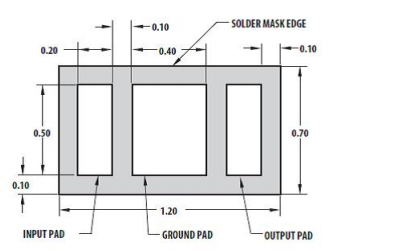

射频VMMK器件通过降低寄生电感和电容提高性能

VMMK 器件晶圆等级和芯片封装工艺 如图1所示,VMMK器件由于安华高特有的晶圆空腔工艺降低了损耗和常见的射频表贴封装带来的寄生电路参数。通过消除焊接和封装引脚之间的寄生电感和电容,在芯片和封装间

发表于 11-22 20:06

•847次阅读

射频VMMK器件通过降低寄生电感和电容提高性能解析

如图1所示,VMMK器件由于安华高特有的晶圆空腔工艺降低了损耗和常见的射频表贴封装带来的寄生电路参数。通过消除焊接和封装引脚之间的寄生电感和电容,在芯片和封装间形成了一个低损耗和低阻抗的信号通道。

发表于 05-07 14:59

•2374次阅读

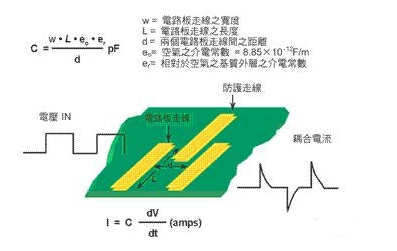

什么是寄生电感_PCB寄生电容和电感计算

寄生电感一半是在PCB过孔设计所要考虑的。在高速数字电路的设计中,过孔的寄生电感带来的危害往往大于寄生电容的影响。它的寄生串联电感会削弱旁路

发表于 10-11 10:36

•2.1w次阅读

射频VMMK器件如何通过降低寄生电感和电容提高性能

如图1所示,VMMK器件由于安华高特有的晶圆空腔工艺降低了损耗和常见的射频表贴封装带来的寄生电路参数。通过消除焊接和封装引脚之间的寄生电感和电容,在芯片和封装间形成了一个低损耗和低阻抗的信号通道。在元件之上的空腔具有低介电常数

发表于 08-21 18:50

•0次下载

如何减少导线的寄生电感?

如何减少导线的寄生电感? 引言: 随着电子设备的广泛应用,对于高速数据传输和高频信号的传输要求也越来越高。然而电学特性的限制使得对导线的寄生电感逐渐成为制约高频电路性能的瓶颈之一。降低寄生

什么是寄生电路?

什么是寄生电路?

评论