1 后摩尔时代,先进封装成为提升芯片性能重要解法

1.1 摩尔定律放缓,先进封装日益成为提升芯片性能重要手段

随着摩尔定律放缓,芯片特征尺寸接近物理极限,先进封装成为提升芯片性 能,延续摩尔定律的重要手段。先进封装是指处于前沿的封装形式和技术,通过 优化连接、在同一个封装内集成不同材料、线宽的半导体集成电路和器件等方式, 提升集成电路的连接密度和集成度。当前全球芯片制程工艺已进入 3-5nm 区间, 接近物理极限,先进制程工艺芯片的设计难度、工艺复杂度和开发成本大幅增加, 摩尔定律逐渐失效,半导体行业进入“后摩尔时代”。前道制程工艺发展受限,但 随着 AI 等新兴应用场景快速发展,芯片性能要求日益提高,越来越多集成电路 企业转向后道封装工艺寻求先进技术方案,以确保产品性能的持续提升。先进封 装技术应运而生,在“后摩尔时代”逐步发展为推动芯片性能提升的主要研发方向。先进封装有多种分类标准,是否有焊线或光刻工序是其中一种区分方式。传 统封装不涉及光刻工序,切割后的晶圆通过焊线工艺实现芯片与引线框架的电性 连接,从而完成芯片内外部的连通。先进封装主要利用光刻工序实现线路重排 (RDL)、凸块制作(Bumping)及三维硅通孔(TSV)等工艺技术,涉及涂胶、曝 光、显影、电镀、去胶、蚀刻等工序。

1.2 先进封装份额占比提升,2.5D/3D 封装增速领先先进封装

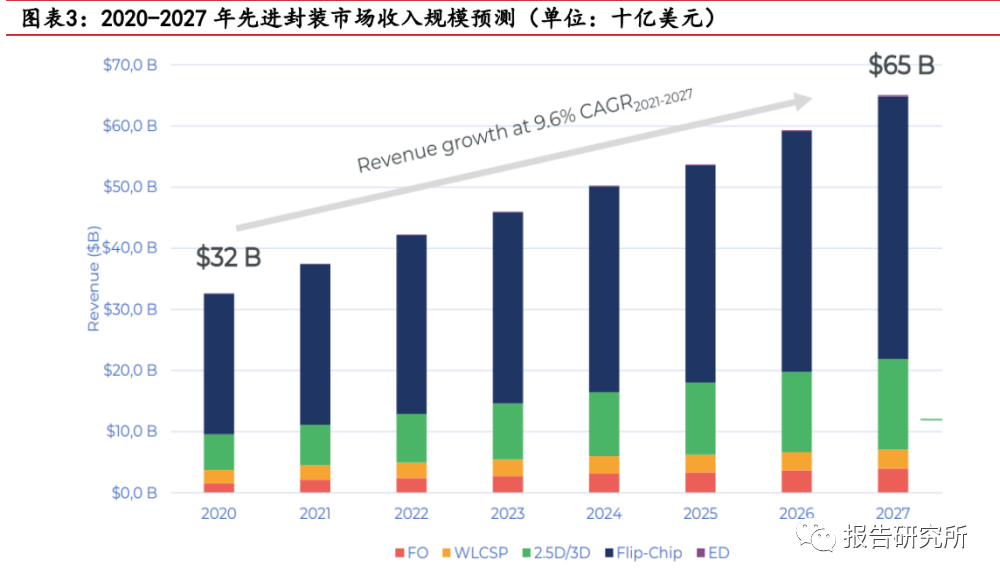

AI 带动先进封装需求。TrendForce 报告指出,聊天机器人等生成式 AI 应用 爆发式增长,带动 2023 年 AI 服务器开发大幅扩张。这种对高端 AI 服务器的依 赖,需要使用高端 AI 芯片,这不仅将拉动 2023~2024 年 HBM 的需求,而且预计 还将在 2024 年带动先进封装产能增长 30~40%。先进封装增速高于整体封装,2.5D/3D 封装增速居先进封装之首。根据 Yole, 2021 年,先进封装市场规模约 375 亿美元,占整体封装市场规模的 44%,预计到 2027 年将提升至占比 53%,约 650 亿美元,CAGR21-27为 9.6%,高于整体封装市场 规模 CAGR21-27 6.3%。先进封装中的 2.5D/3D 封装多应用于(x)PU, ASIC, FPGA, 3D NAND, HBM, CIS 等,受数据中心、高性能计算、自动驾驶等应用的驱动,2.5D/3D 封装市场收入规模 CAGR21-27高达 14%,在先进封装多个细分领域中位列第一。

1.3 先进封装处于晶圆制造与封测的交叉区域

先进封装处于晶圆制造与封测制程中的交叉区域,涉及 IDM、晶圆代工、封 测厂商。先进封装要求在晶圆划片前融入封装工艺步骤,具体包括应用晶圆研磨 薄化、重布线(RDL)、凸块制作(Bumping)及硅通孔(TSV)等工艺技术,涉及 与晶圆制造相似的光刻、显影、刻蚀、剥离等工序步骤,从而使得晶圆制造与封 测前后道制程中出现中道交叉区域。前后道大厂争先布局先进封装,竞争格局较为集中。后摩尔时代,先进制程 成本快速提升,一些晶圆代工大厂发展重心正在从过去追求更先进纳米制程,转 向封装技术的创新。诸如台积电、英特尔、三星、联电等芯片制造厂商纷纷跨足 封装领域。先进封装竞争格局较为集中,全球主要的 6 家厂商,包括 2 家 IDM 厂 商(英特尔、三星),一家代工厂商(台积电),以及全球排名前三的封测厂商(日 月光、Amkor、JCET),共处理了超过 80%的先进封装晶圆。

2 TSV:硅通孔,先进封装关键技术

2.1 TSV:硅通孔技术,芯片垂直堆叠互连的关键技术

TSV(Through Silicon Via),硅通孔技术,是通过硅通道垂直穿过组成堆 栈的不同芯片或不同层实现不同功能芯片集成的先进封装技术。TSV 主要通过铜 等导电物质的填充完成硅通孔的垂直电气互连,减小信号延迟,降低电容、电感, 实现芯片的低功耗、高速通信,增加带宽和实现器件集成的小型化需求。此前,芯片之间的大多数连接都是水平的,TSV 的诞生让垂直堆叠多个芯片 成为可能。Wire bonding(引线键合)和 Flip-Chip(倒装焊)的 Bumping(凸 点)提供了芯片对外部的电互连,RDL(再布线)提供了芯片内部水平方向的电互 连,TSV 则提供了硅片内部垂直方向的电互连。

2.2 TSV 三种主要应用方向:背面连接、2.5D 封装、3D 封装

TSV 有多种用途,可大致分为 3 种:(a) 垂直的背面连接,无芯片堆叠,如“简单的背面连接”。TSV 位于有源晶 粒(active die)中,用于连接至晶圆背面的焊盘(bond pad);(b) 2.5D 封装。晶粒(die)连接至硅中介层(interposer),TSV 在中介层 中;(c) 3D 封装。TSV 位于有源晶粒中,用于实现芯片堆叠。

(a)TSV 作为简单背面连接:用于 CIS 和锗化硅(SiGe)功率放大器

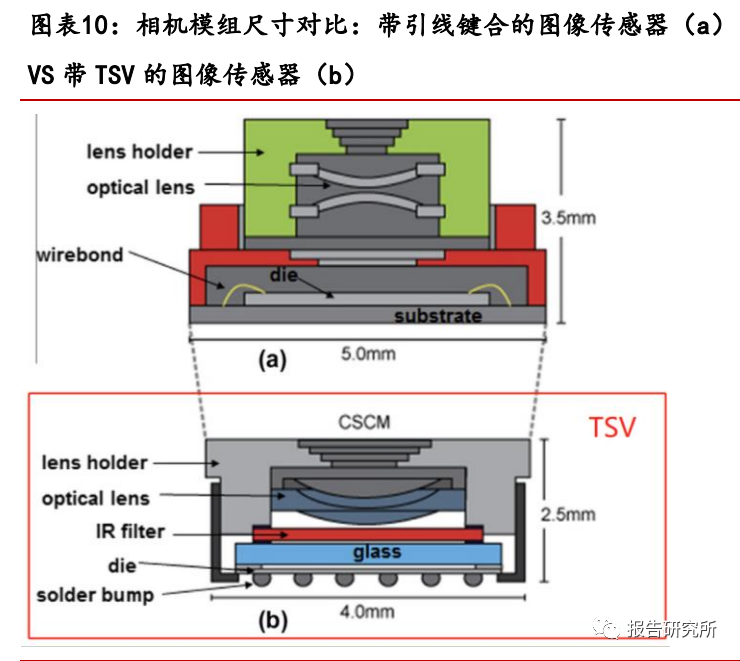

TSV 三种主要应用方式中,简单的背面连接结构是技术难度最低的,也是 TSV 技术首次大规模投入生产时的应用方向,如 CMOS 图像传感器(CIS)、SiGe 功率 放大器两个产品就应用了 TSV 技术。将 TSV 用于 CMOS 图像传感器有许多优点:1)使用 TSV 代替引线键合可以减小相机模组的尺寸。2)简化了图像传感器的晶圆级封装(WLP)。WLP 工艺的第一步 是将玻璃晶圆附着到图像传感器的正面,防止光刻胶(抗蚀剂)微透镜在组装过程 中受到损坏和污染,然而安装好玻璃晶圆后会使从晶圆正面到焊盘的连接途径受 阻,TSV 通过简化晶圆级封装,对此问题提供了简易的解决方法。

(b)TSV 应用于 2.5D 封装:FPGA

与简单的背面连接相比,2.5D 先进封装的硅中介层需要更小的 TSV 间距 (≤50 μm),因此需要更先进的 TSV 工艺。现场可编程门阵列(Field Programmable Gate Array,FPGA)器件是最早 使用硅中介层的产品之一:硅中间层可以使芯片间密切连接,整合后的结构看起 来像单个大尺寸的 FPGA 芯片,解决了早期直接构建单个大尺寸 FPGA 芯片的技术 难题。

(c)TSV 应用于 3D 封装:存储器堆叠

储器堆叠是首批应用 3D 堆叠 TSV 结构的产品之一,和 2.5D 封装中硅中阶层 对 TSV 间距的需求相似,但实际应用中难度更高,例如宽 I/O DRAM 设备。使用宽 I/O DRAM 和芯片堆叠的优势包括封装高度降低40%,功耗降低50%, 带宽增加 6 倍。

2.3 国内封测厂 TSV 布局情况:多家头部厂商已有布局

内资封测厂商向 TSV 等先进封装领域突破。全球半导体产业经历二次产业转 移,目前处于第三次产业转移的进程之中,作为半导体领域壁垒相对较低的领域, 封测产业目前主要转移至亚洲区域,主要包括中国大陆、中国台湾、东南亚等。封测是中国大陆集成电路发展最为完善的板块,技术能力与国际先进水平比较接 近,我国封测市场已形成内资企业为主的竞争格局。中国大陆封测市场目前主要 以传统封装业务为主,经过多年的技术创新和市场积累,内资企业产品已由 DIP、 SOP、SOT、QFP 等产品向 QFN/DFN、BGA、CSP、FC、TSV、LGA、WLP 等技术更先进 的产品发展,并且在 WLCSP、FC、BGA 和 TSV 等技术上取得较为明显的突破,产 量与规模不断提升,逐步缩小与外资厂商之间的技术差距,极大地带动我国封装 测试行业的发展。

我国头部封测企业,如长电科技、通富微电、华天科技、晶方科技已有采用 TSV技术封装的产品批量出货。2.5D/3D封装所需的晶圆内部的加工如TSV加工, 硅转接板加工等工序属于晶圆厂擅长制程,而晶圆,裸芯片(Die)之间的高密度 互联和堆叠,以及和基板,接点的互联技术属于芯片后道成品制造环节的优势。应用于 CoWoS 等 2.5D/3D 先进封装中的 TSV 技术对深宽比等有更高要求,需要用 到诸多前道设备,仍多由晶圆厂来完成。国内封测厂则在先进封装平台、CIS 封 装等领域对 TSV 技术有所布局。长电科技的 XDFOI技术平台有 TSV less 和 TSV 方案。通富微电 2021 年在高性能计算领域建成了 2.5D/3D 封装平台(VISionS) 及超大尺寸 FCBGA 研发平台,并完成高层数再布线技术开发,可为客户提供晶圆 级和基板级 Chiplet 封测解决方案;在存储器领域,多层堆叠 NAND Flash 及 LPDDR 封装实现稳定量产,并在国内首家完成基于 TSV 技术的 3DS DRAM 封装开 发。华天科技工业级 12 吋 TSV-CIS 产品已实现量产。晶方科技应用晶圆级硅通 孔(TSV)封装技术,聚焦以影像传感芯片为代表的智能传感器市场,封装的产品 主要包括 CIS 芯片、TOF 芯片、生物身份识别芯片、MEMS 芯片等,应用于智能手 机、安防监控数码、汽车电子等市场领域。

3 TSV 制造流程及所需设备

3.1 TSV 制造流程

-

芯片

+关注

关注

457文章

51345浏览量

428237 -

摩尔定律

+关注

关注

4文章

637浏览量

79276 -

封装

+关注

关注

127文章

8033浏览量

143534 -

先进封装

+关注

关注

2文章

433浏览量

290

原文标题:电子行业TSV研究框架:先进封装关键技术

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

先进封装技术-19 HBM与3D封装仿真

先进封装技术-17硅桥技术(下)

先进封装技术-16硅桥技术(上)

先进封装的核心概念、技术和发展趋势

先进封装技术-7扇出型板级封装(FOPLP)

先进封装技术- 6扇出型晶圆级封装(FOWLP)

电子行业TSV研究框架:先进封装关键技术

电子行业TSV研究框架:先进封装关键技术

评论