变量的赋值

在转换中执行赋值时,所使用的值有明显的区别。在下面的表达式中

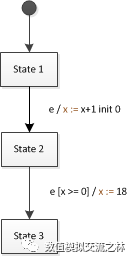

蓝色部分表示引发事件(也就是常说的e)时的值,绿色部分表示执行所有激活链后将更新的值。对于以下状态图:

当处于状态 1 并引发事件 e 时,执行将按如下方式发生:

- 转到状态 2,更新 x 的未来值。

- 检查优先级为 1 的转换,x 仍等于 0;无法进行过渡。

- 检查优先级为 2 的转换,该转换为空且始终为 true;可以进行转换,转到状态 4。

- 激活链结束,x 的未来值成为它的实际值,所以 x 的值变成 1,我们停留在状态 4。

感兴趣的小伙伴可以思考一下为什么是状态4而不是状态3

赋值更新激活链末尾的变量或离散输出的值。因此,当相同的值被分配两次时,就会出现问题,我们应该使用哪一个?

x 的值应该是 1 还是值 18?为避免状态图执行的歧义,禁止对激活链中的变量进行多次更新。为了打破链条,您必须为其中一个转换添加一个触发器:

这样,状态 2 和状态 3 之间的转换就不会直接进行;在重新更新变量 X 之前,必须在状态 2 中引发事件 E。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

转换器

+关注

关注

27文章

8703浏览量

147175 -

信号处理器

+关注

关注

1文章

254浏览量

25275 -

触发器

+关注

关注

14文章

2000浏览量

61156 -

有限状态机

+关注

关注

0文章

52浏览量

10331 -

AMESIM

+关注

关注

1文章

15浏览量

11732

发布评论请先 登录

相关推荐

什么是有限状态机呢

在嵌入式,机器人领域,由于多的复杂逻辑状态,我们编写程序的时候不得不考虑很多种情况,容易造成功能间的冲突。有限状态机(finite-state machine),简称状态机,是一种表示

发表于 12-20 06:51

基于VHDL的MTM总线主模块有限状态机设计

为了能够更简洁严谨地描述MTM总线的主模块有限状态机的状态转换,同时减少FPGA芯片功耗,提高系统稳定性,文中在分析MTM总线结构和主模块有限状态机模型的基础上,基于VHDL语言采

发表于 05-29 15:39

•20次下载

有限状态机的建模与优化设计

本文提出一种优秀 、高效的 Verilog HDL 描述方式来进行有限状态机设计 介绍了 有限状态机的建模原则 并通过一个可综合的实例 验证了 该方法设计的

发表于 03-22 15:19

•1次下载

VHDL有限状态机设计-ST

EDA的有限状态机,广义而言是指只要涉及触发器的电路,无论电路大小都可以归结为状态机。有限状态机设计在学习EDA时是很重要的一章。

发表于 06-08 16:46

•3次下载

初学者对有限状态机(FSM)的设计的认识

有限状态机(FSM)是一种常见的电路,由时序电路和组合电路组成。设计有限状态机的第一步是确定采用Moore状态机还是采用Mealy

发表于 02-11 13:51

•4304次阅读

如何使用FPGA实现序列检测有限状态机

有限状态机是绝大部分控制电路的核心结构, 是表示有限个状态以及在这些状态之间转移和动作等行为的数学模型。有限状态机是指输出取决于过去输入部分

发表于 11-04 17:17

•12次下载

有限状态机设计是HDL Designer Series的关键应用

有限状态机的设计是HDL Designer Series™工具的关键应用。 尽可能地对于设计人员编写导致状态机性能不佳的VHDL,可以使用HDL Designer用于生成VHDL的Series™工具

发表于 04-08 10:05

•6次下载

基于事件驱动的有限状态机介绍

一、介绍 EFSM(event finite state machine,事件驱动型有限状态机),是一个基于事件驱动的有限状态机,主要应用于嵌入式设备的软件系统中。 EFSM的设计

基于事件驱动的有限状态机介绍

EFSM(event finite state machine,事件驱动型有限状态机),是一个基于事件驱动的有限状态机,主要应用于嵌入式设备的软件系统中。

一个基于事件驱动的有限状态机

EFSM(event finite state machine,事件驱动型有限状态机),是一个基于事件驱动的有限状态机,主要应用于嵌入式设备的软件系统中。 EFSM的设计原则是:简单!EFSM的使用者只需要关心:

有限状态机变量赋值的一些小概念

有限状态机变量赋值的一些小概念

评论