1

内部变量的声明

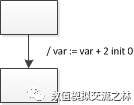

状态图环境内部的变量使用init关键字声明:

在这个例子中,我们引入了一个名为 var 的变量,类型为 int,初始值为 0。每次状态图执行遍历转换时,变量将递增 2。同一作用域中每个变量只能有一个init。

变量初始化的语法为:

varname:=expr0 init expr1

此表达式引入了一个名为 varname 的变量,其初始值在第二个表达式中给出(在 init关键字之后)。

从上述表达可以看出关键字 init 是用在过渡状态线上。

2

内部变量声明的简化写法

如果赋值中使用的表达式与用于初始化的表达式相同,则可以使用简化的语法:

我们在这里介绍两个变量 x 和 y,它们在传递初始转换时将被分配为零(整数或实数)。

变量的类型取决于用于初始化它的值。例如,在这里,使用文字整数 0 和浮点文字 0.0 分别导致实际类型 int 和 real:类型确定自动执行并最终在整个状态图中传播(任何后续使用 x 和 y 都会传播所涉及的表达式中的 int 和实数类型约束)。

注意:禁止将 int 变量与实变量混合和匹配。必须使用 to_real 和 to_int 函数进行转换。Int 常量可以在任何地方用作实常数,但在从初始状态过渡时。(看到没 to_real 和 to_int 又是两个关键字)

3

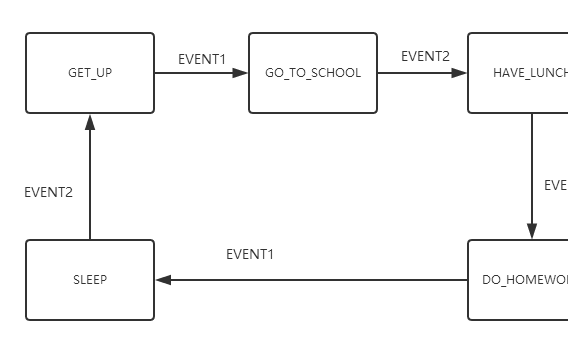

变量的作用范围

内部变量的作用范围也即是内部变量的作用域。它们仅在状态图的某些部分可见。

变量在其复合状态下可见,在下面的所有子复合(或并行)状态下可见。

此示例中有三个不同的声明变量,一个“y”变量仅在第一个复合状态下可见,因为用于声明它的 init 关键字位于此状态内的转换中。还声明了两个同名变量:“x”。一个在顶层和 Composite1 可见;另一个在 Composite2 中声明,并隐藏先前声明的变量。由于这种隐藏,Composite2 无法访问在顶级声明的变量 x。Composite 1 不会重新定义名为 x 的变量,因此可以访问在顶级声明的变量。

注意:状态图环境编译器将在存在变量隐藏的情况下生成警告消息。(警告只是警告,但不是错误)

为了简化不同变量的范围,下表综合了不同变量的范围:

-

转换器

+关注

关注

27文章

8714浏览量

147320 -

信号处理器

+关注

关注

1文章

254浏览量

25290 -

有限状态机

+关注

关注

0文章

52浏览量

10351 -

AMESIM

+关注

关注

1文章

15浏览量

11736

发布评论请先 登录

相关推荐

什么是有限状态机呢

基于VHDL的MTM总线主模块有限状态机设计

有限状态机的建模与优化设计

VHDL有限状态机设计-ST

初学者对有限状态机(FSM)的设计的认识

Linux编程之有限状态机FSM的理解与实现

如何使用FPGA实现序列检测有限状态机

AMEsim信号处理之有限状态机内部变量的声明

AMEsim信号处理之有限状态机内部变量的声明

评论