如下表所示,接口信号能工作在8Gbps及以上速率,由于速率很高,PCB布线设计要求会更严格,在前几篇关于PCB布线内容的基础上,还需要根据本篇内容的要求来进行PCB布线设计。

高速信号布线时尽量少打孔换层,换层优先选择两边是GND的层面处理。尽量收发信号布线在不同层,如果空间有限,需收发信号走线同层时,应加大收发信号之间的布线距离。

针对以上高速信号还有如下方面的要求:

01

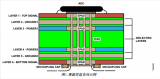

BGA焊盘区域挖参考层

如果接口的工作速率≥8Gbps,建议在BGA区域,挖掉这些信号正下方的L2层参考层,以减小焊盘的电容效应,挖空尺寸R=10mil。

如果接口的工作速率<8Gbps,例如DP接口只工作在5.4Gbps,那么不用挖BGA区域的参考层,如下图所示。

02

避免玻纤编织效应

PCB基板是由玻璃纤维和环氧树脂填充压合而成。玻璃纤维的介电常数大约是6,树脂的介电常数一般不到3。在路径长度和信号速度方面发生的问题,主要是由于树脂中的玻璃纤维增强编织方式引起的。

较为普通的玻璃纤维编织中的玻璃纤维束是紧密绞合在一起的,因此束与束之间留出的大量空隙需要用树脂填充,PCB中的平均导线宽度要小于玻璃纤维的间隔,因此一个差分对中的一条线可能有更多的部分在玻璃纤维上、更少的部分在树脂上,另一条线则相反(树脂上的部分比玻璃纤维上的多)。这样会导致D+和D-走线的特性阻抗不同,两条走线的时延也会不同,导致差分对内的时延差进而影响眼图的质量。

当接口的信号速率达到8Gbps,且走线长度超过1.5inch,需谨慎处理好玻纤编织效应。建议采用以下方式之一来避免玻纤编织效应带来的影响。

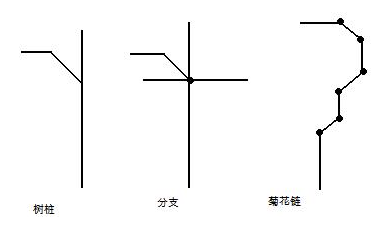

方式一:改变走线角度,如按10°~ 35°,或PCB生产加工时,将板材旋转10°以保证所有走线都不与玻纤平行,如下图所示。

方式二:使用下图走线,则W至少要大于3倍的玻纤编织间距,推荐值W=60mil,θ=10°,L=340mil。

03

差分过孔建议

1、高速信号尽量少打孔换层,换层时需在信号孔旁边添加GND过孔。地过孔数量对差分信号的信号完整性影响是不同的。无地过孔、单地过孔以及双地过孔可依次提高差分信号的信号完整性。

2、选择合理的过孔尺寸。对于多层一般密度的PCB设计来说,选用0.25mm/0.51mm/0.91mm(钻孔/焊盘/POWER隔离区)的过孔较好;对于一些高密度的PCB也可以使用0.20mm/0.46mm/0.86mm 的过孔,也可以尝试盲埋孔设计。

3、过孔中心距的变化,对差分信号的信号完整性影响是不同的。对于差分信号,过孔中心距过大或过小,均会对信号完整性产生不利影响。

4、如果接口的工作速率≥8Gbps,那么这些接口差分对的过孔尺寸建议根据实际叠层进行仿真优化。

以下给出基于EVB一阶HDI叠层的过孔参考尺寸:

R_Drill=0.1mm (钻孔半径)

R_Pad=0.2mm (过孔焊盘半径)

D1:差分过孔中心间距

D2:表层到底层的反焊盘尺寸

D3:信号过孔与回流地过孔的中心间距

04

耦合电容优化建议

1、耦合电容的放置,按照设计指南要求放置。如果没有设计指南时,若信号是IC到IC,耦合电容靠近接收端放置;若信号是IC到连接器,耦合电容请靠近连接器放置。

2、尽可能选择小的封装尺寸,减小阻抗不连续。

3、如果接口的信号工作速率≥8Gbps,那么这些接口的差分隔直电容建议按如下方式进行优化:

1)根据接口选择挖空一层或者两层地平面,如果挖空电容焊盘正下方L2地参考层,需要隔层参考,即L3层要为地参考层;

2)如果挖空L2和L3地参考层,那么L4层要为地参考层。挖空尺寸需根据实际叠层通过仿真确定;以下给出基于EVB一阶HDI叠层的参考尺寸。

【注】D1:差分耦合电容之间的中心距;L:挖空长度;H:挖空宽度。

4、在耦合电容四周打4个地通孔以将L2~L4层的地参考层连接起来,如下图所示。

05

ESD优化建议

1、ESD保护器件的寄生电容必须足够低,以允许高速信号传输而不会降级。

2、ESD需放置在被保护的IC之前,但尽量与连接器/触点PCB侧尽量靠近;放置在与信号线串联任何电阻之前;放置在包含保险丝在内的过滤或调节器件之前。

3、如果接口的信号工作速率≥8Gbps,那么这些接口的差分对ESD器件建议按以下方式优化。挖空ESD焊盘正下方L2和L3地参考层,L4层作为隔层参考层,需要为地平面。挖空尺寸需结合 ESD型号并根据实际叠层通过仿真确定。

以下给出基于基于EVB一阶HDI叠层的所用ESD型号为ESD73034D的参考尺寸:

4、同时在每个ESD四周打4个地通孔,以将L2~L4层的地参考层连接起来,如下图所示。

06

连接器优化建议

1、在连接器内走线要中心出线。如果高速信号在连接器有一端信号没有与GND相邻PIN时,设计时应在其旁边加GND孔。

2、如果接口的信号工作速率≥8Gbps,那么这些接口的连接器要能符合相应的标准要求(如HDMI2.1/DP1.4/PCI-E3.0协议标准)。推荐使用这些厂商的连接器:Molex、Amphenol、HRS等等。

3、根据接口选择挖空一层或者两层地平面,如果挖空连接器焊盘正下方的L2地参考层,需隔层参考,即L3层要作为地参考层;如果挖空L2和L3的地参考层,那么L4层需要为地平面,作为隔层参考层。挖空尺寸需结合连接器型号并根据实际叠层通过仿真确定。

4、建议在连接器的每个地焊盘各打2个地通孔,且地孔要尽可能靠近焊盘。

以下给出基于EVB一阶HDI叠层的挖空参考尺寸:

连接器推荐布线方式:

设计完PCB后,一定要做分析检查,才能让生产更顺利,这里推荐一款可以一键智能检测PCB布线布局最优方案的工具:华秋DFM软件,只需上传PCB/Gerber文件后,点击一键DFM分析,即可根据生产的工艺参数对设计的PCB板进行可制造性分析。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有300万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

https://dfm.elecfans.com/uploads/software/promoter/HQDFM%20V3.7.0_DFMGZH.zip

-

pcb

+关注

关注

4319文章

23084浏览量

397630 -

PCB布线

+关注

关注

20文章

463浏览量

42053 -

高速信号

+关注

关注

1文章

226浏览量

17696

发布评论请先 登录

相关推荐

华秋DFM软件再升级,热门功能抢先体验

高速ADC PCB布局布线技巧分享

pcb电源布线规则分享 PCB电源布线的六大技巧

PCB板设计时,铺铜有什么技巧和要点?

【华秋干货铺】PCB阻抗设计12问,轻松带你搞懂阻抗

pcb关键信号怎么样去布线

【华秋干货铺】PCB布线技巧升级:高速信号篇

【华秋干货铺】PCB布线技巧升级:高速信号篇

评论