FPGA开发过程中,利用各种IP核,可以快速完成功能开发,不需要花费大量时间重复造轮子。

当我们面对使用新IP核的情况时,总会遇到一些以前未曾接触过的新内容,这些新内容会让我们感到陌生和恐惧,不知道该如何下手。

那么今天以xilinx vivado 为例分享学习FPGA 新IP核的正确打开方式。

一、常规方式

1、导入IP

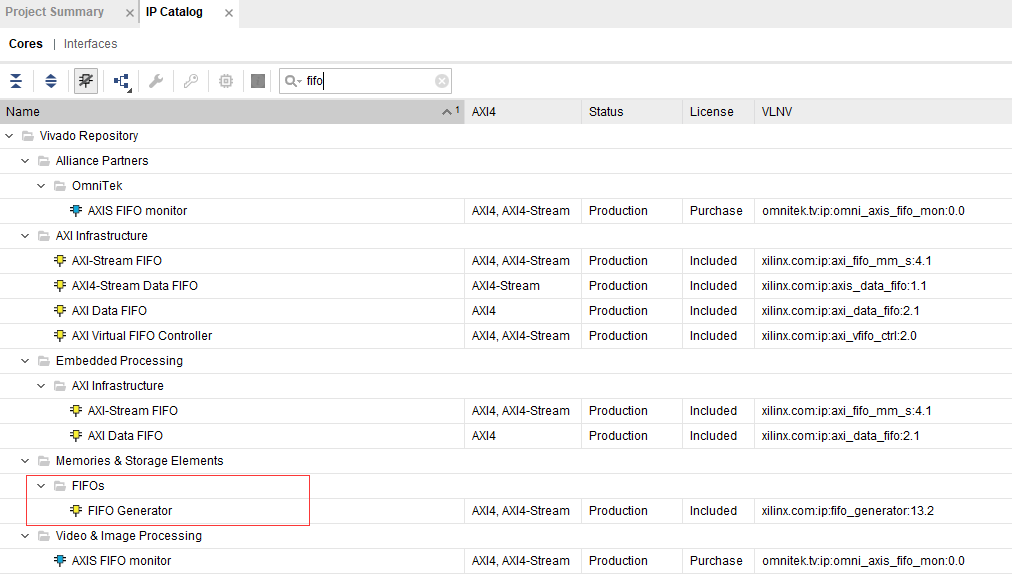

在Vivado中,点击左侧导航栏中的“IP Catalog”,输入关键词搜素要使用的IP,比如fifo,双击进行配置IP。

2、阅读手册

点击左上角”Documentation“,可以阅读官方的IP说明手册、IP更新信息、常见问题及解决方式。这里选择点击“Product Guide”可以转到Xilinx的DocNav中,打开当前IP手册,如果对这个IP很熟悉,可以跳过这一步。

3、配置IP

根据实际的需求配置IP的参数,如工作时钟等,配置完成后,点击OK,选择OOC编译,等编译完成后,这样在“Design source”中可看到新定义的IP。

4、生成例程

右键点击刚生成的IP,选择“Open IPExample Design”,打开IP对应配置下的测试工程,选择指定路径,自动打开新生成的测试工程。

4、阅读示例工程,仿真分析

工程中包含了时钟、复位及输入输出、AXI总线协议等必要的配置,包含TestBench仿真测试文件,阅读分析源码,仿真查看波形,通过少量更改可以下板测试,ILA监测,参考示例工程,在实际应用中即可使用。

通过以上步骤,您可以更好地理解和使用Xilinx的IP核。

二、其它方式

可以通过百度或google搜索这个IP的相关博客,看看网上大牛们是怎么用和理解这个IP的,一般都会有详细的经验分享。

再来看xilinx官方手册。

这样上手起来也更快一些,可以少走一些弯路。

-

FPGA

+关注

关注

1629文章

21743浏览量

603558 -

Xilinx

+关注

关注

71文章

2167浏览量

121481 -

时钟

+关注

关注

11文章

1734浏览量

131501 -

IP核

+关注

关注

4文章

327浏览量

49503

发布评论请先 登录

相关推荐

错误的用视频文件打开schdoc文件,怎么把打开方式改回去?

游戏融网:结婚的正确打开方式

请问怎么删除以记事本方式打开的FNG文件的打开方式

WinXP系统tbi文件如何打开 WinXP系统tbi文件打开方式

Design Compiler打开方式

RISC-V MCU IDE MRS(MounRiver Studio)开发之:绑定各后缀名文件打开方式

FPGA新IP核学习的正确打开方式

使用微波炉应当注意的问题及其正确的打开方式

别自嗨了,VR开始正确打开方式节日营销

allegro设置SCH和pcb文件的默认打开方式方法

学习FPGA新IP核的正确打开方式

学习FPGA新IP核的正确打开方式

评论