来源:半导体芯科技编译

业内率先推出8层垂直堆叠的24GB容量HBM3 Gen2,带宽超过1.2TB/s,并通过先进的1β工艺节点实现“卓越功效”。

美光科技已开始提供业界首款8层垂直堆叠的24GB容量HBM3 Gen2内存样品,其带宽超过1.2TB/s,引脚速度超过9.2Gb/s,相比目前出货的HBM3解决方案提高了50%。美光的HBM3 Gen2产品的每瓦性能是前几代产品的2.5倍,据称为关键人工智能(AI)数据中心性能、容量和功效指标创造了新记录。美光本次改进可减少GPT-4等大型语言模型的训练时间,为AI推理提供高效的基础设施应用,并提供卓越的总拥有成本(TCO)。

美光高带宽内存(HBM)解决方案的基础是美光1β (1-beta) DRAM工艺节点,该节点允许将24Gb DRAM芯片组成行业标准封装尺寸内的8层垂直堆叠的立方体。此外,美光的12层垂直堆叠的堆栈容量为36GB,将于2024年第一季度开始提供样品。美光表示,与现有的竞争解决方案相比,它在给定的堆栈高度下提供的容量增加了50%。美光的HBM3 Gen2 性能功耗比和引脚速度改进对于管理当今人工智能数据中心的极端功耗需求至关重要。美光在技术方面的进步,让能效提升成为可能,例如硅通孔(TSV)比竞争对手的HBM3产品增加了一倍,通过金属密度增加五倍,从而降低热阻抗,此外,还设计了更为节能的数据通路。

美光很荣幸成为台积电3DFabric Alliance的合作伙伴,帮助塑造半导体和系统的创新未来。作为HBM3 Gen2产品开发工作的一部分,美光与台积电之间的合作为AI和HPC设计应用计算系统的顺利引入和集成奠定了基础。台积电已收到美光HBM3 Gen2内存样品,并与美光密切合作进行进一步的评估和测试,助力客户的下一代HPC应用创新。

美光HBM3 Gen2解决方案满足了生成式AI领域对多模态、数万亿参数AI模型日益增长的需求。每个立方体容量为24GB,引脚速度超过9.2Gb/s,大型语言模型的训练时间减少30%以上,从而降低TCO。此外,美光产品触发每日查询量显着增加,从而能够更有效地利用经过训练的模型。美光HBM3 Gen2拥有业界一流的每瓦性能,能切实推动现代AI数据中心节省成本。对于安装1000万个GPU的情况,每个HBM立方体可节约5W功耗,预计在五年内可节省高达5.5亿美元的运营费用。

美光计算产品集团副总裁兼总经理Praveen Vaidyanathan表示:“美光HBM3 Gen2技术的开发旨在为客户和行业提供卓越的人工智能和高性能计算解决方案。对我们来说,一个重要的标准是,HBM3 Gen2产品在客户平台上是否易于集成。其完全可编程的内存内建自测试(MBIST)可在完整规格的引脚速度下运行,能够为客户提供更强大的测试能力,实现高效协作,助力客户缩短产品上市时间。”

NVIDIA超大规模和HPC计算副总裁Ian Buck表示:“生成式AI的核心是加速计算,它受益于HBM高带宽,可带来更出色的能效。我们与美光在众多产品领域有着长期合作,并且非常期待与美光在HBM3 Gen2上合作,促进AI创新。”

美光利用其全球工程机构开发了这一突破性产品,于美国进行设计和工艺开发,在日本进行内存制造,在台湾进行先进封装。美光此前宣布推出基于1α (1-alpha)节点、24Gb单块DRAM裸片的96GB容量DDR5模组,用于大容量服务器解决方案,如今又推出了基于1β节点24Gb芯片24GB容量HBM3产品。公司还计划在2024年上半年推出基于1β节点32Gb单块DRAM裸片的128GB容量DDR5模组。这些产品展示了美光在AI服务器方面的技术创新。

审核编辑 黄宇

-

封装

+关注

关注

126文章

7767浏览量

142696 -

AI

+关注

关注

87文章

30072浏览量

268331 -

HBM

+关注

关注

0文章

372浏览量

14704

发布评论请先 登录

相关推荐

风景独好?12层HBM3E量产,16层HBM3E在研,产业链涌动

HBM4到来前夕,HBM热出现两极分化

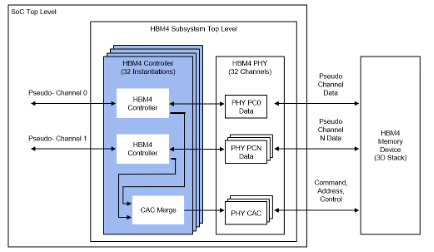

Rambus推出业界首款HBM4控制器IP

Rambus宣布推出业界首款HBM4控制器IP,加速下一代AI工作负载

SK海力士引领未来:全球首发12层HBM3E芯片,重塑AI存储技术格局

美光出样业界容量密度最高新一代 GDDR7 显存

SK海力士加速HBM4E内存研发,预计2026年面市

预期HBM供应将大幅增长,驱动DRAM产业发展

三星电子发布业界最大容量HBM

HBM、HBM2、HBM3和HBM3e技术对比

三星电子成功发布其首款12层堆叠HBM3E DRAM—HBM3E 12H

三星发布首款12层堆叠HBM3E DRAM,带宽高达1280GB/s,容量达36G

深度解析HBM内存技术

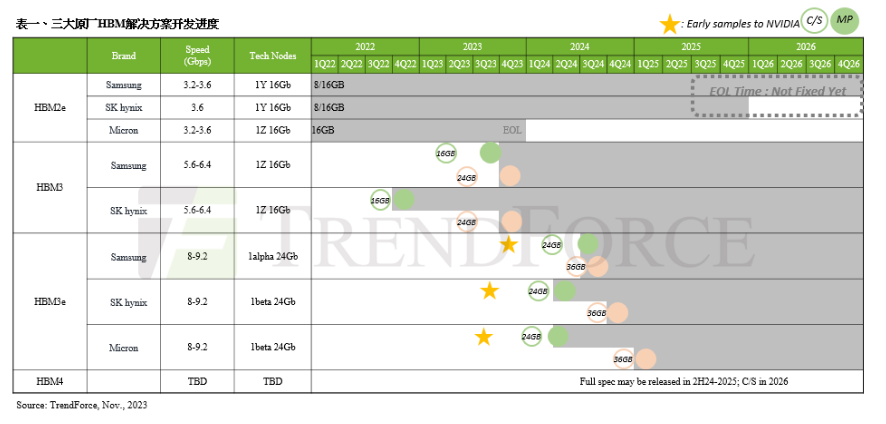

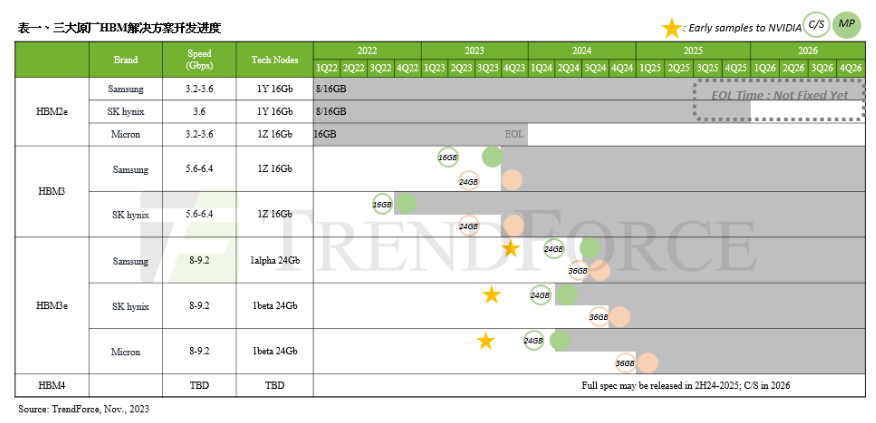

英伟达将于Q1完成HBM3e验证 2026年HBM4将推出

预计英伟达将于Q1完成HBM3e验证 2026年HBM4将推出

业界最快、容量最高的HBM?

业界最快、容量最高的HBM?

评论