1、硬件描述语言HDL(Hardware Description Language)

硬件描述语言(HDL)是一种用形式化方法来描述数字电路和系统的语言。数字电路系统的设计者利用这种语言可以从上层到下层(从抽象到具体)逐层描述自己的设计思想,用一系列分层次的模块来表示极其复杂的数字系统。然后利用电子设计自动化(以下简称为EDA)工具逐层进行仿真验证,再把其中需要变为具体物理电路的模块组合经由自动综合工具转换到门级电路网表。接下去再用专用集成电路(ASIC)或现场可编程门阵列(FPGA)自动布局布线工具把网表转换为具体电路布线结构的实现。在制成物理器件之前,还可以用Verilog的门级模型(原语元件或UDP)来代替具体基本元件。因其逻辑功能和延时特性与真实的物理元件完全一致,所以在仿真工具的支持下能验证复杂数字系统物理结构的正确性,使投片的成功率达到100%。目前,这种称之为高层次设计(High-Level-Design)的方法已被广泛采用。据统计,目前在美国硅谷约有90%以上的ASIC和FPGA已采用Verilog硬件描述语言方法进行设计。

硬件描述语言的发展至今已有近三十年的历史,并成功地应用于设计的各个阶段:建模、仿真、验证 和综合等。最近十多年来,用综合工具把可综合风格的HDL模块自动转换为具体电路发展非常迅速,大大地提高了复杂数字系统的设计生产率。在美国和日本等先进电子工业国,Verilog语言已成为设计数字系统的基础。

对于FPGA新手应由浅入深学习:

(1)Verilog的基本语法,

(2)简单的可综合Verilog模块与逻辑电路的对应关系,

(3)简单的Verilog测试模块和它的意义,

(4)如何编写复杂的多层次的可综合风格的Verilog HDL模块,

(5)如何用可综合的Verilog模块构成一个可靠的复杂IP软核和固核模块,

(6)在开发工具建立自己的FPGA工程,实现简单FPGA小例子。

2、Verilog HDL的历史

2.1、什么是Verilog HDL

Verilog HDL是硬件描述语言的一种,用于数字电子系统设计。它允许设计者用它来进行各种级别的逻辑设计,可以用它进行数字逻辑系统的仿真验证、时序分析、逻辑综合。它是目前应用最广泛的一种硬件描述语言。据有关文献报道,目前在美国使用Verilog HDL进行设计的工程师大约有10多万人,全美国有200多所大学教授用 Verilog 硬件描述语言的设计方法。在我国台湾地区几乎所有著名大学的电子和计算机工程系都讲授Verilog有关的课程。

2.2、Verilog HDL的产生及发展

Verilog HDL是在1983年,由GDA(GateWay Design Automation)公司的Phil Moorby首创的。Phil Moorby后来成为Verilog-XL的主要设计者和Cadence公司(Cadence Design System)的第一个合伙人。在1984-1985年,Moorby设计出了第一个名为Verilog-XL的仿真器,1986年,他对Verilog HDL的发展又作出了另一个巨大贡献:即提出了用于快速门级仿真的XL算法。

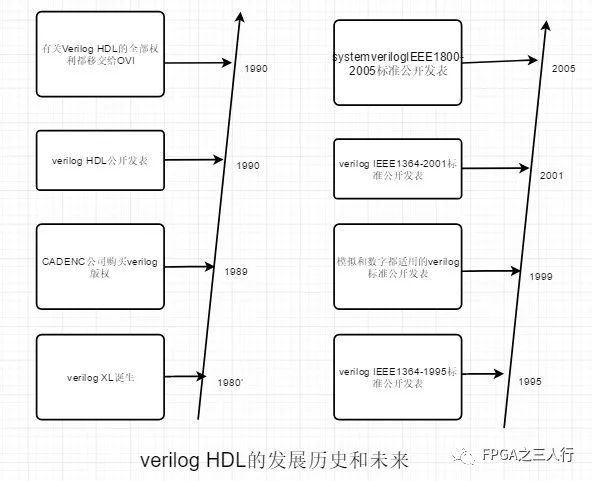

随着Verilog-XL算法的成功,Verilog HDL语言得到迅速发展。1989年,Cadence公司收购了GDA公司,Verilog HDL语言成为Cadence公司的私有财产。1990年,Cadence公司决定公开Verilog HDL语言,于是成立了OVI(Open Verilog International)组织来负责促进Verilog HDL语言的发展。基于Verilog HDL的优越性,IEEE于1995年制定了Verilog HDL的IEEE标准,即Verilog HDL1364-1995;2001年发布了Verilog HDL1364-2001标准;2005年SystemVerilog IEEE 1800-2005 标准的公布,更使得Verilog语言在综合、仿真验证和模块的重用等性能方面都有大幅度的提高。

下图展示了Verilog的发展历史和未来。

图1

2.3、Verilog HDL和 VHDL的比较

Verilog HDL和VHDL都是用于逻辑设计的硬件描述语言,并且都已成为IEEE标准。VHDL是在1987年成为IEEE标准,Verilog HDL则在1995年才正式成为IEEE标准。之所以VHDL比Verilog HDL早成为IEEE标准,这是因为VHDL是由美国军方组织开发的,而Verilog HDL 则是从一个普通的民间公司的私有财产转化而来,基于Verilog HDL的优越性,才成为的IEEE标准,因而有更强的生命力。

VHDL 其英文全名为VHSIC Hardware Description Language,而VHSIC则是Very High Speed Integerated Circuit的缩写词,意为甚高速集成电路,故VHDL其准确的中文译名为甚高速集成电路的硬件描述语言。

Verilog HDL和VHDL作为描述硬件电路设计的语言,其共同的特点在于:能形式化地抽象表示电路的行为和结构、支持逻辑设计中层次与范围的描述、可借用高级语言的精巧结构来简化电路行为的描述、具有电路仿真与验证机制以保证设计的正确性、支持电路描述由高层到低层的综合转换、硬件描述与实现工艺无关(有关工艺参数可通过语言提供的属性包括进去)、便于文档管理、易于理解和设计重用。

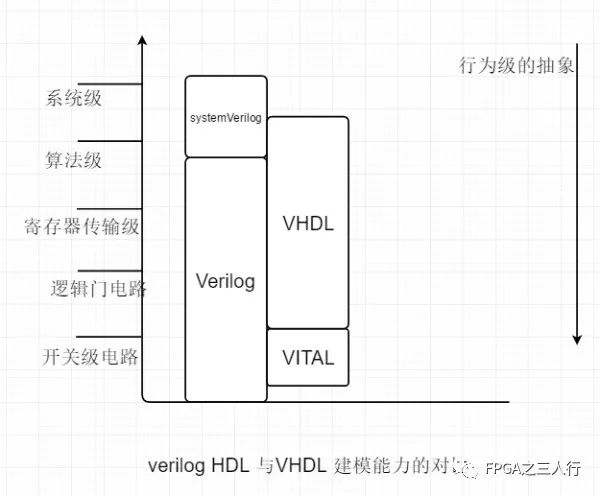

但是Verilog HDL和VHDL又各有其自己的特点。由于Verilog HDL早在1983年就已推出,至今已有二十多年的应用历史,因而Verilog HDL拥有更广泛的设计群体,成熟的资源也远比VHDL丰富。与VHDL相比Verilog HDL的最大优点是:它是一种非常容易掌握的硬件描述语言,只要有C语言的编程基础,通过二十学时的学习,再加上一段实际操作,一般同学可在二至三个月内掌握这种设计方法的基本技术。而掌握VHDL设计技术就比较困难。这是因为VHDL不很直观,需要有Ada编程基础,一般认为至少需要半年以上的专业培训,才能掌握VHDL的基本设计技术。2005年SystemVerilog IEEE1800-2005标准公布以后,集成电路设计界普遍认为Verilog HDL 将在十年内全面取代VHDL成为ASIC设计行业包揽设计、测试和验证功能的的唯一语言。下面图2所示的是Verilog HDL和VHDL建模能力的比较图,供读者参考:

图2

2001年公布的VerilogIEEE1364- 2001标准和2005年公布的SystemVerilog IEEE1800-2005标准,不但使Verilog的可综合性能和系统仿真性能方面有大幅度的提高,而且在IP的重用方面(包括设计和验证模块的重用)也有重大的突破。因此Verilog HDL不但作为学习HDL设计方法的入门和基础是比较合适的,而且对于ASIC设计专业人员而言,也是必须掌握的基本技术。学习掌握Verilog HDL建模、仿真、综合、重用和验证技术不仅可以使同学们对数字电路设计技术有更进一步的了解,而且可以为以后学习高级的行为综合、物理综合、IP设计和复杂系统设计和验证打下坚实的基础。

2.4、 Verilog 目前的应用情况和适用的设计

近十多年以来,EDA界一直对在数字逻辑设计中究竟采用哪一种硬件描述语言争论不休。近两三年来,美国、日本和我国台湾省电子设计界的情况已经清楚地表明,在高层次数字系统设计领域,Verilog 已经取得压倒性的优势;在中国大陆,近10年来,Verilog应用的比率已有显著的增加。根据笔者了解,国内大多数集成电路设计公司都采用Verilog HDL。Verilog是专门为复杂数字系统的设计仿真而开发的,本身就非常适合复杂数字逻辑电路和系统的仿真和综合。由于Verilog 在其门级描述的底层,也就是在晶体管开关的描述方面比VHDL有强得多得功能,所以即使是VHDL的设计环境,在底层实质上也是由Verilog HDL描述的器件库所支持的。1998年通过的Verilog HDL新标准,把Verilog HDL-A并入Verilog HDL新标准,使其不仅支持数字逻辑电路的描述还支持模拟电路的描述,因此在混合信号的电路系统的设计中,它也有很广泛的应用。在深亚微米ASIC和高密度FPGA已成为电子设计主流的今天,Verilog的发展前景是非常远大的。2001年3月,Verilog IEEE1364-2001标准的公布,以及2005年10月SystemVerilog IEEE 1800-2005 标准的公布,使得Verilog语言在综合、仿真验证和IP模块重用等性能方面都有大幅度的提高,更加拓宽了Verilog的发展前景。

Verilog适合系统级(System)、算法级(Alogrithem)、寄存器传输级(RTL)、逻辑级(Logic)、门级(Gate)、电路开关级(Switch)设计,而SystemVerilog是Verilog语言的扩展和延伸,更适用于可重用的可综合IP和可重用的验证用IP设计,以及特大型(千万门级以上)基于IP的系统级设计和验证。

2.5、采用Verilog HDL设计复杂数字电路的优点

2.5.1、传统设计方法--电路原理图输入法

几十年前,当时所做的复杂数字逻辑电路及系统的设计规模比较小也比较简单,其中所用到的FPGA或ASIC设计工作往往只能采用厂家提供的专用电路图输入工具来进行。为了满足设计性能指标,工程师往往需要花好几天或更长的时间进行艰苦的手工布线。工程师还得非常熟悉所选器件的内部结构和外部引线特点,才能达到设计要求。这种低水平的设计方法大大延长了设计周期。

近年来,FPGA和ASIC的设计在规模和复杂度方面不断取得进展,而对逻辑电路及系统的设计的时间要求却越来越短。这些因素促使设计人员采用高水准的设计工具,如:硬件描述语言(Verilog HDL或VHDL)来进行设计。

2.5.2、 Verilog HDL设计法与传统的电路原理图输入法的比较

如 2.5.1.所述,采用电路原理图输入法进行设计,具有设计的周期长,需要专门的设计工具,需手工布线等缺陷。而采用Verilog 输入法时,由于Verilog HDL的标准化,可以很容易地把完成的设计移植到不同的厂家的不同的芯片中去,并在不同规模的应用时可以较容易地作修改。这不仅是因为用Verilog HDL所完成的设计,它的信号位数是很容易改变的,可以很容易地对它进行修改,来适应不同规模的应用,在仿真验证时,仿真测试矢量还可以用同一种描述语言来完成,而且还因为采用Verilog HDL综合器生成的数字逻辑是一种标准的电子设计互换格式(EDIF)文件,独立于所采用的实现工艺。有关工艺参数的描述可以通过 Verilog HDL提供的属性包括进去,然后利用不同厂家的布局布线工具,在不同工艺的芯片上实现。

采用Verilog 输入法最大的优点是其与工艺无关性。这使得工程师在功能设计、逻辑验证阶段,可以不必过多考虑门级及工艺实现的具体细节,只需要利用系统设计时对芯片的要求,施加不同的约束条件,即可设计出实际电路。实际上这是利用了计算机的巨大能力在EDA工具的帮助下,把逻辑验证与具体工艺库匹配、布线及时延计算分成不同的阶段来实现从而减轻了人们的繁琐劳动。

2.5.3、Verilog 的标准化

Verilog 是在1983年由GATEWAY公司首先开发成功的,经过诸多改进,于1995年11月正式被批准为Verilog IEEE1364-1995标准,2001年3月在原标准的基础上经过改进和补充又推出Verilog IEEE1364-2001新标准。2005年10月又推出了Verilog语言的扩展,即SystemVerilog (IEEE 1800-2005 标准)语言,这使得Verilog语言在综合、仿真验证和IP模块重用等性能方面都有大幅度的提高,更加拓宽了Verilog的发展前景。

Verilog HDL的标准化大大加快了Verilog HDL的推广和发展。由于Verilog HDL设计方法的与工艺无关性,因而大大提高了Verilog模型的可重用性。

2.5.4、软核

我们把功能经过验证的、可综合的、实现后电路结构总门数在5000门以上的Verilog HDL模型称之为“软核”(Soft Core)。而把由软核构成的器件称为虚拟器件,在新电路的研制过程中,软核和虚拟器件可以很容易地借助EDA综合工具与其它外部逻辑结合为一体。这样,软核和虚拟器件的重用性就可大大缩短设计周期,加快了复杂电路的设计。

2.5.5、固核和硬核的概念以及它们的重用

2.5.5.1、固核

我们把在某一种现场可编程门阵列(FPGA)器件上实现的,经验证是正确的总门数在5000门以上电路结构编码文件,称之为“固核”。

2.5.5.1、硬核

我们把在某一种专用集成电路工艺的(ASIC)器件上实现的经验证是正确的总门数在5000门以上的电路结构版图掩膜,称之为“硬核”。

2.5.5.3、软核、固核、硬核对比

在具体实现手段和工艺技术尚未确定的逻辑设计阶段,软核具有最大的灵活性,它可以很容易地借助EDA综合工具与其它外部逻辑结合为一体。当然,由于实现技术的不确定性,有可能要作一些改动以适应相应的工艺。相比之下固核和硬核与其它外部逻辑结合为一体的灵活性要差得多,特别是电路实现工艺技术改变时更是如此。而近年来电路实现工艺技术的发展是相当迅速的,为了逻辑电路设计成果的积累,和更快更好地设计更大规模的电路,发展软核的设计和推广软核的重用技术是非常有必要的。我们新一代的数字逻辑电路设计师必须掌握这方面的知识和技术。Verilog语言以及它的扩展SystemVerilog 是设计可重用的IP,即软核、固核、硬核和验证用虚拟核所必须的语言。

2.6、FPGA硬件描述语言设计流程

2.6.1、自顶向下(Top-Down)设计

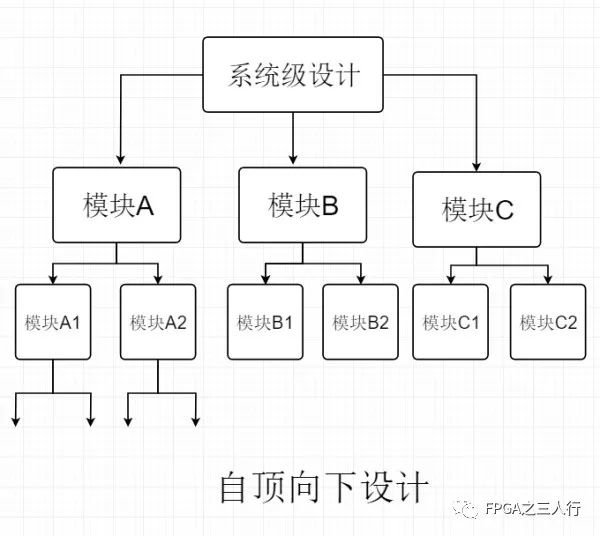

自顶向下的设计(即TOP_DOWN设计)是从系统级开始,把系统划分为基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接用EDA元件库中的基本元件来实现为止。利用层次化、结构化的设计方法,一个完整的硬件设计任务首先由总设计师(Architect)划分为若干个可操作的模块,编制出相应的模型(行为的或结构的),通过仿真加以验证后,再把这些模块分配给下一层的设计师。这就允许多个设计者同时设计一个硬件系统中的不同模块,其中每个设计者负责自己所承担的部分;而由上一层设计师对其下层设计者完成的设计用行为级上层模块对其所做的设计进行验证。为了提高设计质量,如果其中有一部分模块可由商业渠道得到,我们可以购买它们的知识产权的使用权(IP核的重用),以节省时间和开发经费,。图3为自顶向下的示意图,以设计树的形式绘出。

图3 自顶向下设计

2.6.2、FPGA模块的设计编译和仿真的过程

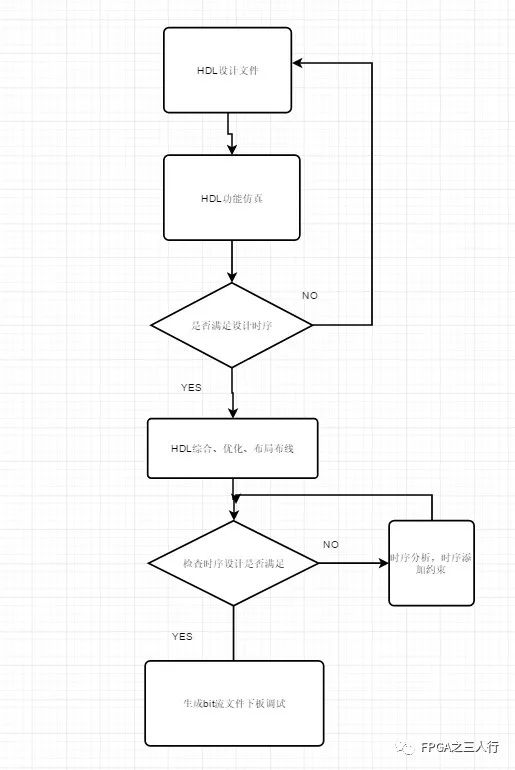

在不同的层次做具体模块的设计所用的方法也有所不同,在高层次上往往编写一些行为级的模块通过仿真加以验证,其主要目的是系统性能的总体考虑和各模块的指标分配,并非具体电路的实现。因而综合及其以后的步骤往往不需进行。而当设计的层次比较接近底层时,行为描述往往需要用电路逻辑来实现。这时的模块不仅需要通过仿真加以验证,还需进行综合、优化、布线和后仿真。总之具体电路是从底向上逐步实现的。EDA工具往往不仅支持HDL描述也支持电路图输入,有效地利用这两种方法是提高设计效率的办法之一。下面的流程图简要地说明了模块的编译和测试过程:

图4

从上图可以看出,模块设计流程主要由两大主要功能部分组成:

(1)、设计开发:即从编写设计文件-->综合到布局布线-->电路生成这样一系列步骤。

(2)、设计验证:也就是进行各种仿真的一系列步骤,如果在仿真过程中发现问题就返回设计输入进行修改。

2.7、总结

2.7.1、编程语言verilog的优点

(1)采用VerilogHDL进行电路设计的最大优点是设计与工艺无关系,

(2)能够在每个抽象层次的描述上对设计进行仿真验证,

(3)VerilogHDL适用于复杂数字逻辑电路和系统的总体仿真、子系统仿真和具体电路综合等各个设计阶段。

2.7.2、熟练掌握FPGA设计流程

由于TOP_DOWN的设计方法是首先从系统设计入手,从顶层进行功能划分和结构设计。系统的总体仿真是顶层进行功能划分的重要环节,这时的设计是与工艺无关的。由于设计的主要仿真和调试过程是在高层次完成的所以能够早期发现结构设计上的错误,避免设计工作的浪费,同时也减少了逻辑仿真的工作量。自顶向下的设计方法方便了从系统级划分和管理整个项目,使得几十万门甚至几千万门规模的复杂数字电路的设计成为可能,并可减少设计人员,避免不必要的重复设计,提高了设计的一次成功率。

从底向上的设计在某种意义上讲可以看作上述TOP_DOWN设计的逆过程。虽然设计也是从系统级开始,即从设计树的树根开始对设计进行逐次划分,但划分时首先考虑的是单元是否存在,即设计划分过程必须从已经存在的基本单元出发,设计树最末枝上的单元要么是已经制造出的单元,要么是其它项目已开发好的单元或者是可外购得到的单元。

-

FPGA

+关注

关注

1630文章

21796浏览量

605526 -

Verilog

+关注

关注

28文章

1351浏览量

110310 -

HDL

+关注

关注

8文章

328浏览量

47439 -

编程语言

+关注

关注

10文章

1950浏览量

34929

原文标题:FPGA之编程语言verilog

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Verilog HDL的历史 FPGA硬件描述语言设计流程

Verilog HDL的历史 FPGA硬件描述语言设计流程

评论