前言

前面我们学习了8259A,但8259A 只适合单 CPU 的情况,为了充分挖掘 SMP 体系结构的并行性,能够把中断传递给系统中的每个 CPU 至关重要。基于此理由,Intel 引入了一种名为 I/O 高级可编程控制器的新组件,来替代老式的 8259A 可编程中断控制器。下面一起来学习一下APIC。

0 APIC概述

Intel从Pentium处理器开始引入了APIC(Advanced Programmable Interrupt Controller)机制,直译为高级可编程中断控制器。引入APIC机制是为了适应multiple processor(MP,多处理器)环境。

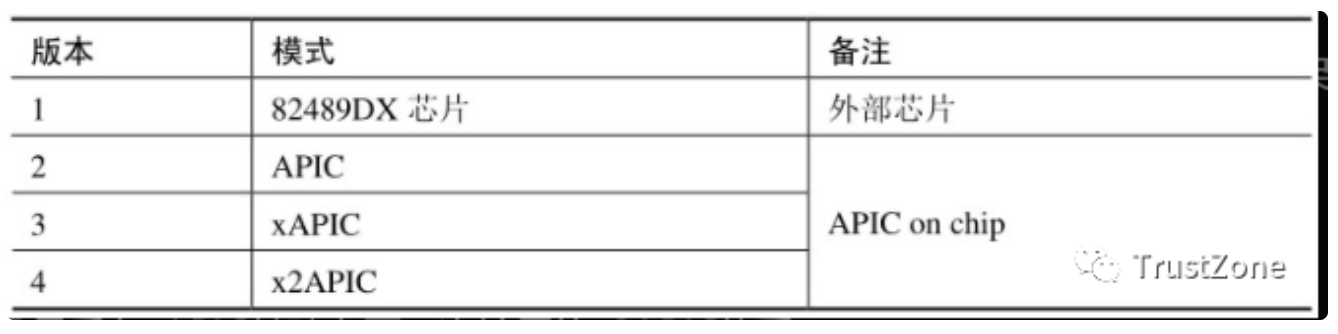

APIC经历了4个版本

最初的APIC属于外部设备,以外部的82489DX芯片形式存在。在P6家族和Pentium处理器后,以APIC on Chip形式存在,引入了处理器内部的local APIC架构,和82489DX 外部APIC相比较功能得到了扩展和增强。

Pentium 4和Intel Xeon处理器在APIC的基础上进一步扩展,形成了xAPIC体系,以及最后在xAPIC基础上再一次扩展的x2APIC体系。

1 APIC

每个logical processor(逻辑处理器)都有自己的local APIC,每个local APIC包括了一组local APIC寄存器,用来控制local和external中断的产生、发送和接收等,也产生和发送IPI(处理器间的中断消息)。local APIC寄存器组以内存映射形式映射到物理地址空间上,因此软件可以使用MOV指令进行访问。

然而在x2APIC模式上local APIC寄存器映射到MSR寄存器组来代替映射内存,软件使用RDMSR和WRMSR指令来访问local APIC寄存器。

如下所示,这是在支持Intel Hyper-Threading Technology的MP系统上,两个logical processor(线程)共享一个processor core执行单元。

每个local APIC有自己的local APIC ID,这个ID决定了logical processor在system bus上的地址,可以用于处理器间的消息接收和发送,也可用于外部中断消息的接收。

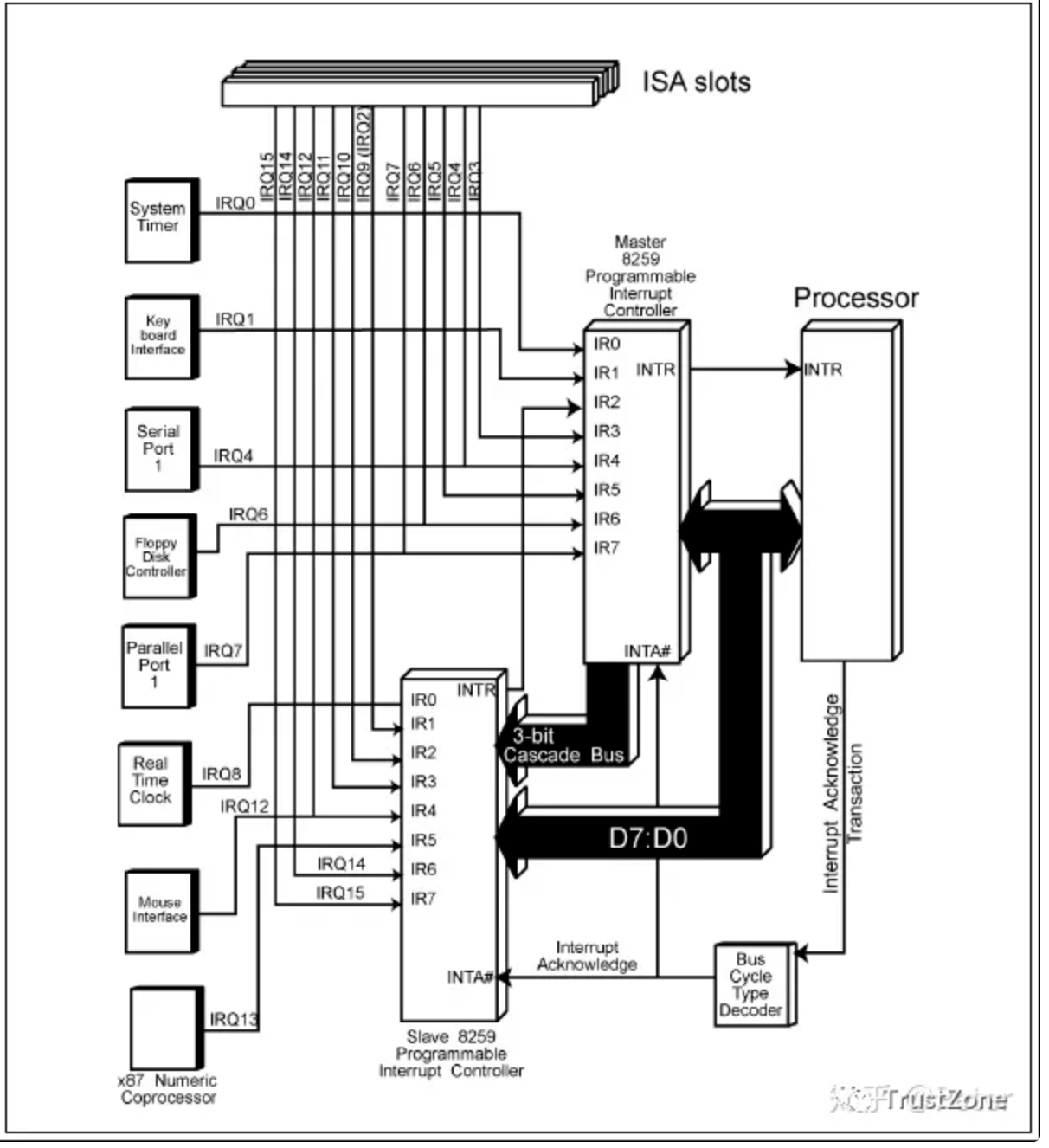

标准PC上两片级联的8259提供了理论上15个中断输入源,但实际系统中这些中断源远远不够用。

从Pentium开始,微机系统中引入了高级可编程中断控制器APIC(Advanced Programmable Interrupt Controller), APIC兼容PIC(Programmable Interrupt Controller)。

新型高级可编程中断控制器SAPIC(StreamLined Advanced Programmable Interrupt Controller)是APIC的64位升级版本。

APIC可以用于单CPU和多CPU系统中。 引入APIC一方面是为了支持多处理器系统需要 ,使外部中断能被有选择地交给某一个CPU来处理。

CPU利用处理器间中断IPI (Inter-Processor Interrupt),可以将一个外部中断交给另一个CPU来处理 ,也可以在CPU之间发布消息,或者实现抢占式调度。

多处理器系统中,CPU通过彼此发送中断来完成它们之间的通信。另一方面,扩展了系统可用的中断数达到24个,分隔了PCI/ISA设备使用的中断,在APIC系统中只有PCI设备才能使用16~23号中断,而ISA设备仍然使用常规的0~15号中断,解决了使用8259中断控制器所带来的中断共享、中断优先级不易控制等问题。

ISA总线: (Industry Standard Architecture:工业标准体系结构)是为PC/AT电脑而制定的总线标准,为16位体系结构,只能支持16位的I/O设备,数据传输率大约是16MB/S。也称为AT标准。ISA是IndustryStandardArchitecture的缩写ISA插槽是基于ISA总线(IndustrialStandardArchitecture,工业标准结构总线)的扩展插槽,其颜色一般为黑色,比PCI接口插槽要长些,位于主板的最下端。其工作频率为8MHz左右,为16位插槽,最大传输率16MB/sec,可插接显卡,声卡,网卡已及所谓的多功能接口卡等扩展插卡。其缺点是CPU资源占用太高,数据传输带宽太小,是已经被淘汰的插槽接口。

ISA是8/16bit的系统总线,最大传输速率仅为8MB/s,但允许多个CPU共享系统资源。由于兼容性好,它在上个世纪80年代是最广泛采用的系统总线,不过它的弱点也是显而易见的,比如传输速率过低、CPU占用率高、占用硬件中断资源等。后来在PC‘98规范中,就开始放弃了ISA总线,而Intel从i810芯片组开始,也不再提供对ISA接口的支持。

PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准,它原来的名称为“3GIO”,是由英特尔在2001年提出的,旨在替代旧的PCI,PCI-X和AGP总线标准。PCI总线已成为了计算机的一种标准总线。

PCI总线取代了早先的ISA总线。有许多优点,比如即插即用(Plug and Play)、中断共享等。所谓即插即用,是指当板卡插入系统时,系统会自动对板卡所需资源进行分配,如基地址、中断号等,并自动寻找相应的驱动程序。而不象旧的ISA板卡,需要进行复杂的手动配置。实际的实现远比说起来要复杂。

在PCI板卡中,有一组寄存器,叫"配置空间"(Configuration Space),用来存放基地址与内存地址,以及中断等信息。以内存地址为例。当上电时,板卡从ROM里读取固定的值放到寄存器中,对应内存的地方放置的是需要分配的内存字节数等信息。

操作系统要根据这个信息分配内存,并在分配成功后把相应的寄存器中填入内存的起始地址。这样就不必手工设置开关来分配内存或基地址了。对于中断的分配也与此类似。ISA卡的一个重要局限在于中断是独占的,而我们知道计算机的中断号只有16个,系统又用掉了一些,这样当有多块ISA卡要用中断时就会有问题了。PCI总线的中断共享由硬件与软件两部分组成。

硬件上,采用电平触发的办法:中断信号在系统一侧用电阻接高,而要产生中断的板卡上利用三极管的集电极将信号拉低。这样不管有几块板产生中断,中断信号都是低;而只有当所有板卡的中断都得到处理后,中断信号才会回复高电平。

软件上,采用中断链的方法:假设系统启动时,发现板卡A用了中断7,就会将中断7对应的内存区指向A卡对应的中断服务程序入口ISR_A;然后系统发现板卡B也用中断7,这时就会将中断7对应的内存区指向ISR_B,同时将ISR_B的结束指向ISR_A。

以此类推,就会形成一个中断链。而当有中断发生时,系统跳转到中断7对应的内存,也就是ISR_B。ISR_B就要检查是不是B卡的中断,如果是,要处理,并将板卡上的拉低电路放开;如果不是,则呼叫ISR_A。这样就完成了中断的共享。咱们继续

值得注意的是,只有Windows 2000以后的操作系统才支持APIC, Linux可以支持但需要定制,缺省安装并不支持。

BIOS运行于实模式,不支持APIC, APIC只有在保护模式下才能使用。 (因此8259A)

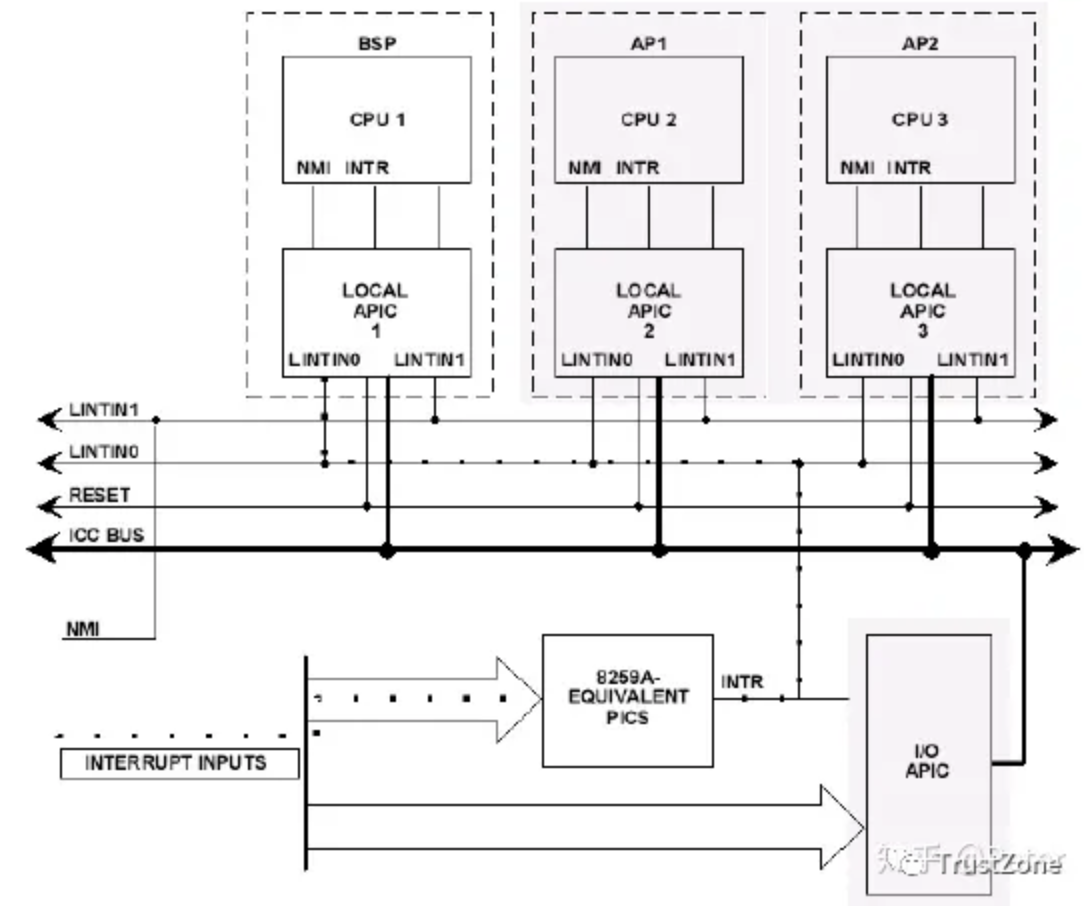

整个APIC系统可以分为两大部分:LAPIC(Local APIC)和IO APIC,如图23所示。

单核或者多核情况下,每个处理器中都有自己的LAPIC,而IO APIC是作为系统芯片组中一部分,在PCI-to-ISA bridge的LPC控制器内,系统最多有8个IO APIC。

LAPIC通过系统总线接收该处理器产生的本地中断(例如时钟中断等)及处理器间中断,并接收外部的中断消息,如来自IO APIC的消息等。

IO APIC负责接收所有外部的硬件中断,并翻译成消息选择发给接收中断的处理器。

APIC功能可以被关闭。 APIC被关闭时,由集成在芯片组内的8259功能模块来处理中断 , 此时LAPIC的引脚LINT0连接到INTR, LINT1连接到NMI 。本节介绍的APIC以Pentium 4和Xeon为主,Pentium采用的APIC有所不同。

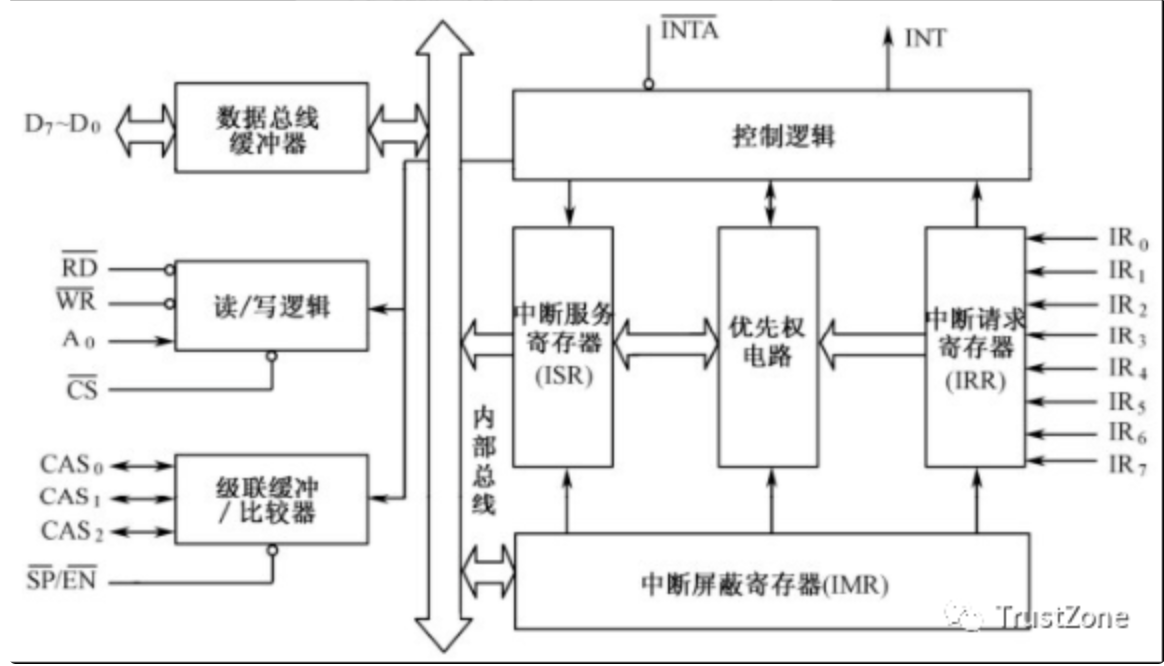

8259A内部结构

2 LAPIC

典型地,8259兼容类的legacy中断控制器是在uni-processor(单处理器)系统上使用,已不能适应于多处理器环境,而I/O APIC能适用于multi-porcessor(多处理器)环境上。

I/O APIC可以发送中断消息到指向的logical processor上。I/O APIC属于芯片组的一部分,现称为PCH(Platform controller Hub),位于PCIto-ISA bridge(南桥芯片)的LPC控制器上。

各芯片组厂商的南桥名称都有所不同,例如英特尔称之为I/O路径控制器(ICH,IO Controller Hub)或平台路径控制器(PCH)。因此后面看着叫PCH也不需要奇怪哦!!!

I/O APIC也有自己的寄存器,同样也以内存映射形式映射到物理地址空间上。

LAPIC(Local APIC,本地APIC)包含了8259和8254的功能。

Intel 8253/8254是一个可编程定时/计数器(PIT-Programmable Interval Timer)芯片,用于处理计算机中的精确时间延迟。该芯片提供了 3个独立的16位计数器通道。每个通道可工作在不同的工作方式下, 并且这些工作方式均可以使用软件来设置。对于PC/AT及其兼容微机系统采用的是8254芯片。Linux 0.11操作系统只对通道0进行了重新设置,使得该计数器工作在方式3下,并且每间隔10毫秒发出一个信号以产生中断请求信号(IRQ0)。这个间隔定时产生的中断请求就是Linux 0.11内核工作的脉搏,它用于定时切换当前执行的任务和统计每个任务使用的系统资源量(时间)。

它能响应以下几种中断:

- ① 系统中断:IO APIC送来的系统中断请求,由IO APIC交给中断请求指定的目标处理器处理。

- ③ 本地中断:本地APIC产生的系统中断请求(计时器、LINT0/LINT1、性能监控、温度传感器、错误)。本地中断只能由该CPU处理。

从P6系列处理器开始,可以用特殊命令CPUID探测LAPIC的存在。如执行以下命令:

MOV EAX, 1CPUID

返回值在EDX寄存器中,当返回值第9位为1时,表示本地APIC存在,否则表示不存在。

下面简要介绍LAPIC的相关机制。

- (1)中断发布方式

本地APIC的中断发布方式分为静态和动态两种。

在静态方式下,根据重定向表中的信息,中断消息无条件地提交给某一个、几个或全部CPU;

在动态方式下,中断消息通过TPR (Task Priority Register)判断提交给最低优先权的CPU或焦点CPU(已接收或正在处理该中断)。

如果有多个CPU都执行相同优先级的进程,则必须采用仲裁(Arbitration)技术。

- (2)IA32_APIC_BASE寄存器 在模式专用寄存器(Model Specific Register)中,有一个IA32_APIC_BASE寄存器,其索引为1BH。CPU通过它来配置和控制本地APIC,例如允许、禁止本地APIC及设置本地APIC寄存器的基地址。IA32_APIC_BASE寄存器的格式如图24所示。

IA32_APIC_BASE寄存器

- E=1时,启用本地APIC。

- BSP=1时,此CPU为引导处理器;

- BSP=0时,为应用处理器。

在多CPU系统中,只能有一个引导处理器。

本地APIC寄存器是多个寄32_APIC_BASE指定,使用4KB存储器空间。

默认情况下,Intel将LAPIC的寄存器都映射到了物理地址0xFEE00000H。

本地APIC寄存器长度为32位、64位或者256位,所有地址边界按照16字节即128位为边界来访问。APIC地址映射见表如下

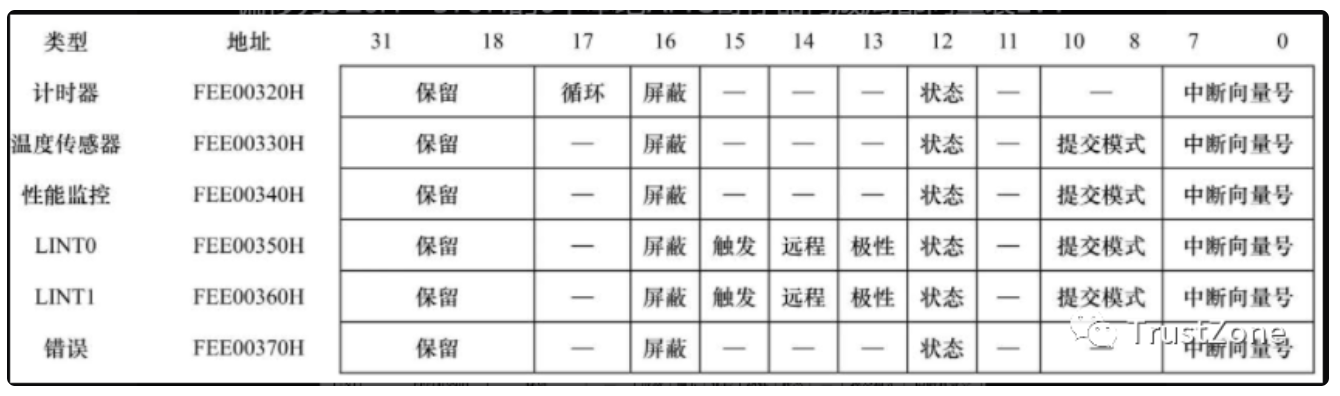

- (3)局部向量表

偏移为320H~370H的6个本地APIC寄存器构成局部向量表LVT(Local Vector Table) ,分别代表6种中断:

- 计时器中断、

- 温度传感器中断、

- 性能监控中断、

- LINT0中断、

- LINT1中断

- 错误中断。

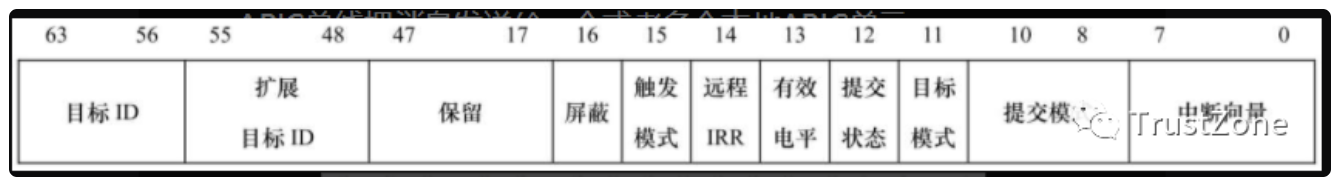

LVT中各个寄存器的格式如图25所示。

局部向量表LVT

- ① D16屏蔽位等于1时,对应的中断类型被屏蔽。

- ② D15触发位等于0时,边沿触发;等于1时,电平触发。

- ③ D14远程位等于1时,本地APIC收到中断请求。收到中断结束命令时,置为0。

- ④ D13极性位等于0时,LINT0/LINT1高电平有效;等于1时,低电平有效。

- ⑤ D12状态位等于1时,已经向CPU提交了中断请求,但CPU还没有应答。

一共有5种提交模式,见表如下。

局部中断提交模式

当提交模式等于000B时,CPU读取LVT中的低8位作为中断向量。

- (4)计时器中断

本地APIC中的计时器相关寄存器包括当前计数寄存器CCR、计数初值寄存器CR和除数寄存器DCR。

给CR寄存器赋值时,初始值装入CCR, CCR的值按一定频率递减,递减的频率等于系统总线频率除以刻度系数。刻度系数由DCR确定。CCR的值递减到0时,向处理器提交计时器中断。

当计时器采用单次模式(循环位等于0)时 ,提交计时器中断后,CCR的值一直保持为0,直到向CR寄存器装入新的初值。采用循环模式时,提交计时器中断后,CR的值重新到CCR,继续递减。计数过程中若初始计数寄存器被重置了,则将使用新的初始计数值,重新开始计数。

- (5)发布中断

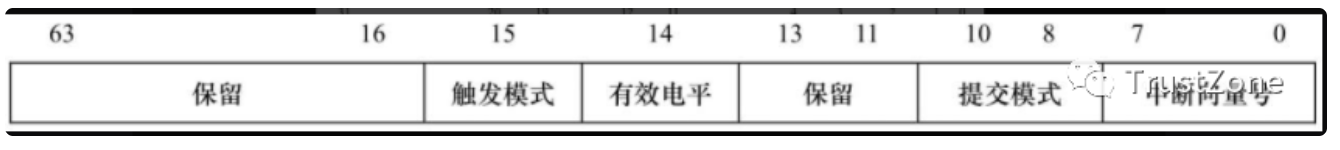

通过写入ICR寄存器,CPU可以向自身或者其他CPU发布处理器间中断IPI。ICR寄存器为64位,低32位的地址为FEE00300H,高32位的地址为FEE00310H。

ICR的主要功能包括:发送一个中断给另外一个处理器;允许处理器转发它收到的一个中断,但不对另一个处理器的请求提供服务 ;把处理器定向到中断本身,即执行一次自我中断;传送特定的IPI,比如启动IPI(SIPI)消息,到其他处理器。

ICR寄存器格式如图26所示。

ICR寄存器中,D13、D16、D17、D20~D55均保留。其他位含义如下:

- ① D7~D0表示中断向量号。

- ② D10~D8表示提交模式:

- a. 000(固定):传送向量域中指定的中断到目标处理器或者处理器组。

- b. 001(最低优先权):除了把中断传送给目的域中指定的目标处理器组中的优先级最低的处理器之外,其他同于固定模式。处理器传送最低优先权IPI的能力是与模型相关的,BIOS和操作系统软件应该避免它。

- c. 010(SMI):传送一个SMI中断给目标处理器或者处理器组。为了与未来兼容,该向量域应该设成00H。

- d. 011(保留)。e. 100(NMI):传送一个NMI中断给目标处理器或者处理器组。忽略向量信息。

- f. 101(INIT):传送一个INIT请求给目标处理器或者处理器组,使之执行一次初始化。作为这个IPI消息的结果之一,所有处理器都执行一次初始化。

- g. 110(未激活INIT的电平):发送一个同步消息给系统中的所有本地APIC,把它们的仲裁ID设置成它们的APIC ID。对于这个传送模式,电平标志必须设为0,触发模式标志设为1,目标指示应为10(Pentium 4和Intel Xeon处理器中不支持)。

- ③ D11用来指定接收目标的模式。D11=0时,使用物理目标模式;D11=1时,使用逻辑目标模式。

- ④ D12提交状态是只读位。等于1时,表示上一次发送的IPI消息还没有被目标CPU接收。

- ⑤ D14有效电平位。0表示无效电平;1表示有效电平。注意,无效电平可能是高电平或者低电平,有效电平也可能是高电平或者低电平。

- ⑥ D15触发模式位。0表示边沿触发;1表示电平触发。

- ⑦ D19~D18目标指示位。等于00时,表示根据目标ID确定发送目标;等于01时,发送给自己;等于10时,发送给所有CPU;等于11时,发送给所有CPU(自己除外)。

- ⑧ D64~D56表示消息的目标地址(Message Destination Address, MDA)。目标地址的表示方式包括两种:物理目标模式和逻辑目标模式。 下面介绍这两种模式。

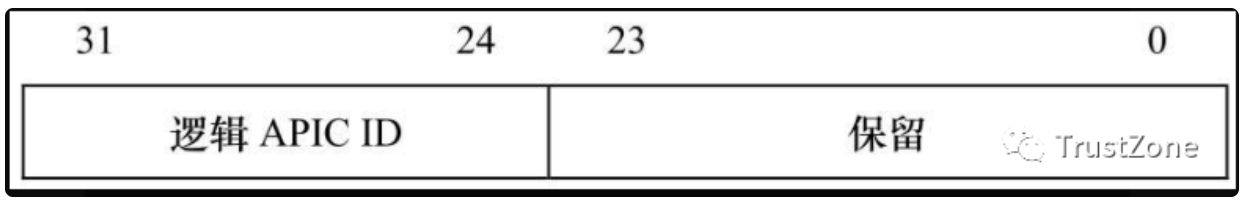

- 平面模式:本地APIC中的逻辑目标寄存器(Logic Destination Register, LDR)的高8位保存的是逻辑APIC标识,如图28所示。将逻辑APIC标识与MDA相与,如果得到的结果有任何一位等于1,那么这个APIC就接收IPI消息。在平面模式下,由于逻辑APIC标识有8个二进制位,支持最多8个CPU。

LDR格式

* 集群模式:Pentium CPU支持平面集群模式和层次集群模式,而Pentium 4只支持层次集群模式。在层次集群模式下,在CPU的外部还必须设置专门的集群管理设备,支持最多15个集群,每个集群上最多连接4个APIC,每个集群使用单独的APIC或系统总线。例9.14 假设三个CPU的logical模式配置为:CPU 1的LDR值为00000001b, CPU 2的LDR值为00010010b, CPU3的LDR值为00000100b,此时DFR的model值为0000b。IO APIC发出一条中断消息,其Destination Mode为1, Destination field值为00000001b。试分析该中断消息由哪些CPU接收。解答:三个LAPIC收到该消息后,CPU1、CPU3通过Destination field的高4位判断出该消息目的地为本簇,再将自身Logical APIC ID的低4位与Destination field低4位进行位与操作,CPU1与结果不为0,故最终CPU1接收该中断消息,CPU2、CPU3丢弃。

* 当第63~56位为FFH时,消息广播给所有的APIC。

* 对于Pentium 4和Intel Xeon处理器来说,一个单个目的(本地APIC ID从00H到FEH)或对所有APIC的广播(APIC ID是FFH)都可能在物理模式下指定。

* 对于P6系列和Pentium处理器来说,一个单个目的是由具有从0H到0EH的本地APIC ID的物理目的传送模式指定的,允许APIC总线中访问多达15个本地APIC。对所有本地APIC的广播,是由0FH指定的。

* a.物理目标模式。每一个本地APIC都有唯一的APIC ID。在ICR寄存器的第63~56位中指定一个APIC ID,消息将发送给与它相同的另一个APIC。

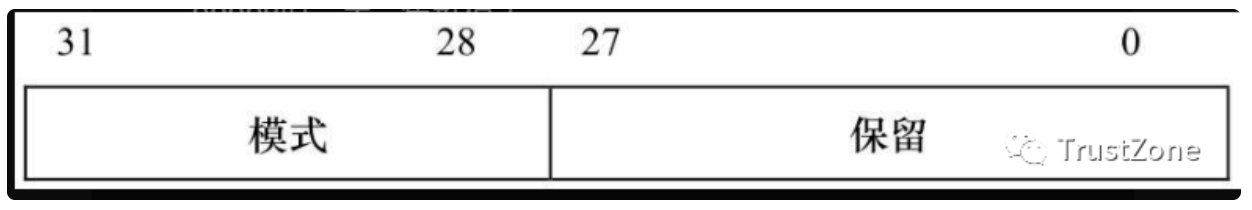

* b.逻辑目标模式。使用逻辑目标模式发送IPI时,目标APIC可以采用平面模式和集群模式。本地APIC中有一个目标格式寄存器(Destination Format Register, DFR),如图27所示,它的高4位(第31~28位)等于1111B时,表示平面模式;等于0000B时,表示集群模式。

- (6)处理中断 本地APIC接收到系统中断、处理器间中断、本地中断后,按照以下流程进行处理:

- ① 检查系统中断、处理器间中断消息中的目标地址与本地APIC是否匹配,如果不匹配,则忽略此消息。

- ② 检查中断消息中的提交模式,如果是NMI、SMI、INIT、ExtINT或者SIPI,那么由这个CPU直接处理;否则设置IRR寄存器(共256位)中的相应位。

- ③ 当有IRR和ISR寄存器中记录了中断请求时,按照中断请求的中断向量、任务优先权寄存器TPR、处理器优先权寄存器PPR进行优先级判断,交给某一个CPU处理。

- ④ 中断结束。提交模式为固定时,中断服务程序写LAPIC的EOI寄存器,将中断从ISR寄存器中清除,如果是电平触发,LAPIC向系统总线发送一条消息,表示中断处理结束。提交模式为NMI、SMI、INIT、ExtINT或者SIPI时,中断服务程序不需要写入EOI寄存器。

- (7)中断请求寄存器IRR和中断服务寄存器ISR

中断请求寄存器IRR共256位,地址为FEE00200H~FEE00270H;中断服务寄存器ISR也是256位,地址为FEE00100H~FEE00170H。

如果中断的提交模式为固定方式,中断请求寄存器IRR记录了本地APIC已经接收到的,但还没有指派给某一个CPU的中断。当CPU可以处理中断时,IRR中具有最高优先级的中断(即中断向量最大)对应的位被置为0,再将ISR中的对应位置为1。ISR中具有最高优先级的中断被发送给CPU进行处理。

在处理高优先级的中断时,如果发生了低优先级的中断,该中断的IRR位置为1。在高优先级的中断处理完成后,中断服务程序写入EOI寄存器,清除高优先级中断的ISR位。这时低优先级中断就会被处理。在处理某个优先级的中断时,如果发生了相同优先级的中断,该中断的IRR位置为1。前一个中断处理完成后,后面的中断才会被处理。在处理某个优先级的中断时,如果发生了更高优先级的中断,本地APIC可以向CPU发送中断,前一个中断被暂停,进入新的中断服务程序。这就是中断嵌套。

触发模式寄存器TMR也是256位。当中断的IRR位置为1时,边沿触发中断的TMR位清为0,电平触发中断的TMR位置为1。

- (8)优先权 中断优先权由它的中断向量号决定,中断优先权等于中断向量号除以16,即中断向量号的高4位,范围是2~15。注意,中断向量号0~31由CPU保留。

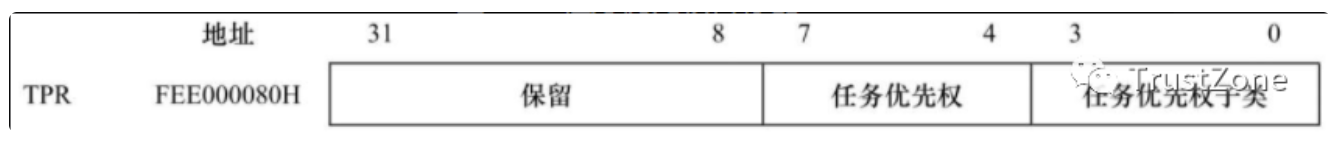

任务优先权寄存器TPR的地址为FEE00080H,格式如图29所示。

任务优先权寄存器TPR

处理器优先权寄存器PPR的地址为FEE000A0H,格式如图30所示。

处理器优先权寄存器PPR

中断优先权大于任务优先权时,中断才会被处理。

CPU通过设置任务优先权寄存器TPR,禁止低级别的中断。例如,把TPR中的第7~4位(任务优先权)设为15时,那么所有的外部中断(除NMI、SMI、INIT、ExtINT等)都会被屏蔽。而任务优先权设为0时,这些外部中断不被屏蔽。

处理器优先权寄存器不能被程序所修改,是一个只读寄存器。 它反映了当前CPU正在执行的程序的优先级。PPR的值是当前正在服务的中断向量和TPR二者之间较高的值。

设ISRV是ISR中被设置为1的最高优先权的中断向量,ISR中所有位等于0时,ISRV等于0。PPR按照以下公式来确定:

IF TPR[7∶∶4] ≥ ISRV[7∶∶4]THEN PPR[7∶∶0]=TPR[7∶∶0]ELSE PPR[7∶∶4]=ISRV[7∶∶4]; PPR[3∶∶0]=0

- (9)消息信号中断

PCI 2.2规范中引入了消息信号中断MSI(Message Signaled Interrupts)。PCI设备可以用两种方法向CPU发出中断请求:

- ①用设备的一个引脚发送中断请求信号;

- ②用MSI向处理器传送中断请求。

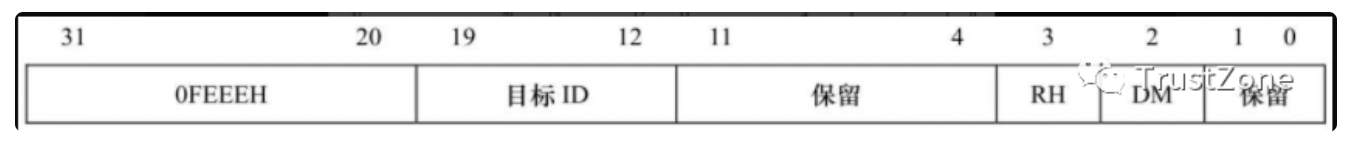

采用MSI向CPU发送中断请求时,PCI设备发起一个PCI写操作,向一个特殊的地址写入一个特定数据。地址的格式如图9-31所示,数据的格式如图32所示。

MSI地址格式

MSI数据格式

在地址中,目标ID指定了MSI消息发送给哪一个(组)CPU, RH说明是否要把消息发送给一组中具有最低优先权的CPU, DM则指示采用物理目标模式或者逻辑目标模式。

在数据部分,触发模式有边沿触发和电平触发两种,后者又分高电平有效和低电平有效。提交模式分为固定、最低优先级、SMI、NMI、INIT、ExtINT等几种。

3 IO APIC

IO APIC用来替代传统的8259中断控制器,一般集成在ICH芯片组中。

ICH(I/O controller hub意思是“输入/输出控制器中心”,负责连接PCI总线,IDE设备,I/O设备等,是英特尔的南桥芯片系列名称。

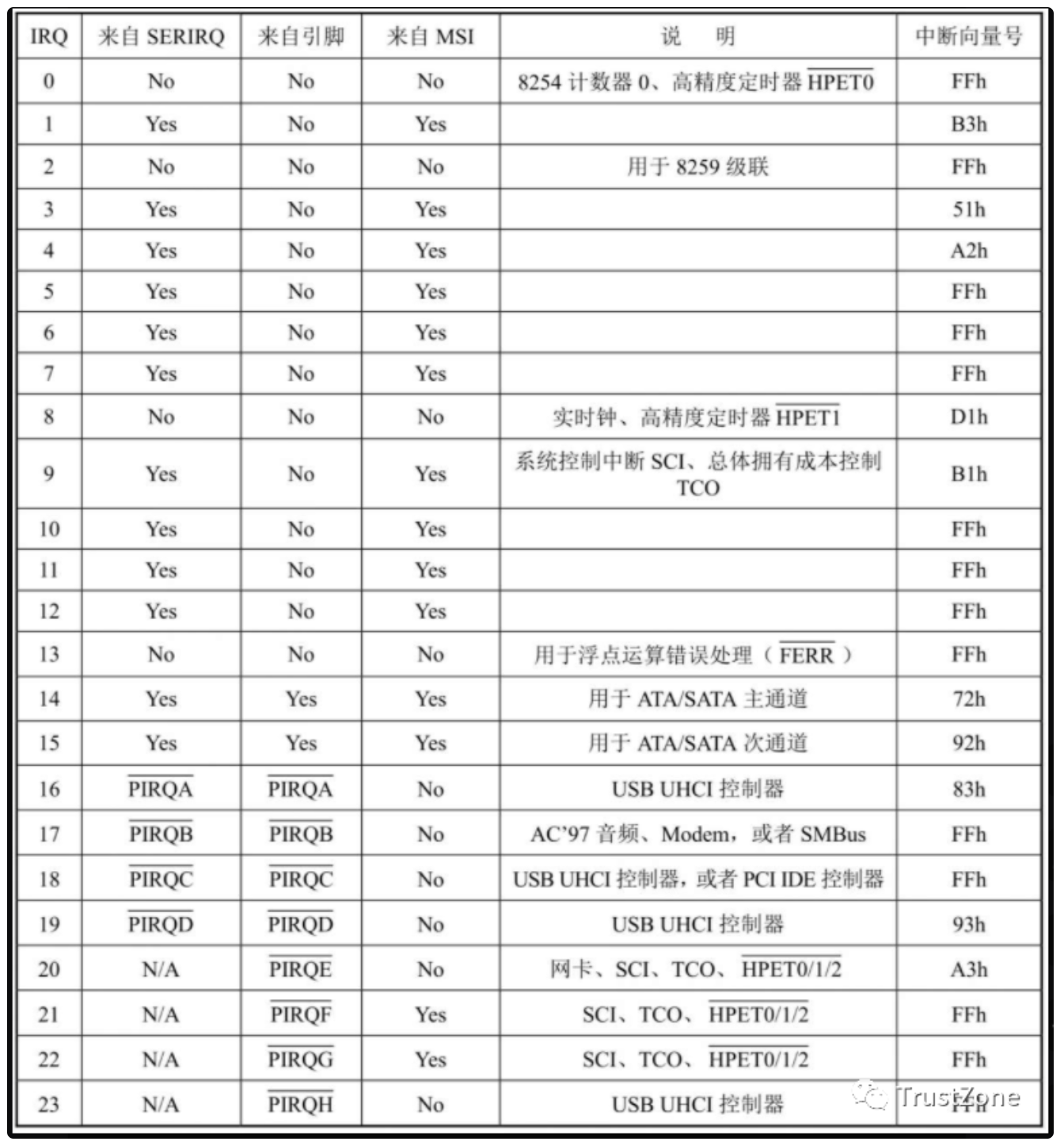

表7中列出了IO APIC管理下每个中断源对应的中断向量。

表七:每个中断源对应的中断向量

和8259相比,IO APIC能支持24个中断源,不需要中断应答周期,可以将中断请求发送给某一个指定的CPU。

IO APIC的中断优先权由中断向量来确定,与中断源(IRQ)无关。 (所以软件编程的时候这个中断向量的设置很需要注意,也更加体现了APIC的灵活性)

系统中最多可以拥有8个IO APIC,每一个IO APIC都分别有自己的输入编码,加起来一台PC上会有上百个IRQ可供设备中断使用。

IO APIC和LAPIC共同起作用,如果系统中没有IO APIC,那么LAPIC就没有用处,此时操作系统会使用8259。Intel系统中常用82093AA芯片来作为IO APIC。

- (1)IO APIC寄存器地址 Intel系统中,IO APIC默认映射到物理地址FEC00000H。IO APIC一共有4个寄存器地址,见表8。

表八:IO APIC的寄存器

一共有64个32位内部寄存器,其索引为0~63。内部寄存器索引见表9。

表九:IO APIC内部寄存器

- (2)重定向表

中断重定向表中的每一项都有可以被单独编程,用来指明中断向量和优先级、目标处理器及选择处理器的方式。

重定向表中的信息用于把每个外部IRQ信号转换为一条消息,然后通过APIC总线把消息发送给一个或者多个本地APIC单元。

重定向表的格式如图33所示。

表十:重定向表

目标ID确定哪一个(组)CPU处理这个中断。目标模式等于0时,即物理目标模式,目标ID的第59~56位表示某一个CPU的APIC ID;等于1时,即逻辑目标模式,目标ID的第53~56位与CPU中的逻辑APIC标识匹配,确定目标。

向CPU发送中断时,扩展目标ID(8位)被放置在地址的第11~4位。地址格式如上图所示。

屏蔽位等于1时,这个中断不会向CPU发送。触发模式分为边沿触发(D15=0)和电平触发(D15=1)两种,后者又分高电平有效(D13=0)和低电平有效(D13=1)。

在电平触发时,远程IRR位有效。等于1时,表示CPU的本地APIC已接受此中断,收到本地APIC发送的EOI后,将此位清0。相对于本地APIC和CPU核心而言,IO APIC和本地APIC之间的传递是远程的。

提交状态等于1时,表示中断消息已产生,但还没有发送给本地APIC。提交模式分为固定(000B)、最低优先级(001B)、SMI(010B)、NMI(100B)、INIT (101B)、ExtINT(111B)等几种。

最低优先级表示把这个中断按照目标ID提交给PPR最低的CPU。重定向表的第7~0位表示该中断对应的中断向量号,在表7中列出了某系统中各个IRQ对应的中断向量号。

以上就是对x86的中断有了一个简单的了解,后续我们接着来看看ARM的GIC。

这个名称的由来,是由于绘制架构图时所派生出来的称呼,第一次被提到这名词时是在1991年采用PCl Local Bus架构时。在Intel,PCl规格的创始者视PCI总线为整个PC平台架构的正中央。北桥芯片将PCl总线主干延伸至北边,以支持CPU、存储器或缓存(Cache)、以及其他攸关性能的功能。反之,南桥芯片将PCI总线主干延伸至南边,并桥接起比较非攸关性能的I/O功能,例如磁盘接口等、音效等。CPU位于架构图的正北方,它透过较高速的北桥芯片链接北边的系统设备,而北桥则透过较慢速的南桥芯片连接南边的其他系统设备。虽然现今PC平台架构已将PCl总线主干取代,换上更快的I/O主干,但“桥”的传统名称仍然延续使用。北桥(英语:Northbridge)是基于Intel处理器的个人电脑主板芯片组两枚芯片中的一枚,北桥用来处理高速信号,例如中央处理器、存储器、显卡(PCI Express接口或AGP接口),还有与南桥之间的通信。北桥芯片位置刚好跟南桥芯片位置相反,它是靠近CPU部分,被散热片覆盖的大的那块芯片,主要功能是负责控制、连接和处理CPU与内存、与南桥通信。北桥芯片是主板的关键芯片,负责管理二级高速缓存,内存的类型和最大容量都由它决定,所以一般主板命名都是用北桥芯片的型号。有一些北桥会集成内置显示核心(如Intel GMA),也支持AGP或PCl Express接口。集成显示核心的北桥若侦测到已安装的PCle/AGP显卡,会停止其GPU功能,但有些北桥可以允许同时使用集成式显卡和安装外加显卡,作为多显示输出。英特尔在第一代Core i7中把存储器控制器集成到了CPU,北桥的功能只剩下连接高速设备(如显卡),此时Intel的南桥称为IOH (Io Controller Hub)。从LGA 1156、LGA 2011开始,Intel处理器集成了北桥(存储器控制器、高速PCl Express控制器和Intel HDGraphics),主板上只剩下南桥,Intel将其称为平台路径控制器(PCH)。

4、APIC与8259A

APIC全称是Advanced Programmable Interrupt Controller,高级可编程中断控制器。

它是在奔腾P54C之后被引入进来的。在现在的计算机它通常由两个部分组成,分别为LAPIC(Local APIC,本地高级可编程中断控制器)和IOAPIC(I/O高级可编程中断控制器)。

LAPIC在CPU中,IOAPIC通常位于南桥 。

APIC是在PIC (Programmable Interrupt Controller) 的基础上发展而来的。

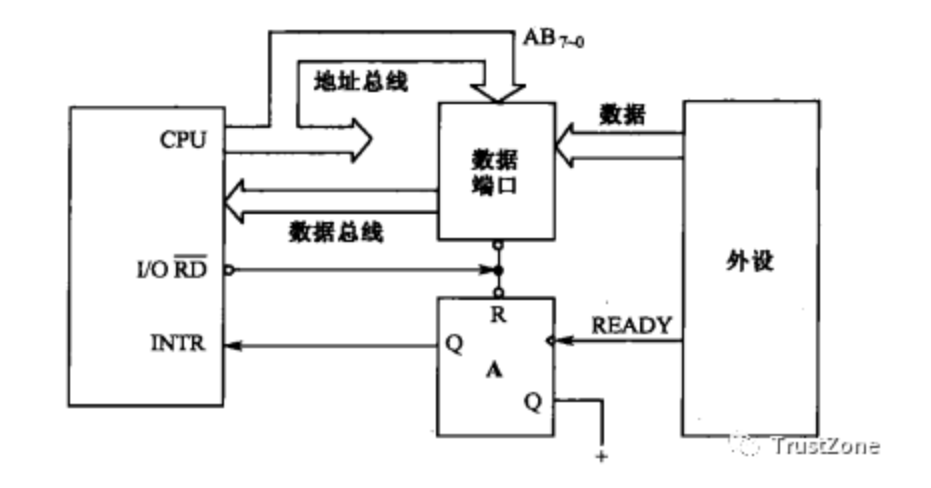

在传统的单处理器的PC-AT 兼容的机器,通常使用8259A双片级联组成Legacy中断控制器(如下图所示)。一共可以连接15个设备(有一个管脚被用于串联另一片8259)。PIC的优先级规则比较简单,0号管脚的优先级最高。

PIC可以通过ICW(Initialization CommandWord)编程设置起始的Vector号。

PIC在单个CPU的环境下工作的挺好,可是当系统越来越复杂出现了多个CPU的情况,它就没法很好的工作了。这种情况下所有的中断都会丢给主8259连接的那个CPU,那么这个CPU就要处理所有的中断,性能上就会有影响。在一个多处理器的系统,任何一个CPU都应该能够响应来自任何设备的中断,这种就是所谓的对称式多重处理(Symmetric Multiprocessing)

IOAPIC: IOAPIC的主要作用是中断的分发。最初有一条专门的APIC总线用于IOAPIC和LAPIC通信,在Pentium4 和Xeon 系列CPU出现后,他们的通信被合并到系统总线中。

Virtual Wire Mode:虚拟接线模式,该模式主要是为了向前兼容,可以理解为就是PIC。在这种模式下,IOAPIC会把8259A的模拟硬件产生的中断信号直接送给BSP。

如上图所示,每个CPU/Core中都有一个LAPIC。相比较于IOAPIC, LAPIC会更复杂一些,它不仅能够处理来自IOAPIC的中断消息,它还可以处理IPI(Inter-Processor Interrupt Messages),NMI,SMI和Init消息。

LAPIC 默认使用基地址FEE00000h开始的4KB空间用来访问内部寄存器,从Pentium Pro开始引入一个APIC_BASE 的MSR,可以用来设置基地址在任何4KB对齐的64GB内存地址空间。IRR:LAPIC已经收到中断但是还未提交CPU处理。ISR:CPU已经开始处理中断,但是尚未完成。TMR(Trigger Mode Register):中断的触发模式。EOI软件写入表示中断处理完成。

-

处理器

+关注

关注

68文章

19404浏览量

230969 -

温度传感器

+关注

关注

48文章

2974浏览量

156331 -

寄存器

+关注

关注

31文章

5363浏览量

121029 -

中断控制器

+关注

关注

0文章

59浏览量

9480 -

DCR

+关注

关注

1文章

54浏览量

18851

发布评论请先 登录

相关推荐

8259A芯片是一种什么类型的芯片?从硬件看中断之8259A

从硬件看什么是中断?从硬件看中断之8088

干货!Android之蓝牙驱动开发经验

Windows环境下硬件中断的性能分析

基于APIC时钟的嵌入式Linux内核实时化研究

一个关于Linux中断的问题:硬件处理,初始化和中断处理

linux中断处理之IRQ中断

实际中断处理

STM32之FreeRTOS:(一) 中断配置和临界段的使用

干货!从硬件看中断之APIC

干货!从硬件看中断之APIC

评论