对于通信、雷达等无线电行业相关的朋友,我相信大家对于窄带系统的设计,必然是轻车熟路,如数家珍。尤其是围绕FPGA+AD/DA的数字收发的架构设计,那估计更是心中有笔,信手拈来了。 传统的FPGA+AD/DA独立器件搭建的数字系统我就不过多的介绍,今天我主要给大家讲讲RF-FPGA芯片给整个窄带系统带来的诸多优势,真的是不用不知道,用了都说好!!!

1)高速数字处理

早先的无线电接收系统,利用模拟混频器和级联数字下变频器(DDC)的设计结构,将信号降频至基带以供处理,该系统中会涉及到大量硬件(模拟混频)和电源(模拟域和ASIC/FPGA中的DDC域)。 RF-FPGA的出现,使得DDC可以在RF-FPGA内部的RFADC硬核高速运行,处理的功效要高得多。

2)通过AXI-STEAM接口互联

国产新一代RF-FPGA集成了RFADC,不需要ADC和FPGA之间的高速JESD204或者LVDS接口。直接通过内部并行接口AXI-STEAM接口互联,最大500MHz时钟周期,256位的并行接口。 整个数字接收系统节省了大量的功耗和PCB面积,同时也减小了JESD204的接口的延时。

3)可扩展的硬件设计平台

在硬件设计方面,数字DDC的使用提供了更高的灵活性。系统设计人员现在可以平台化ADC和FPGA相关硬件设计,然后只需进行细微的变更,重新配置系统软件便可适应不同的带宽,这也是未来软件无线电的主要方向。 例如,一个无线电系统既可设计为全带宽射频直采ADC系统,也可设计为中频采样ADC系统。唯一的系统变更将是在RF侧,针对IF ADC可能需要增加极少的混频。 上述绝大部分系统变更都可以在软件中进行,ADC + FPGA硬件设计可以基本保持不变,FPGA工程师配置ADC以支持新的带宽。这就形成了一个标准平台化硬件设计,其可以适用于许多平台,软件要求是其唯一变数。

4)通信接收机设计更加灵活

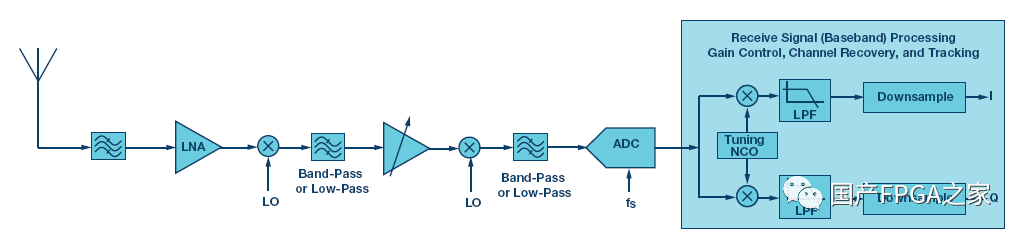

一个非常常见的ADC使用案例是通信接收机系统设计。关于软件定义无线电(SDR)和采用ADC的通信接收机已有许多文献,小弟这里就不展开讨论。图1为较早一代无线电接收机的功能框:

图1-用于无线电的宽带数字接收机 无线电接收机的一般规格要求ADC的噪声频谱密度(NSD)至少为153 dBFS/Hz或更佳。众所周知,NSD与ADC的SNR存在如下关系: NSD = SNR + 10 log10 (Fs ÷ 2) 其中:NSD为ADC噪声谱密度、SNR的单位为dBFS、Fs为ADC采样率

4.1 常规软件无线电设计

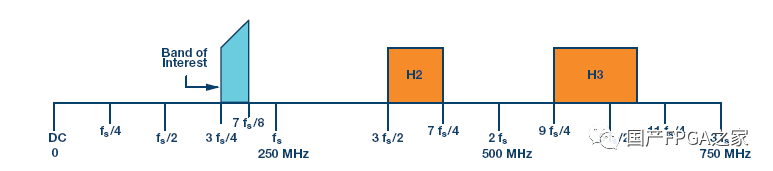

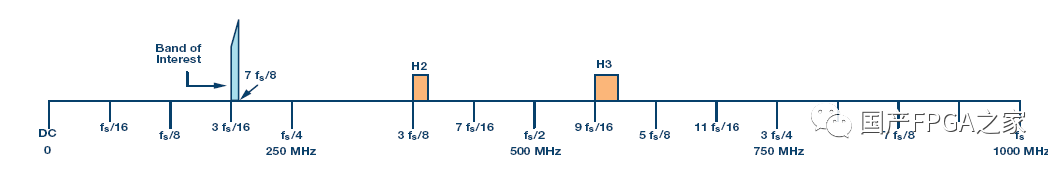

为了正确地对50MHz频段进行数字化,ADC 将需要至少5倍的采样带宽,即至少约250MHz。将这些数值代入上式,ADC达到–153dBFS/Hz NSD要求所需的SNR约为72dBFS。 图2显示了利用250MSPS ADC对50MHz频段有效采样所采用的频率规划,该图还显示了二次和三次谐波频段的位置。

图2-采用250MSPS ADC的50MHz宽带无线电的频率规划

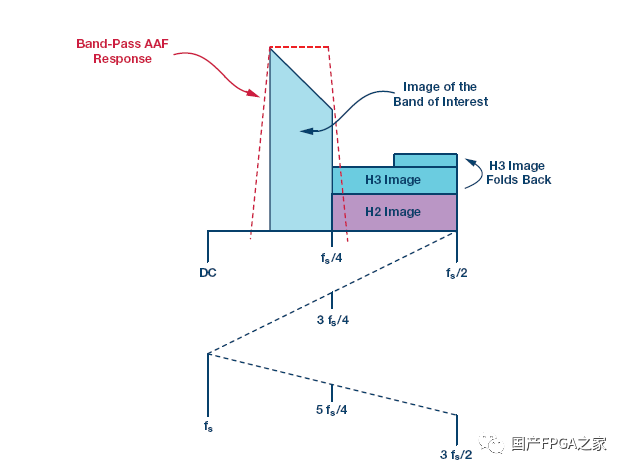

ADC采样的频率都会落在ADC的第一奈奎斯特(DC–125MHz)频段。这种现象称为混叠,因此这些频率包括目标频段、折回或混叠到第一奈奎斯特频段的二次和三次谐波,如图3所示,说明如下:

图3-显示在第一奈奎斯特区中的可用频段,含二次和三次谐波

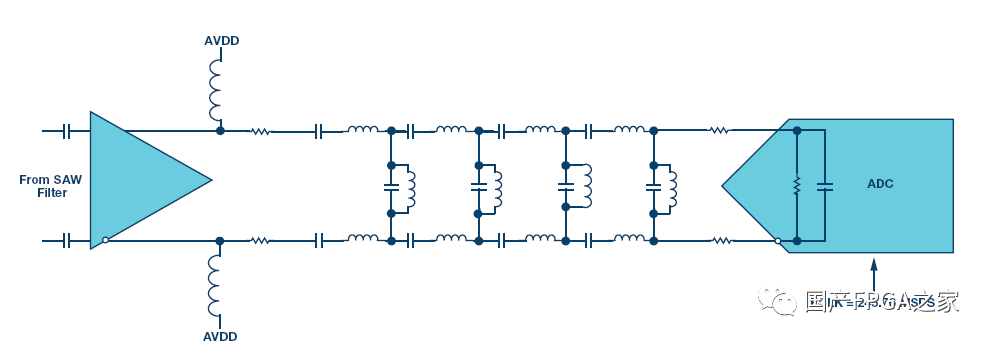

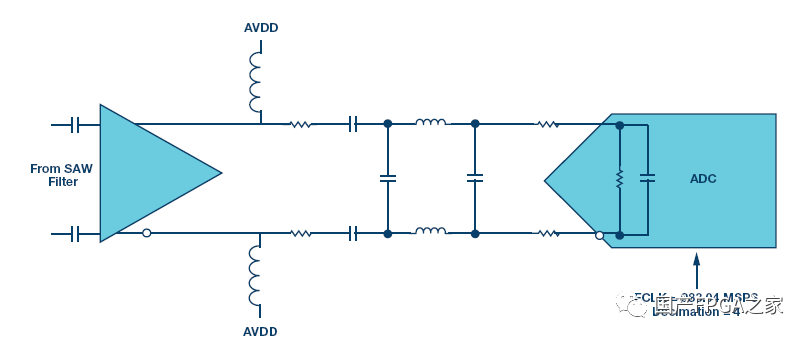

除NSD规格外,GSM、LTE和LTE-A等蜂窝通信标准还对SFDR (无杂散动态范围)有其它严格要求,这给前端设计带来了很大压力。对目标频段中的信号进行采样时,前端能够衰减干扰信号。 常规无线电前端设计的SFDR规格,即抗混叠滤波器要求很难达到。满足SFDR要求的最佳抗混叠滤波器(AAF)解决方案是采用带通滤波器。 通常,此类带通滤波器为五阶或更高阶。一款可以满足此类应用的SNR (或NSD)和SFDR要求的合适ADC是16位250 MSPS模数转换器AD9467,采用AD9467的蜂窝无线电应用前端设计将图4所示:

图4-包括放大器、抗混叠滤波器和250 MSPS ADC的前端设计

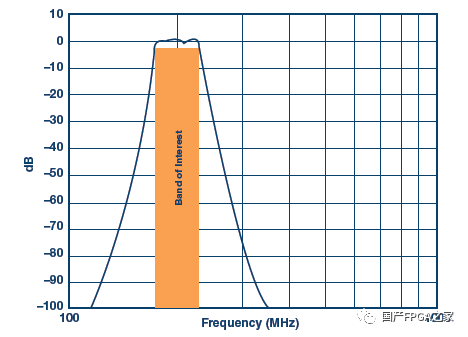

满足SFDR要求的AAF的频率响应如图5所示:

图5-包括放大器、抗混叠滤波器和250 MSPS ADC的带通响应

此系统的实现不是不可能,但存在很多设计难题。因为带通滤波器涉及到大量器件,是最难实现的滤波器之一。而且相关器件的选择非常重要,任何不匹配都会导致ADC输出中出现不需要的杂散(SFDR)。 除了非常复杂以外,任何阻抗不匹配都会影响滤波器的增益平坦度。为了优化该滤波器设计以满足带通平坦度和阻带抑制要求,需要做相当多的设计工作。 虽然这种无线电设计的前端实现很复杂,但它确实有效,然而,系统实现因为下列原因而变得复杂:

滤波器设计;

FPGA必须提供专用JESD204B/LVDS端口来捕捉数据,这会使PCB设计复杂化;

FPGA还需要留出一些处理能力来进行数字信号处理。

4.2 RF-FPGA简化并加速设计

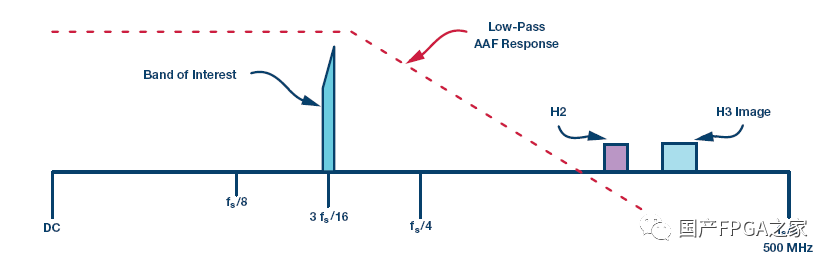

RF-FPGA中RFADC硬核采样频率最大能到4.6GHz,对于50MHz带宽信号,利用过采样技术,然后抽取平均降低底噪,以改善动态范围。 对系统设计人员来说,这意味着实现起来很简单,并可获得其它灵活性。由于该ADC的采样频率(1GHz)是上述例子(250MHz)的4倍,RF采样ADC奈奎斯特区的频率规划要简单得多,如图6所示:

图6-采用1GSPS ADC的50MHz宽带无线电的频率规划

从频率规划可知,它实现起来要比图2所示的设计简单得多。AAF要求也有所降低,如图7所示。这种方法的思想是使用简单的模拟前端设计,而把数字处理模块留在RF直采ADC内以执行繁重的信号处理。

图7-1GSPS ADC的AAF

过采样的好处是将该频率规划扩展到整个奈奎斯特区,即比250MSPS奈奎斯特区大4倍的区域。这样就大大降低了滤波要求,一个简单的三阶低通滤波器就足够,而无需250MSPS ADC方案所用的带通滤波器。采用RF采样ADC的简化AAF实现方案如图8所示:

图8-包括放大器、抗混叠滤波器和1GSPS ADC的前端设计

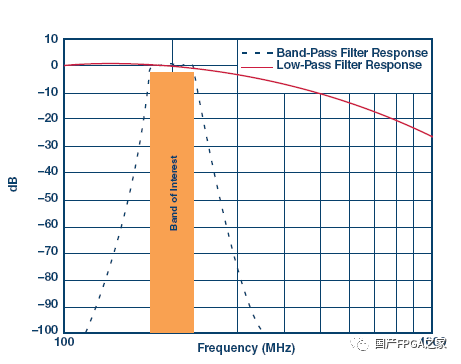

图9所示为上述系统低通滤波器响应性能,同时显示了带通滤波器以作比较。

图9-250MSPS ADC和1GSPS ADC的AAF比较

从上述AAF对比结果来看,低通滤波器的带通平坦度更佳,而且就器件不匹配而言,1GSPS ADC系统更容易管理,其阻抗匹配也更容易实现。 此外,由于器件数量更少,系统成本也更低,简化的前端设计可缩短设计时间。同时每4倍过采样率时,通过平均还可以获得6dB的额外处理增益,提高一位有效位数。

战术总结

随着RF-FPGA的到来,必然会给传统的窄带、宽带的收发系统设计带来变革,小弟私以为,对于新技术和新产品的到来,我们要时刻保持谦虚包容的态度,积极地去学习和接纳。毕竟身处在这么卷的行业赛道里,不努力学习,可能明天就要到别人的厂子里应聘保安了。

审核编辑:汤梓红

-

FPGA

+关注

关注

1630文章

21796浏览量

605593 -

接口

+关注

关注

33文章

8691浏览量

151796 -

adc

+关注

关注

99文章

6533浏览量

545597 -

RF

+关注

关注

65文章

3057浏览量

167306 -

窄带系统

+关注

关注

0文章

2浏览量

1349

原文标题:窄带系统设计中,RF-FPGA优势何在?

文章出处:【微信号:国产FPGA之家,微信公众号:国产FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于全光矢量调制技术的超宽带光载无线系统及其关键技术分析介绍

GPS芯片的关键技术是什么

什么是RF MEMS?有哪些关键技术与器件?

FPGA+DSP导引头信号处理中FPGA设计的关键技术

FPGA+DSP导引头信号处理中FPGA设计的关键技术

基于国产RF-FPGA宽带射频采集卡

数字收发组件的关键技术 RF-FPGA芯片在窄带系统设计中的优势

数字收发组件的关键技术 RF-FPGA芯片在窄带系统设计中的优势

评论