PCIe最初被称为HSI(用于高速互连),并在最终确定其PCI-SIG名称PCI Express之前,将其名称更改为3GIO(第三代I / O)。名为阿拉帕霍工作组(AWG)的技术工作组制定了该标准。对于初稿,特设工作组只包括英特尔工程师; 随后特设工作组扩大到包括行业伙伴。PCI Express是一项不断发展和完善的技术.

“速度得用金钱来换,因此我们在迈向更高信号速率的同时,会看到有多少人愿意为此付出代价,以及他们会怎么做。”好消息是,PCIe将按照时程在年底完成0.71版的批准,将提供高达256GB/s 的速率;这距离16 GT/s速率的4.0版PCIe问世还不到两年。加速PCIe发展蓝图的主要推手是云端运算需求;而PCIe以往是每3~4年,甚至是7年会将数据传输速率提升一倍。数据中心网络需要更快的速度以过渡至800Gbit以太网络,而数量越来越庞大的深度学习加速器,也感觉它们需要更高速度.

浅谈PCIe传输速率和有效带宽计算方式

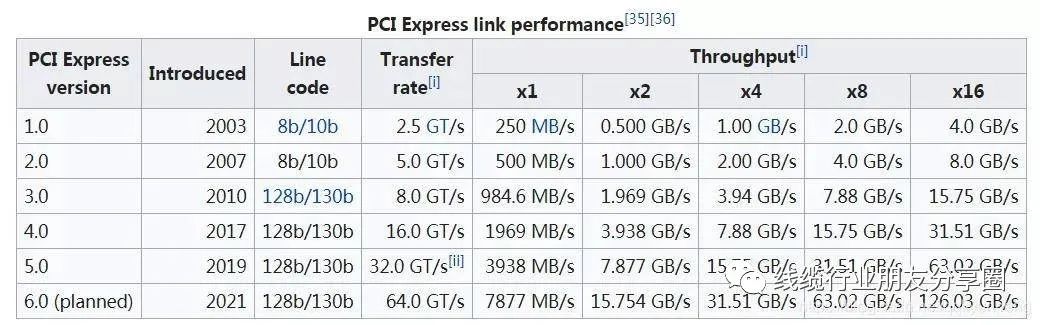

PCIe是串行总线,PCIe1.0的线上比特传输速率为2.5Gb/s,物理层使用8/10编码,即8比特的数据,实际在物理线路上是需要传输10比特的,因此:

PCIe1.0 x 1的带宽=(2.5Gb/s )/ 10bit =250MB/s

这是单条Lane的带宽,有几条Lane,那么整个带宽就是250MB乘以Lane的数目。

PCIe2.0的线上比特传输速率在PCIe1.0的基础上翻了一倍,为5Gb/s,物理层同样使用8/10编码,所以:

PCIe2.0 x 1的带宽=(5Gb/s )/ 10bit = 500MB/s

同样,有多少条Lane,带宽就是500MB/s乘以Lane的数目。

PCIe3.0的线上比特传输速率没有在PCIe2.0的基础上翻倍,不是10Gb/s,而是8Gb/s,但物理层使用的是128/130编码进行数据传输,所以:

PCIe3.0 x 1的带宽=(8Gb/s)/ 8bit = 1GB/s

同样,有多少条Lane,带宽就是1GB/s乘以Lane的数目。

由于采用了128/130编码,128比特的数据,只额外增加了2bit的开销,有效数据传输比率增大,虽然线上比特传输率没有翻倍,但有效数据带宽还是在PCIe2.0的基础上做到翻倍。

这里值得一提的是,上面算出的数据带宽已经考虑到8/10或者128/130编码,因此,大家在算带宽的时候,没有必要再考虑线上编码的问题了。

和SATA单通道不同,PCIe连接可以通过增加通道数扩展带宽,弹性十足。通道数越多,速度越快。不过,通道数越多,成本越高,占用更多空间,还有就是更耗电。因此,使用多少通道,应该在性能和其他因素之间进行一个综合考虑。

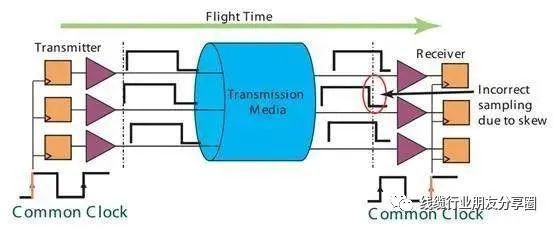

PCIe是从PCI发展过来的,PCIe的”e”是express的简称,快的意思。PCIe怎么就能比PCI快呢,因为PCIe在物理传输上,跟PCI有着本质的区别。PCI使用并口传输数据,而PCIe使用的是串口传输。PCI并行总线,单个时钟周期可以传输32bit或者64bit,怎么就比不了你单个时钟周期传输1个bit数据的串行总线呢。在实际时钟频率比较低的情况下,并口因为可以同时传输若干比特,速率确实比串口快。随着技术的发展,数据传输速率要求越来越快,要求时钟频率也越来越快,但是,并行总线时钟频率不是想快就能快的。如下图所示:

在发送端,数据在某个时钟沿传出去(左边时钟第一个上升沿),在接收端,数据在下个时钟沿(右边时钟第二个上升沿)接收。因此,要在接收端能正确采集到数据,要求时钟的周期必须大于数据传输的时间(从发送端到接收端)。受限于数据传输时间(该时间还随着数据线长度的增加而增加),因此时钟频率不能做得太高。另外,时钟信号在线上传输的时候,也会存在相位偏移(clock skew ),影响接收端的数据采集。

PCIe使用串行总线进行数据传输就没有这些问题。它没有外部时钟信号,它的时钟信息通过8/10编码或者128/130编码嵌入在数据流,接收端可以从数据流里面恢复时钟信息,因此,它不受数据在线上传输时间的限制,你导线多长都没有问题,你数据传输频率多快也没有问题;没有外部时钟信号,自然就没有所谓的clock skew问题.

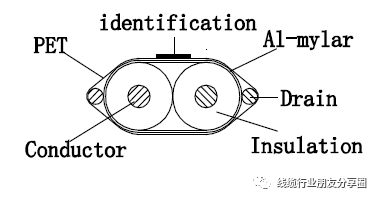

浅谈PCIe线材结构

PCIe为串行,通过使用差分信号传输(differential transmission),信号完整性理论之差分讯号;采用双通道技术,在传输模式上,PCI-Express采用与全双工通信技术类似的双通道传输模式,在速度方面,PCI-Express v1.0a 为每个通道提供了2.5Gb/s的传输速率,随着版本的不同,面向PCI Express扩展卡应用的线缆组件可提供PCIe X4、X8和X16等规格,该系列线缆组件包含MiniSAS、SATA、QSFP +和SPF +等高速线缆。PCIE物理层实现了一对收发差分对,可以实现全双工的通讯方式,目前主要的PCIE结构主要是SAS结构,线材选用CAT A ,B,C ,D,E结构,根据测试的参数要求,设计符合不同规范的参数。

PCIe Spec只是规定了物理层需要实现的功能、性能与参数等,置于如何实现这些却并没有明确的说明。也就是说,厂商可以根据自己的需要和实际情况,来设计PCIe的物理层结构来保证功能即可!

-

带宽

+关注

关注

3文章

1054浏览量

43649 -

传输

+关注

关注

0文章

158浏览量

28549 -

PCIe

+关注

关注

16文章

1496浏览量

89111

发布评论请先 登录

频宽飙升到1TB/s! PCIe 8.0规范0.5版正式发布,2028年最终定案

如何评估SDRAM的有效带宽

深入剖析DS80PCI102:PCIe链路扩展的得力助手

更宽的 LoRa 带宽是如何提升数据速率的?

PCIe 6.0 SSD主控芯片狂飙!PCIe 7.0规范到来!

PCIe传输速率和有效带宽科普

PCIe传输速率和有效带宽科普

评论