近日,“2023功率与光电半导体器件设计及集成应用论坛”于西安召开。论坛由第三代半导体产业技术创新战略联盟(CASA)指导,西安交通大学、极智半导体产业网(www.casmita.com)、第三代半导体产业主办,西安电子科技大学、中国科学院半导体研究所、第三代半导体产业技术创新战略联盟人才发展委员会、全国半导体应用产教融合(东莞)职业教育集团联合组织、西安和其光电股份有限公司等单位协办。

期间,“平行论坛1:功率半导体器件设计及集成应用”上,西安卫光科技有限公司器件研究中心工程师李朴带来《600V超结MOSFET器件研究》的主题报告。详细分享了600V 超结MOSFET研究过程与成果。

报告中介绍,随着功率半导体应用领域逐渐扩大,当应用在计算机和航空电子等领域中时,低导通压降能够缩小整机的冷却系统,从而降低整机尺寸和成本,所以用户对器件的导通电阻提出了更高的要求。

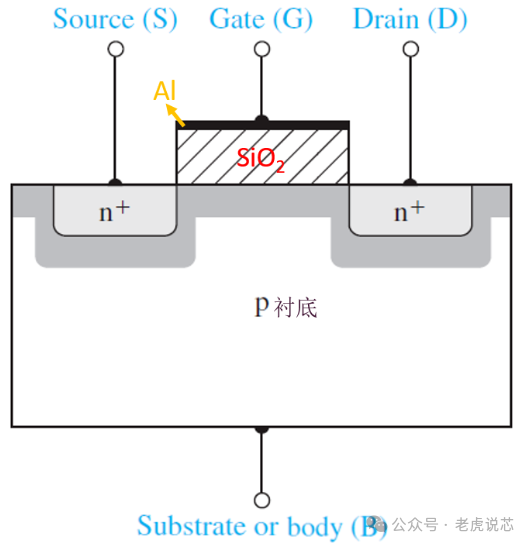

而传统功率MOSFET中击穿电压与导通电阻的关系,始终被限制在了“硅限”2.5次方,难以克服。为了能突破发展瓶颈,“超结理论”应运而生,极大的推动了功率半导体的发展。基于超结理论的器件能够在保证击穿电压的同时,进一步提高N柱区掺杂浓度,从而减小通态电阻,将击穿电压与通态电阻的限制关系优化到1.3次方。

报告对SJMOS的基本工作原理进行分析,进而利用仿真软件对600V SJMOS的元胞区工艺进行工艺仿真,并对其击穿电压、导通电阻、阈值进行了优化。最终得到元胞区仿真击穿电压722V,阈值电压3.04V,特征导通电阻27mΩ•cm2。

-

电阻

+关注

关注

86文章

5521浏览量

172120 -

MOSFET

+关注

关注

147文章

7181浏览量

213432 -

功率半导体

+关注

关注

22文章

1161浏览量

43003

原文标题:卫光科技李朴:600V超结MOSFET器件研究

文章出处:【微信号:第三代半导体产业,微信公众号:第三代半导体产业】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

储能柜400V升压600V变压器 额定电压400V变600V 使用条件:室内室外

600V CoolMOS S7T集成温度传感器介绍

评估超结功率 MOSFET 的性能和效率

锐骏200V低压和600V高压MOS对于电机控制和电源管理

适用于600V GaN功率级的QFN12x12封装的热性能

LN4203南麟600V 半桥栅极驱动器

英飞凌推出600V CoolMOS 8 SJ MOSFET系列

新品 | 600V CoolMOS™ 8 SJ MOSFET系列

PCIM2024论文摘要|新型400V SiC MOSFET用于高效三电平工业电机驱动

英飞凌推出全新600 V CoolMOS™ 8 SJ MOSFET系列, 适用于高成本效益的先进电源应用

突破碳化硅(SiC)和超结电力技术的极限

卫光科技李朴:600V超结MOSFET器件研究

卫光科技李朴:600V超结MOSFET器件研究

评论