导读

三十年前,CPU 和其他专用处理器几乎处理所有计算任务。那个时代的显卡有助于加快 Windows 和应用程序中 2D 形状的绘制速度,但绝对没有其他作用。快进到今天,GPU 现已成为整个行业最具主导地位的芯片之一。

具有讽刺意味的是,图形芯片硬件的唯一功能的日子已经一去不复返了,图形高性能计算和机器学习在很大程度上依赖于不起眼的 GPU 的处理能力。与我们一起探索这款单芯片如何从一个不起眼的像素推动器演变成一个强大的浮点计算引擎。

***01. ***一开始CPU统治一切

让我们首先回到 20 世纪 90 年代末。高性能计算领域,无论是使用超级计算机进行科学研究、标准服务器上的数据处理,还是工作站上的工程和设计任务,都完全依赖于两种类型的 CPU:为单一目的而构建的专用处理器或现成的处理器,AMD、IBM 或 Intel 的货架芯片。

以 ASCI RED为例。1997 年,它是最强大的超级计算机之一,由 9,632 个 Intel Pentium II Overdrive CPU 组成(下图)。每个单元的运行频率为 333 MHz,该系统的理论峰值计算性能略高于 3.2 TFLOPS(每秒万亿次浮点运算)。

由于我们将在本文中经常提到这个指标,因此值得花点时间来解释它的含义。在计算机科学中,浮点数(或简称浮点数)是表示非整数值的数据值,例如 6.2815 或 0.0044。整数值(称为整数)经常用于控制计算机及其上运行的任何软件所需的计算。

浮点数对于精度至关重要的情况至关重要 - 特别是与科学或工程相关的任何事情。即使是简单的计算,例如确定圆的周长,也至少涉及一个浮点值。

几十年来,CPU 一直拥有单独的电路来对整数和浮点数执行逻辑运算。在上述 Pentium II Overdrive 的情况下,它可以在每个时钟周期执行一次基本浮点运算(乘法或加法)。理论上,这就是为什么 ASCI Red 的峰值浮点性能为 9,632 个 CPU x 3.33 亿个时钟周期 x 1 次操作/周期 = 3,207,456 百万次 FLOPS。

这些数字是基于理想条件(例如,对易于放入高速缓存的数据使用最简单的指令)预测的,并且在现实生活中很少实现。然而,它们可以很好地表明系统的功率。

其他超级计算机也拥有类似数量的标准处理器——劳伦斯利弗莫尔国家实验室的Blue Pacific使用了 5808 个 IBM PowerPC 604e芯片,洛斯阿拉莫斯国家实验室的Blue Mountain(上图)则使用了 6144 个MIPS Technologies R1000。

为了达到万亿次浮点运算级别的处理能力,需要数千个 CPU,所有这些都需要大量 RAM 和硬盘存储的支持。过去是这样,现在仍然是,这一切归因于机器的数学要求。当我们在学校第一次接触物理、化学和其他学科的方程时,一切都是一维的。换句话说,我们使用一个数字来表示距离、速度、质量、时间等。

然而,为了准确地建模和模拟现象,需要更多的维度,并且数学上升到向量、矩阵和张量的领域。它们在数学中被视为单个实体,但包含多个值,这意味着任何进行计算的计算机都需要同时处理大量数字。鉴于当时的 CPU 每个周期只能处理一到两个浮点数,因此需要数千个浮点数。

***02. ***SIMD 加入竞争:

MMX、3DNow!和SSE

1997 年,英特尔使用一种名为MMX的技术更新了其最初的奔腾系列 CPU ,这是一组利用内核内八个附加寄存器的指令。每个都被设计为存储一到四个整数值。该系统允许处理器同时执行跨多个数字的一条指令,这种方法更被称为 SIMD(单指令、多数据)。

一年后,AMD 推出了自己的版本,称为3DNow!。它的性能尤其优越,因为寄存器可以存储浮点值。又过了一年,英特尔才在 MMX 中解决这个问题,并在其 Pentium III 芯片中引入了SSE(流 SIMD 扩展)。

首次出现在 AMD K6-2 CPU 中的3D Now

随着日历进入新千年,高性能计算机的设计者可以使用能够有效处理矢量数学的标准处理器。一旦扩展到数千个,这些处理器就可以同样出色地管理矩阵和张量。尽管取得了这一进步,超级计算机世界仍然青睐旧的或专用的芯片,因为这些新的扩展并不是专门为此类任务而设计的。

对于另一种快速普及的处理器(GPU)来说也是如此,它比 AMD 或英特尔的任何 CPU 都更擅长 SIMD 工作。

在图形处理器的早期,CPU 处理组成场景的三角形的计算(因此 AMD 为其 SIMD 技术使用这个名称)。然而,像素的着色和纹理完全由 GPU 处理,并且这项工作的许多方面都涉及矢量数学。

20 多年前最好的消费级显卡,例如3dfx 的Voodoo5 5500和 Nvidia 的 GeForce 2 Ultra,都是出色的 SIMD 设备。然而,它们的创建目的是为游戏生成 3D 图形,而不是其他任何东西。即使是专业市场的显卡也只专注于渲染。

ATI 售价 2,000 美元的 ATI FireGL 3 配备了两个 IBM 芯片(一个 GT1000 几何引擎和一个 RC1000 光栅器)、一个巨大的 128 MB DDR-SDRAM 以及据称 30 GFLOPS 的处理能力。但这一切都是为了使用 OpenGL 渲染 API 加速 3D Studio Max 和 AutoCAD 等程序中的图形。

那个时代的 GPU 无法用于其他用途,因为转换 3D 对象并将其转换为监视器图像的过程并不涉及大量的浮点数学。事实上,其中很大一部分是在整数级别,并且图形卡需要几年的时间才能开始在整个管道中大量使用浮点值。

第一个是 ATI 的R300 处理器,它有 8 个独立的像素管道,以 24 位浮点精度处理所有数学运算。不幸的是,除了图形之外,没有其他方法可以利用这种能力——硬件和相关软件完全以图像为中心。

计算机工程师并没有忘记 GPU 拥有大量 SIMD 功能,但缺乏将其应用到其他领域的方法这一事实。令人惊讶的是,这是一个游戏机,展示了如何解决这个棘手的问题。

***03. ***统一的新时代

2005年11月,微软的Xbox 360上市,其CPU由IBM基于其标准PowerPC架构设计和制造,GPU由ATI设计、TMSC制造。这款代号为 Xenos 的图形芯片很特别,因为它的布局完全避开了单独的顶点和像素管道的经典方法。

取而代之的是一个三路 SIMD 阵列集群。具体来说,每个集群由 16 个向量处理器组成,每个向量处理器包含 5 个数学单元。这种布局使每个阵列能够在每个周期对 80 个浮点数据值同时执行来自线程的两条顺序指令。

这被称为统一着色器架构,每个阵列可以处理任何类型的着色器。尽管 Xenos 使芯片的其他方面变得更加复杂,但它引发了一种至今仍在使用的设计范例。

在时钟速度为 500 MHz 的情况下,整个集群理论上可以为乘法加法命令的三个线程实现 240 GFLOPS (500 x 16 x 80 x 2) 的处理速率。这个数字有一定的规模感,作为对比,十年前的一些世界顶级超级计算机甚至无法匹敌这个速度。

例如,桑迪亚国家实验室的aragon XP/S140配备 3,680 个 Intel i860 CPU,峰值速度为 184 GFLOPS。到 1995 年,这台机器已经有几年历史了,芯片开发的速度很快就超过了它,但 GPU 也是如此。

CPU 多年来一直在整合自己的 SIMD 阵列,例如,英特尔最初的 Pentium MMX 有一个专用单元,用于在向量上执行指令,最多包含 8 个 8 位整数。当 Xenos 在世界各地的家庭中使用时,此类装置的尺寸至少增加了一倍,但与 Xenos 相比,它们仍然很小。

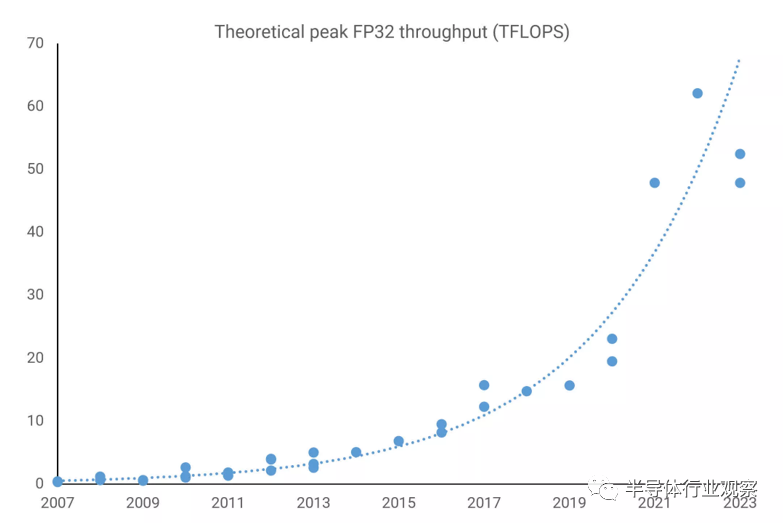

消费级显卡开始采用具有统一着色器架构的 GPU 时,它们已经拥有比 Xbox 360 的图形芯片明显更高的处理速率。2006 年GeForce 8800 GTX中使用的 Nvidia G80(上图)的理论峰值为 346 GLFOPS,而 2007 年Radeon HD 2900 XT中使用的 ATI R600则拥有 476 GLFOPS。

两家制造商很快就在其专业模型中利用了这种计算能力。虽然价格过高,但 ATI 的 FireGL V8650 和 Nvidia 的 Tesla C870 非常适合高端科学计算机。然而,在最高级别上,全球超级计算机仍然仅依赖标准 CPU。事实上,几年后 GPU 才开始出现在最强大的系统中。

那么,当它们明显提供了巨大的处理速度时,为什么不立即使用它们呢?

首先,超级计算机和类似系统的设计、建造和操作都极其昂贵。多年来,它们都是围绕大量 CPU 阵列构建的,因此集成另一个处理器并不是一朝一夕的事。此类系统在增加芯片数量之前需要进行彻底的规划和初始小规模测试。

其次,让所有这些组件协调运行,尤其是软件方面,绝非易事,这也是当时 GPU 的一个重大弱点。虽然它们已经变得高度可编程,但以前可供它们使用的软件相当有限。

Microsoft 的 HLSL(高级着色器语言)、Nvidia 的Cg 库和 OpenGL 的 GLSL 使访问图形芯片的处理能力变得简单,尽管纯粹是为了渲染。

统一着色器架构 GPU 改变了这一切。2006 年,ATI(当时是AMD 的子公司)和 Nvidia 发布了软件工具包,旨在将这种能力不仅仅用于图形,其 API 分别称为CTM(Close To Metal)和CUDA(Compute Unified Device Architecture)。

然而,科学和数据处理社区真正需要的是一个全面的软件包,它将大量的 CPU 和 GPU(通常称为异构平台)视为由众多计算设备组成的单个实体。

2009年,他们的需求得到了满足。OpenCL最初由 Apple 开发,由 Khronos Group(几年前吸收了 OpenGL)发布,成为在日常图形之外使用 GPU 的事实上的软件平台,或者该领域当时被称为 GPGPU(通用GPU 上的计算, Mark Harris创造的术语)。

***04. ***GPU 进入计算竞赛

与广阔的技术评论世界不同,全球范围内并没有数百名评论者测试超级计算机的性能主张。然而,德国曼海姆大学于 20 世纪 90 年代初启动的一个正在进行的项目正是致力于实现这一目标。该组织被称为“TOP500”,每年两次发布全球最强大的 10 台超级计算机排行榜。

第一个夸耀 GPU 的条目出现在 2010 年,中国有两个系统——星云和天河一号。他们分别使用 Nvidia 的Tesla C2050(本质上是 GeForce GTX 470,如下)和 AMD 的Radeon HD 4870卡,前者的理论峰值为 2,984 TFLOPS。

在高端 GPGPU 的早期阶段,Nvidia 是为计算巨头配备的首选供应商,不是因为性能(AMD 的 Radeon 卡通常提供更高程度的处理性能),而是因为软件支持。CUDA 经历了快速发展,几年后 AMD 才找到合适的替代方案,鼓励用户改用 OpenCL。

然而,英伟达并没有完全主导市场,英特尔的至强融核处理器试图占据一席之地。这些大型芯片源自一个名为 Larrabee 的已中止的 GPU 项目,是一种特殊的 CPU-GPU 混合体,由多个类似奔腾的核心(CPU 部分)与大型浮点单元(GPU 部分)配对组成。

对 Tesla C2050 内部结构的检查揭示了 14 个称为流式多处理器 (SM) 的块,由缓存和中央控制器划分。每一个都包含 32 组两个逻辑电路(Nvidia 将其标记为 CUDA 核心),用于执行所有数学运算 - 一组用于整数值,另一组用于浮点数。在后一种情况下,内核可以在每个时钟周期以单(32 位)精度管理一次 FMA(融合乘加)操作;双精度(64 位)运算至少需要两个时钟周期。

Xeon Phi 芯片(中的浮点单元看起来有些相似,只是每个内核处理的数据值只有 C2050 中 SM 的一半。尽管如此,由于与 Tesla 的 14 个重复核心相比,有 32 个重复核心,单个 Xeon Phi 处理器总体上每个时钟周期可以处理更多的值。然而,英特尔首次发布的该芯片更多的是原型机,无法充分发挥其潜力——英伟达的产品运行速度更快,功耗更低,并被证明是一款卓越的产品。

这将成为 AMD、英特尔和 Nvidia 之间三路 GPGPU 之争中反复出现的主题。一种型号可能拥有数量较多的处理核心,而另一种型号可能具有更快的时钟速度或更强大的缓存系统。

CPU 对于所有类型的计算仍然至关重要,许多超级计算机和高端计算系统仍然由 AMD 或英特尔处理器组成。虽然单个 CPU 无法与普通 GPU 的 SIMD 性能竞争,但当数千个 CPU 连接在一起时,它们就证明足够了。然而,此类系统缺乏功效。

例如,在天河一号使用Radeon HD 4870卡的同时,AMD最大的服务器CPU(12核Opteron 6176 SE)也开始流行。对于 140 W 左右的功耗,CPU 理论上可以达到 220 GFLOPS,而上述 GPU 的峰值性能可达到 1,200 GFLOPS,仅多出 10 W,而且成本仅为其一小部分。

***05. ***不再“只是”显卡

到了 2013 年,不仅仅是世界上的超级计算机在集体利用 GPU 的能力进行并行计算。Nvidia 正在积极推广其GRID 平台,这是一种用于科学和其他应用的 GPU 虚拟化服务。最初是作为托管基于云的游戏的系统而推出的,对大规模、经济实惠的 GPGPU 不断增长的需求使得这一转变不可避免。在其年度技术会议上,GRID 被认为是各领域工程师的重要工具。

在同一事件中,GPU 公司展示了代号为 Volta 的未来架构。然而,公布的细节很少,普遍的假设是这将是另一款服务于 Nvidia 所有市场的芯片。

与此同时,AMD 也在做类似的事情,在其专注于游戏的 Radeon 系列以及 FirePro 和 Radeon Sky 服务器卡中利用定期更新的 Graphics Core Next (GCN) 设计。那时,性能数据已经令人震惊——FirePro W9100 的峰值 FP32(32 位浮点)吞吐量为 5.2 TFLOPS,这个数字对于不到二十年前的超级计算机来说是不可想象的。

当然,GPU 仍然主要是为 3D 图形而设计的,但渲染技术的进步意味着这些芯片必须越来越擅长处理一般计算工作负载。唯一的问题是它们执行高精度浮点数学(即 FP64 或更高)的能力有限。纵观2015 年顶级超级计算机,与完全基于 CPU 的超级计算机相比,使用 GPU(英特尔的 Xeon Phi 或 Nvidia 的 Tesla)的数量相对较少。

当 Nvidia 在 2016 年推出Pascal 架构时,一切都发生了变化。这是该公司首次尝试专门为高性能计算市场设计 GPU,其他 GPU 则用于多个领域。前者只生产过一款(GP100),并且只产生了 5 种产品,但之前所有架构都只配备少数 FP64 内核,而这款芯片却容纳了近 2,000 个内核。

Tesla P100 提供超过 9 TFLOPS 的 FP32 处理能力以及 FP64 处理能力的一半,其功能非常强大。AMD 的 Radeon Pro W9100 使用其 Vega 10 芯片,在 FP32 中速度快了 30%,但在 FP64 中慢了 800%。此时,英特尔因销售不佳而濒临停产 Xeon Phi 系列。

一年后,Nvidia 终于发布了 Volta,这表明该公司不仅仅对将其 GPU 引入 HPC 和数据处理市场感兴趣,它还瞄准了另一个市场。

***06. ***神经元、网络,天哪!

深度学习是统称为机器学习的更广泛学科中的一个领域,机器学习本身是人工智能的一个子集。它涉及使用称为神经网络的复杂数学模型,从给定数据中提取信息,例如确定所呈现的图像描绘特定动物的概率。为此,模型需要进行“训练”——在本例中,显示了数百万张该动物的图像,以及数百万张不显示该动物的图像。

所涉及的数学植根于矩阵和张量计算。几十年来,此类工作负载只适合基于 CPU 的大型超级计算机。然而,早在 2000 年代,GPU 就显然非常适合此类任务。

尽管如此,英伟达还是押注于深度学习市场的大幅扩张,并在其 Volta 架构中添加了额外的功能,使其在该领域脱颖而出。这些是作为张量核心销售的 FP16 逻辑单元组,作为一个大型阵列一起运行,但功能非常有限。

事实上,它们只执行一项功能——将两个 FP16 4x4 矩阵相乘,然后将另一个 FP16 或 FP32 4x4 矩阵与该结果相加(这一过程称为 GEMM 运算)。Nvidia 之前的 GPU 以及竞争对手的 GPU 也可以执行此类计算,但速度远不及 Volta。GV100 是唯一使用该架构制造的 GPU,总共包含 512 个张量核心,每个核心能够在每个时钟周期执行 64 个 GEMM。

根据数据集中矩阵的大小以及所使用的浮点大小,Tesla V100 卡在这些张量计算中理论上可以达到 125 TFLOPS。Volta 显然是为小众市场设计的,但 GP100 在超级计算机领域的进军有限,而新的 Tesla 型号则迅速被采用。

PC游戏爱好者会知道,Nvidia随后在随后的图灵架构中将张量核心添加到其通用消费产品中,并开发了一种称为深度学习超级采样(DLSS)的升级技术。最新版本使用 GPU 中的核心在放大图像上运行神经网络,纠正帧中的任何伪影。

在短时间内,Nvidia 独占了 GPU 加速的深度学习市场,其数据中心部门的收入大幅增长——2017 财年增长率为 145%,2018 财年增长率为 133%,2019 财年增长率为 52%。截至 2019 财年末,HPC、深度学习等领域的销售额总计 29 亿美元。

然而,只要有钱,竞争就不可避免。2018 年,谷歌开始通过云服务提供对其内部开发的张量处理芯片的访问。亚马逊很快也紧随其后,推出了专用 CPU AWS Graviton。与此同时,AMD 正在重组其 GPU 部门,形成两条不同的产品线:一条主要用于游戏 (RDNA),另一条专门用于计算 (CDNA)。

虽然 RDNA 与其前身明显不同,但 CDNA 在很大程度上是 GCN 的自然演变,尽管规模扩大到了一个巨大的水平。看看当今用于超级计算机、数据服务器和人工智能机器的 GPU,一切都非常巨大。

AMD 的 CDNA 2 驱动的MI250X拥有 220 个计算单元,提供略低于 48 TFLOPS 的双精度 FP64 吞吐量和 128 GB 的高带宽内存 (HBM2e),这两个方面在 HPC 应用中都备受追捧。Nvidia 的 GH100 芯片采用Hopper 架构和 576 个 Tensor Core,有可能达到 4000 TOPS,在 AI 矩阵计算中采用低精度 INT8 数字格式。

英特尔的Ponte Vecchio GPU 同样庞大,拥有 1000 亿个晶体管,AMD 即将推出的 MI300 拥有 460 亿个晶体管,包括多个 CPU、显卡和内存小芯片。

然而,它们共有的一件事是它们绝对不是 GPU:它们不是 GPU。早在英伟达将该术语用作营销工具之前,该缩写词就代表图形处理单元。AMD 的 MI250X 没有任何渲染输出单元 (ROP),甚至 GH100 也只拥有类似于 GeForce GTX 1050 的Direct3D 性能,使得 GPU 中的“G”变得无关紧要。

那么,我们可以称呼它们什么呢?“GPGPU”并不理想,因为它是一个笨拙的短语,指的是在通用计算中使用 GPU,而不是设备本身。“HPCU”(高性能计算单元)也好不了多少。但也许这并不重要。毕竟,“CPU”一词非常广泛,涵盖了各种不同的处理器和用途。

***07. ***GPU 接下来要征服什么?

AMD、英特尔、Nvidia 和其他数十家公司在 GPU 研发上投入了数十亿美元,当今的图形处理器不会很快被任何截然不同的产品所取代。对于渲染,最新的 API 和使用它们的软件包(例如游戏引擎和 CAD 应用程序)通常与运行代码的硬件无关,因此从理论上讲,它们可以适应全新的东西。

然而,GPU 中专门用于图形的组件相对较少 - 三角形设置引擎和 ROP 是最明显的组件,并且最近版本中的光线追踪单元也高度专业化。然而,其余部分本质上是大规模并行 SIMD 芯片,由强大而复杂的内存/缓存系统支持。

基本设计与以往一样好,未来的任何改进都与半导体制造技术的进步紧密相关。换句话说,它们只能通过容纳更多逻辑单元、以更高的时钟速度运行或两者的组合来改进。

当然,它们可以合并新功能,使其能够在更广泛的场景中发挥作用。在 GPU 的历史上,这种情况已经发生过好几次,不过向统一着色器架构的过渡尤为重要。虽然最好有专用硬件来处理张量或光线追踪计算,但现代 GPU 的核心能够管理这一切,尽管速度较慢。

这就是为什么 MI250 和 GH100 等产品与台式电脑的同类产品非常相似,未来用于 HPC 和 AI 的设计很可能会遵循这一趋势。那么,如果芯片本身不会发生重大变化,那么它们的应用又如何呢?

鉴于与 AI 相关的任何事物本质上都是计算的一个分支,因此只要需要执行大量 SIMD 计算,就可能会使用 GPU。虽然科学和工程领域没有多少领域尚未使用此类处理器,但我们可能会看到 GPU 衍生产品的使用激增。

谷歌的 Coral 加速器板配有两个 edgeTPU 芯片

目前人们可以购买配备微型芯片的手机,其唯一功能是加速张量计算。随着 ChatGPT 等工具的功能和普及度不断增强,我们将看到更多配备此类硬件的设备。

不起眼的 GPU 已经从仅仅比 CPU 更快地运行游戏的设备发展成为通用加速器,为全球的工作站、服务器和超级计算机提供动力。全球数百万人每天都在使用它——不仅在我们的计算机、电话、电视和流媒体设备中,而且在我们使用包含语音和图像识别或提供音乐和视频推荐的服务时也是如此。

GPU 真正的下一步可能是一个未知的领域,但有一点是肯定的,图形处理单元将在未来几十年内继续成为计算和人工智能的主要工具。

审核编辑:刘清

-

存储器

+关注

关注

38文章

7551浏览量

164791 -

OpenGL

+关注

关注

1文章

85浏览量

29397 -

SIMD

+关注

关注

0文章

35浏览量

10366 -

专用处理器

+关注

关注

0文章

5浏览量

9382 -

GPU芯片

+关注

关注

1文章

304浏览量

5965

原文标题:从像素推动器到AI计算引擎,GPU的演变之路

文章出处:【微信号:算力基建,微信公众号:算力基建】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA+AI王炸组合如何重塑未来世界:看看DeepSeek东方神秘力量如何预测......

从图形处理到AI加速,一文看懂Imagination D系列GPU

从CPU到GPU:渲染技术的演进和趋势

从像素推动器到AI计算引擎,GPU的演变之路

从像素推动器到AI计算引擎,GPU的演变之路

评论