电源PCB设计

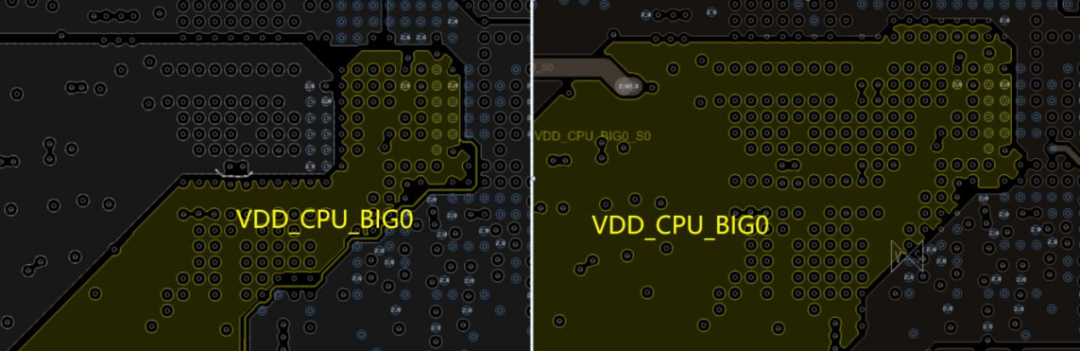

VDD_CPU_BIG0/1

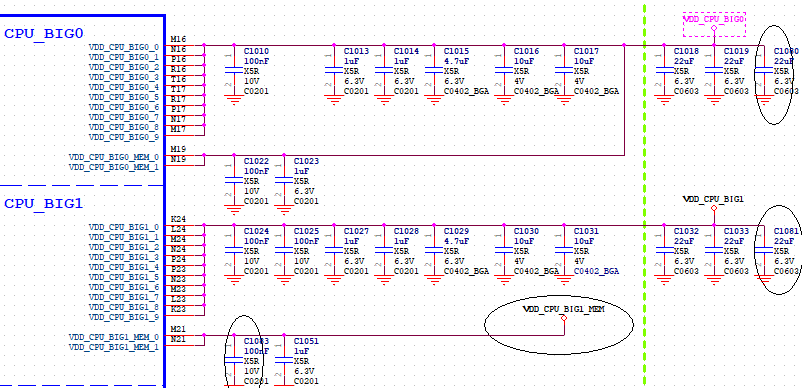

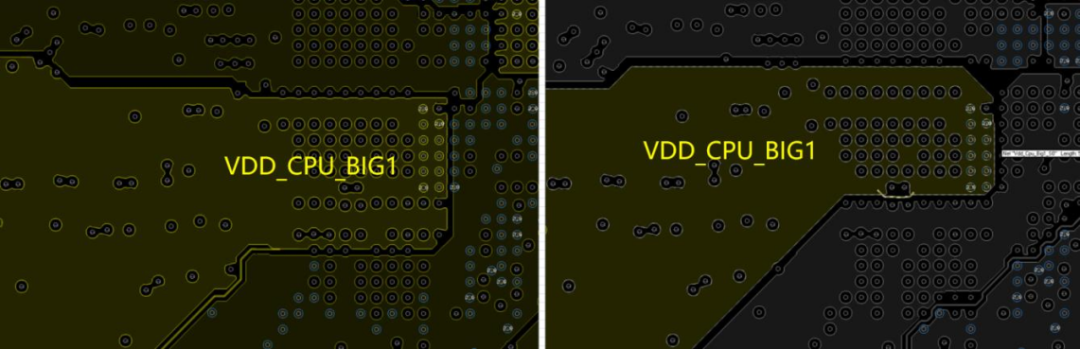

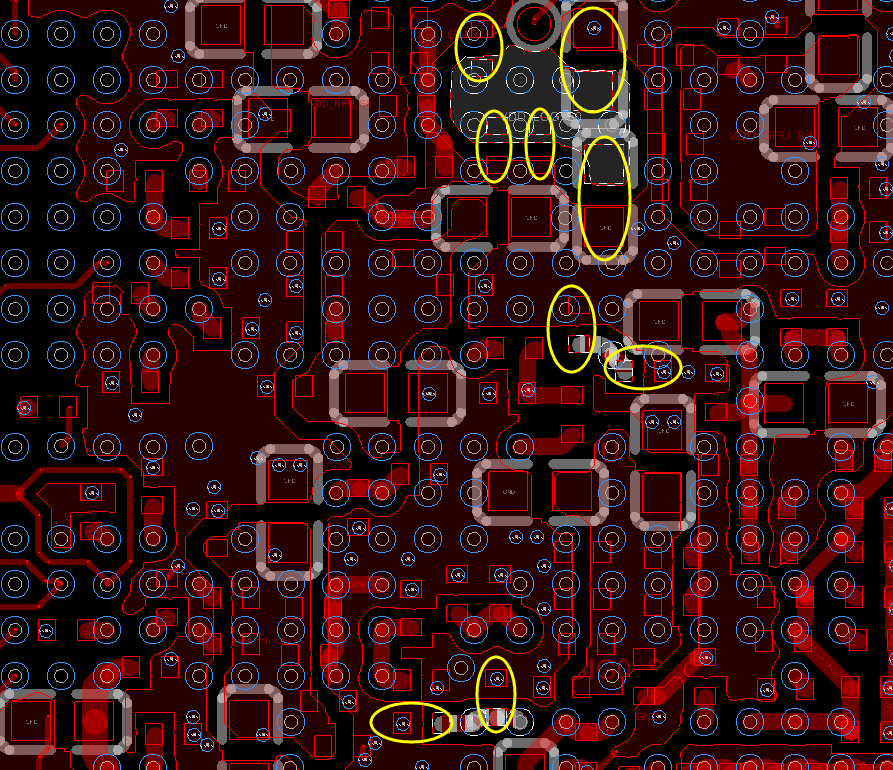

如下图(上)所示的滤波电容,原理图上靠近RK3588的VDD_CPU_BIG电源管脚绿线以内的去耦电容,务必放在对应的电源管脚背面,电容GND PAD尽量靠近芯片中心的GND管脚放置,如下图(下)所示。

其余的去耦电容尽量摆放在芯片附近,而且需要摆放在电源分割来源的路径上。

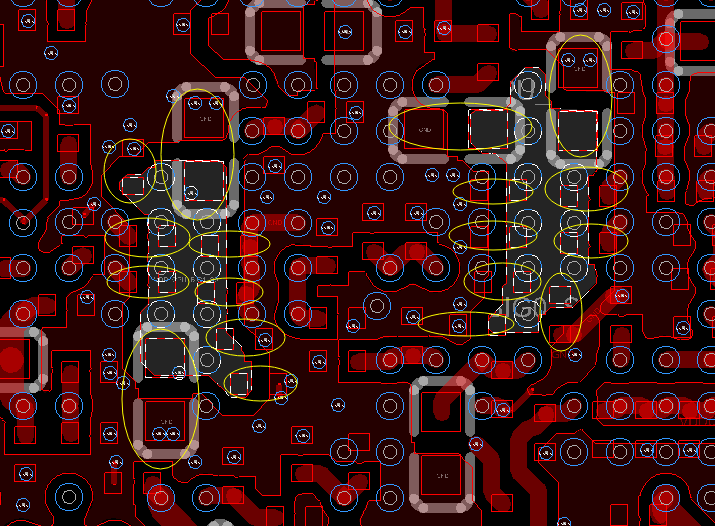

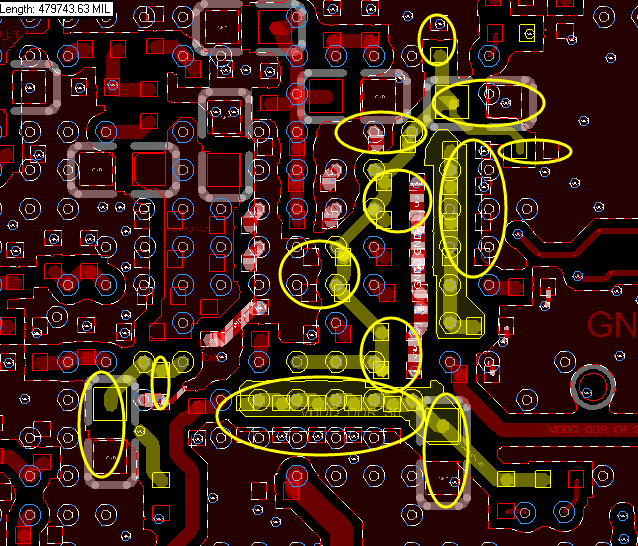

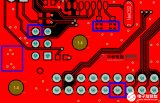

RK3588芯片VDD_CPU_BIG0/1的电源管脚,保证每个管脚边上都有一个对应的过孔,并且顶层走“井”字形,交叉连接。

如下图是电源管脚扇出走线情况,建议走线线宽10mil。

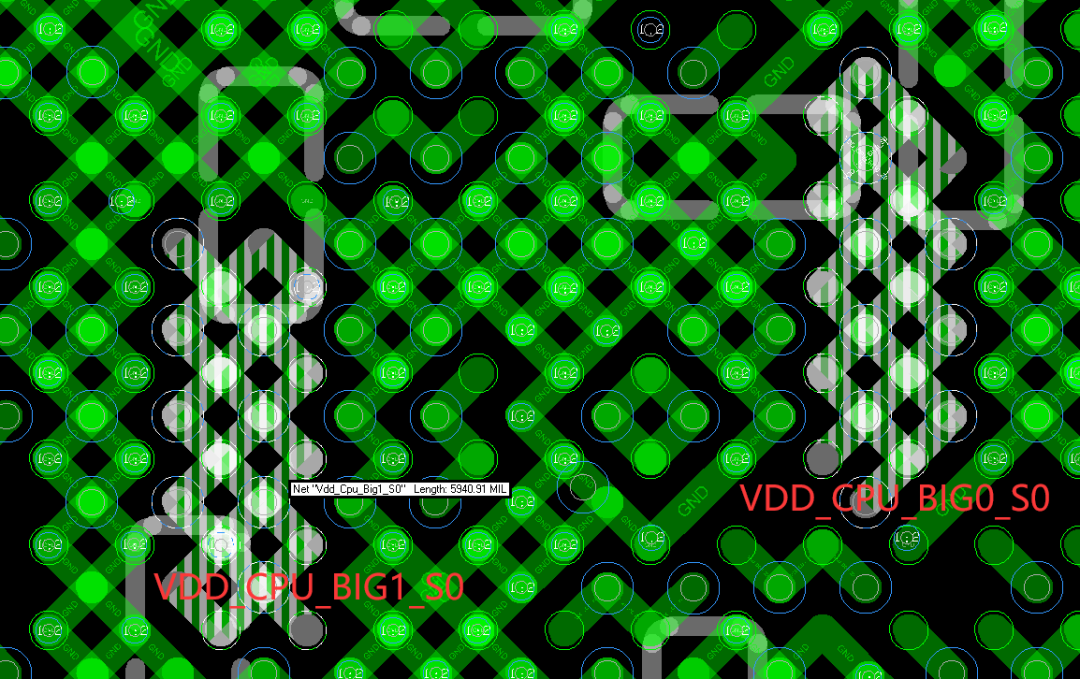

VDD_CPU_BIG0/1覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚覆铜足够宽。

路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够。

VDD_CPU_BIG的电源在外围换层时,要尽可能的多打电源过孔(12个及以上0.5*0.3mm的过孔),降低换层过孔带来的压降。

去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

VDD_CPU_BIG电流比较大需要双层覆铜,VDD_CPU_BIG 电源在CPU区域线宽合计不得小于 300mil,外围区域宽度不小于600mil。

尽量采用覆铜方式降低走线带来压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜),如下图所示。

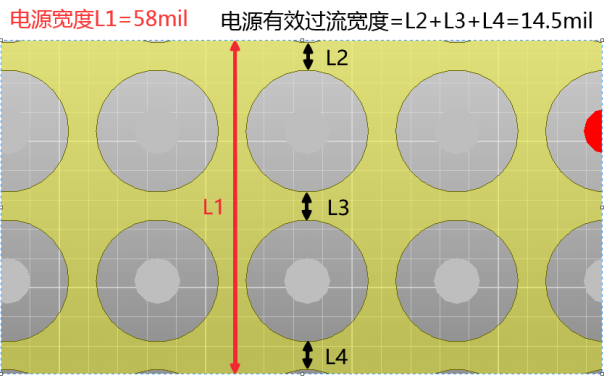

电源平面会被过孔反焊盘破坏,PCB设计时注意调整其他信号过孔的位置,使得电源的有效宽度满足要求。

下图L1为电源铜皮宽度58mil,由于过孔的反焊盘会破坏铜皮,导致实际有效过流宽度仅为L2+L3+L4=14.5mil。

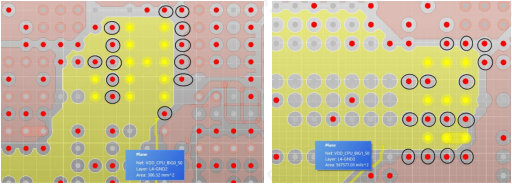

BIG0/1电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧12个,如下图所示。

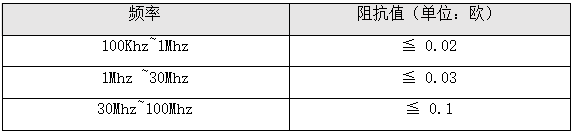

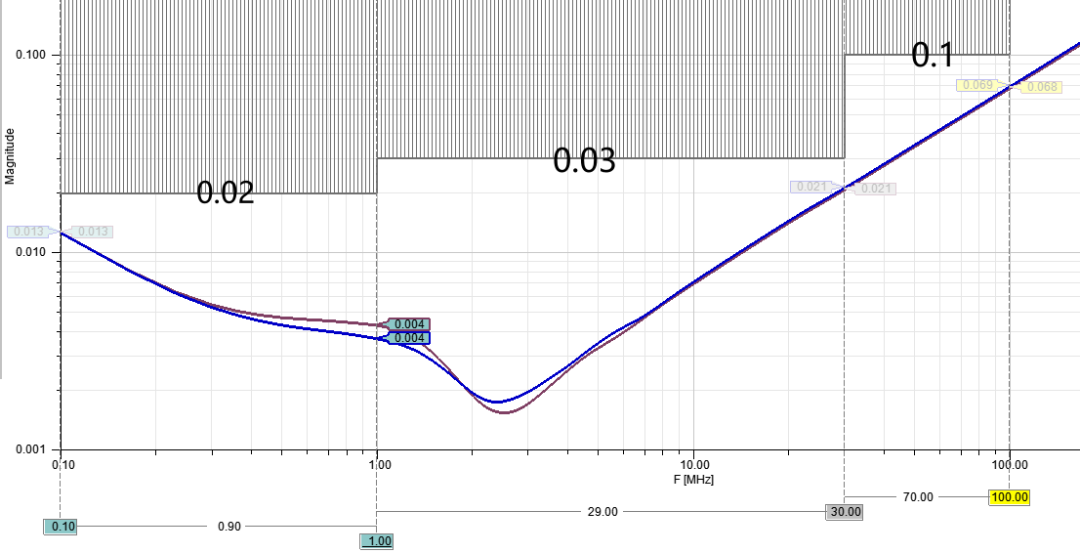

BIG电源PDN目标阻抗建议值,如下表和下图所示。

电源PCB设计

VDD_LOGIC

VDD_LOGIC的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽。

路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚路径都足够。

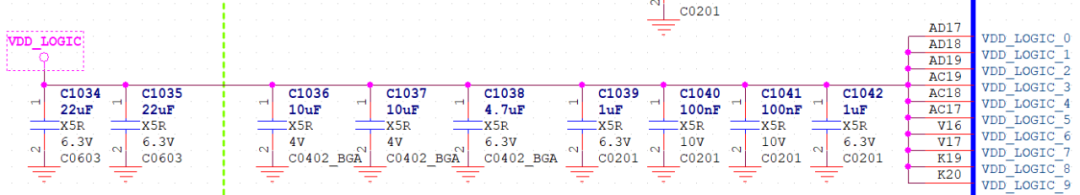

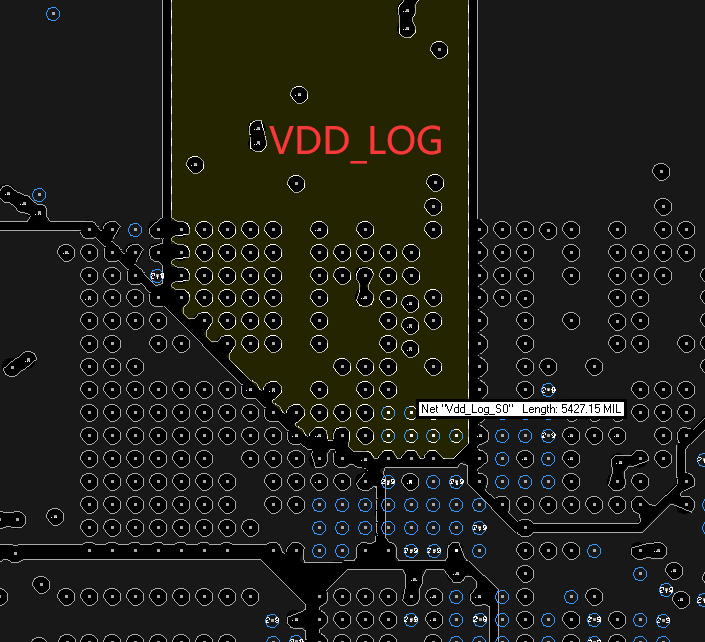

如下图(上)所示,原理图上靠近RK3588的VDD_LOGIC电源管脚绿线以内的去耦电容,务必放在对应的电源管脚背面,电容的GND管脚尽量靠近芯片中心的GND管脚放置,如下图(下)所示。

其余的去耦电容尽量摆放在RK3588芯片附近,并摆放在电源分割来源的路径上。

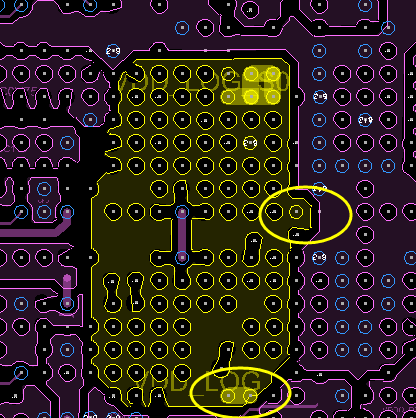

RK3588芯片VDD_LOGIC的电源管脚,每个管脚需要对应一个过孔,并且顶层走“井”字形,交叉连接,如下图所示,建议走线线宽10mil。

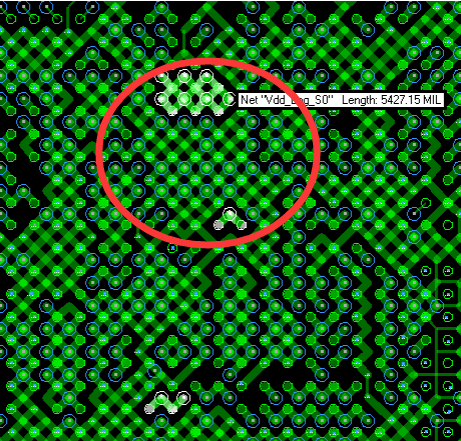

BIG0/1电源过孔40mil范围(过孔中心到过孔中心间VDD_LOGIC电源在CPU区域线宽不得小于120mil,外围区域宽度不小于200mil。

尽量采用覆铜方式,降低走线带来压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜),GND过孔数量建议≧12个。

VDD_LOGIC的电源在外围换层时,要尽可能的多打电源过孔(8个以上10-20mil的过孔),降低换层过孔带来的压降。

去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用,如下图所示。

电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧11个,如下图所示。

电源PCB设计

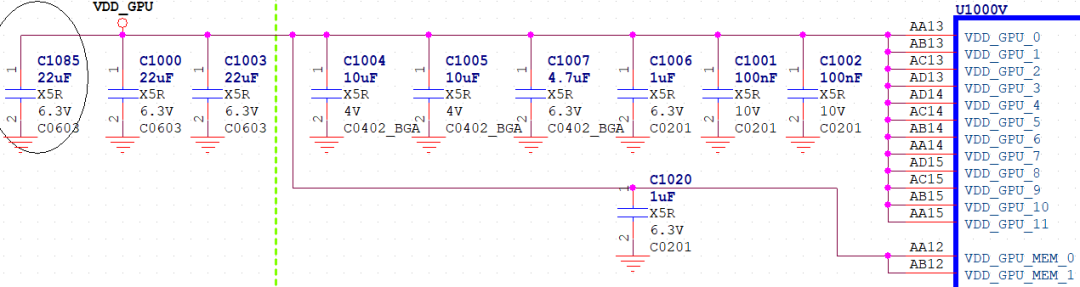

VDD_GPU

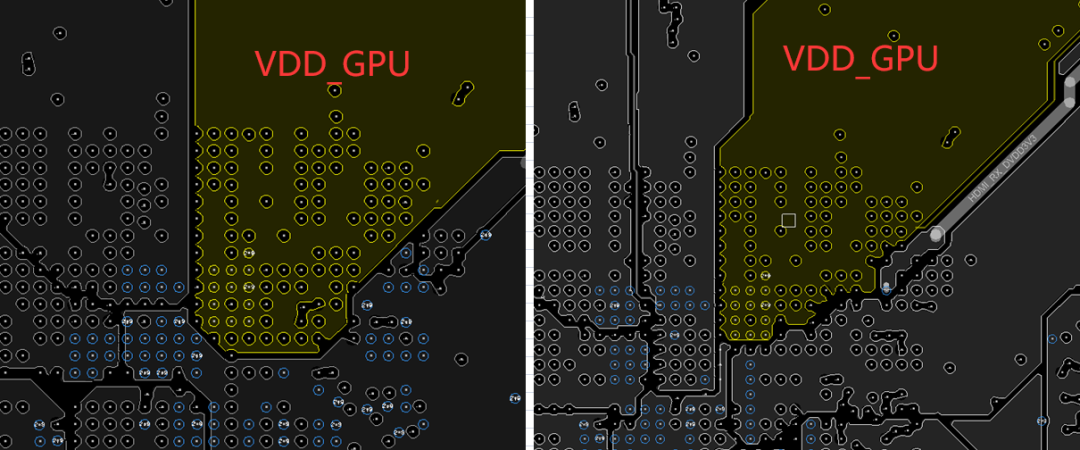

VDD_GPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽。

路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

VDD_GPU 的电源在外围换层时,要尽可能的多打电源过孔(10个以上0.5*0.3mm的过孔),降低换层过孔带来的压降。

去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

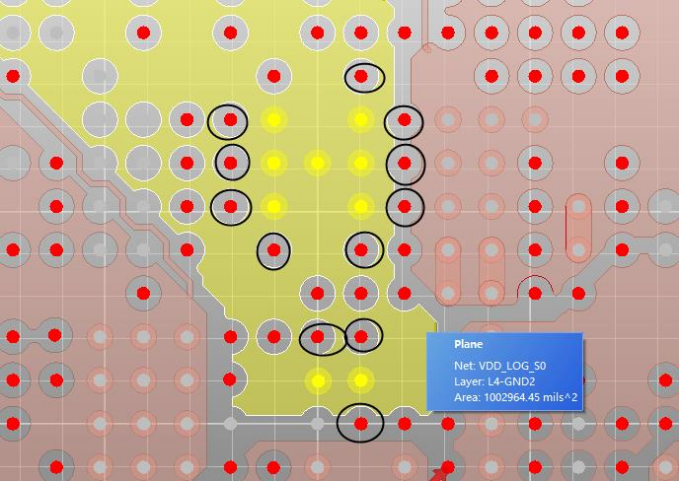

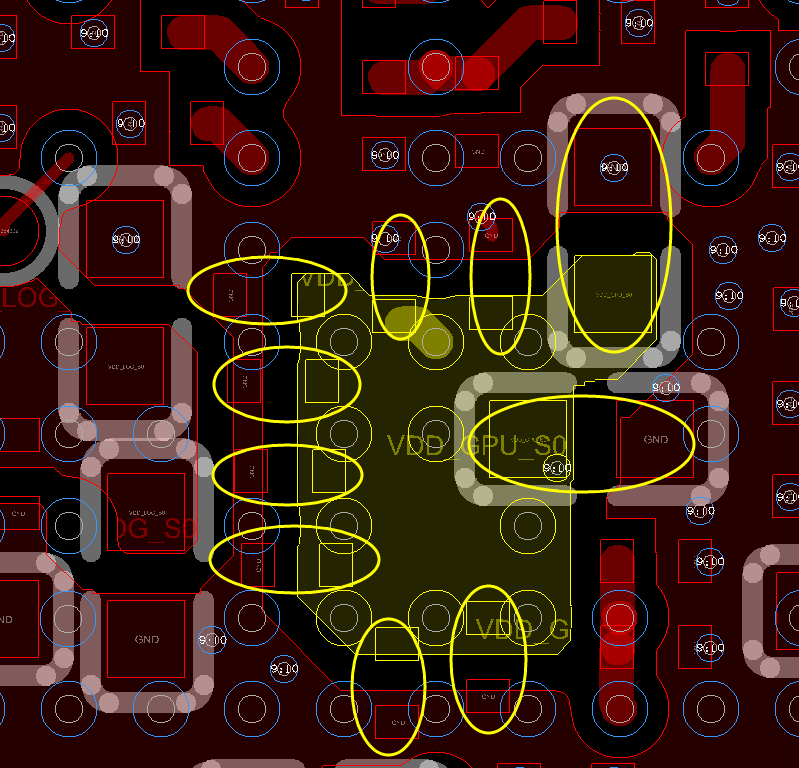

如下图(上)所示,原理图上靠近RK3588的VDD_GPU电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如下图(下)所示。

其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

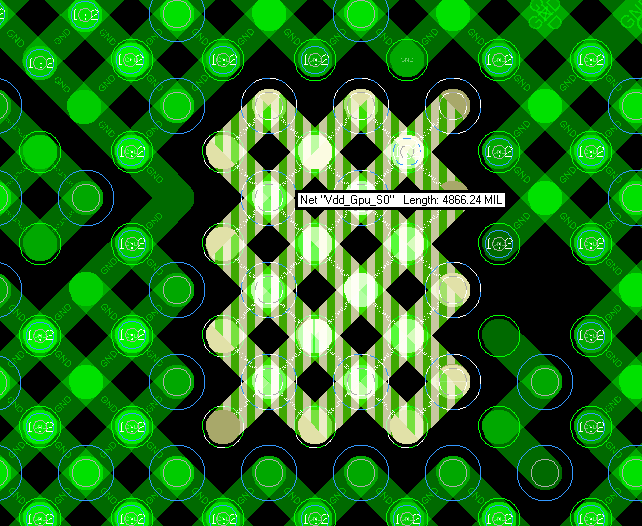

RK3588芯片VDD_GPU的电源管脚,每个管脚需要对应一个过孔,并且顶层走“井”字形,交叉连接,如下图所示,建议走线线宽10mil。

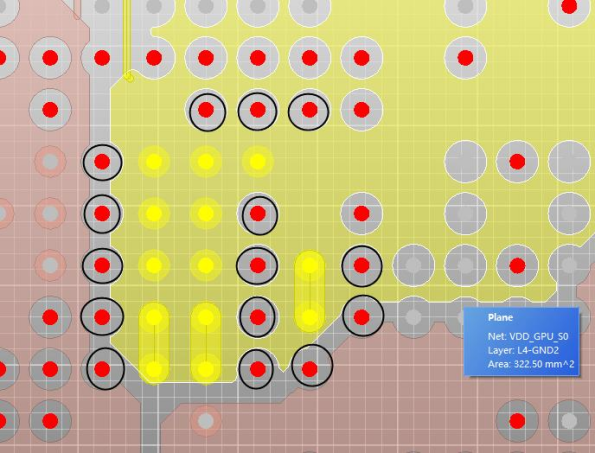

VDD_GPU电源在GPU区域线宽不得小于300mil,外围区域宽度不小于500mil,采用两层覆铜方式,降低走线带来压降。

电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧14个,如下图所示。

电源PCB设计

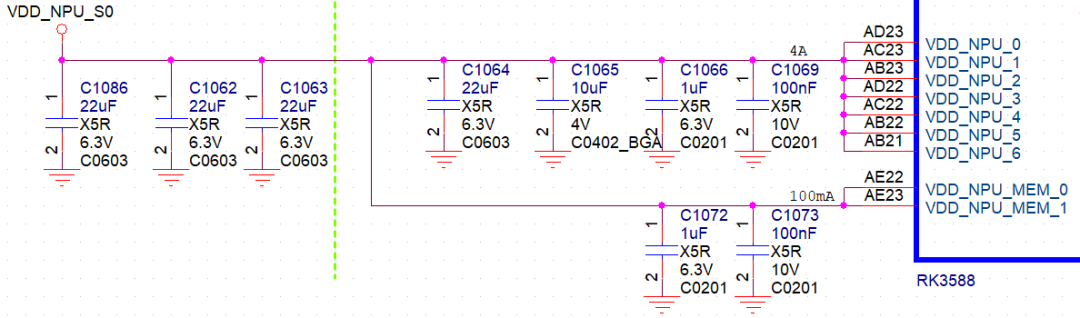

VDD_NPU

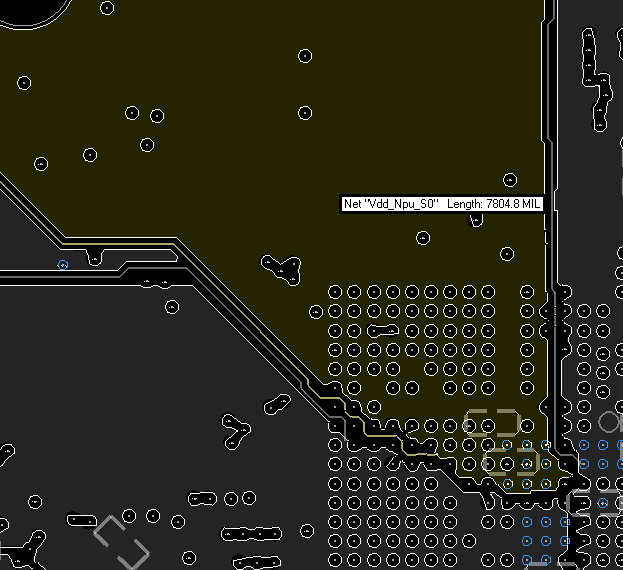

VDD_NPU的覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽。

路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

VDD_NPU的电源在外围换层时,要尽可能的多打电源过孔(7个以上0.5*0.3mm的过孔),降低换层过孔带来的压降。

去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

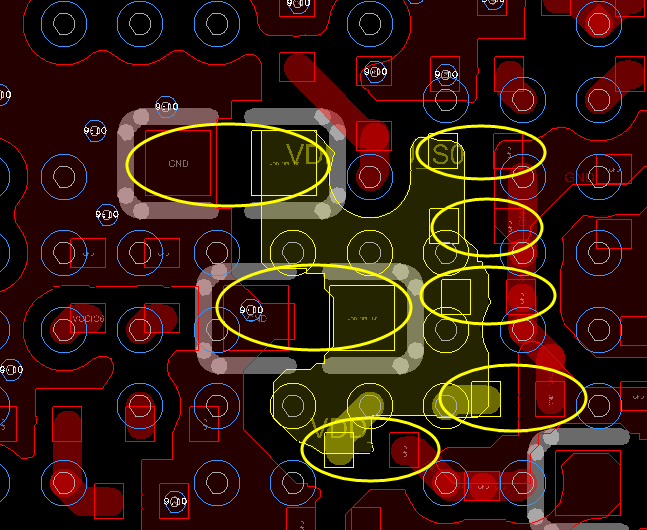

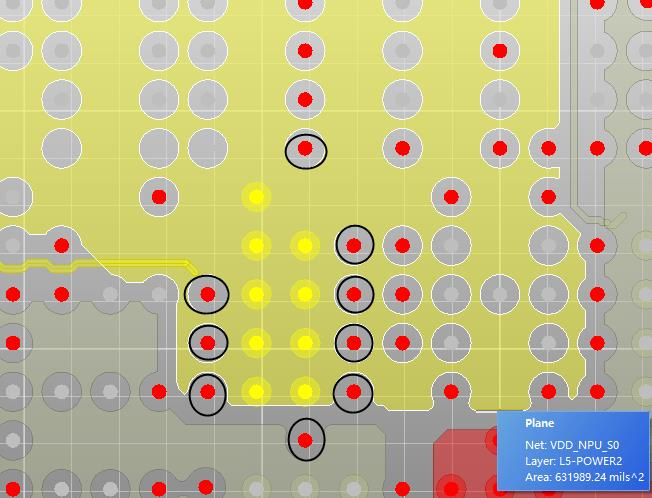

如下图(上)所示,原理图上靠RK3588的VDD_NPU电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如下图(下)所示。

其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

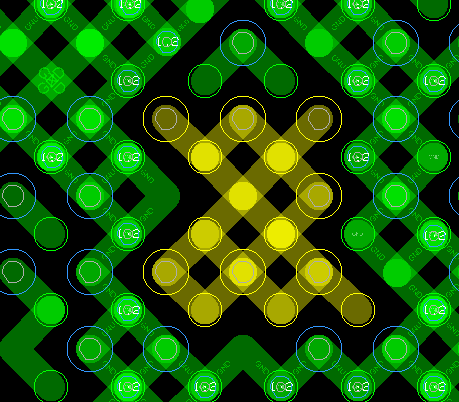

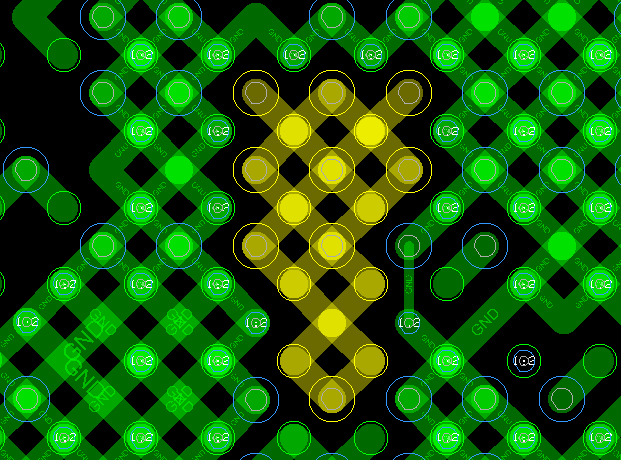

RK3588芯片VDD_NPU的电源管脚,每个管脚就近有一个对应过孔,并且顶层走“井”字形,交叉连接,如下图所示 ,建议走线线宽10mil。

VDD_NPU电源在NPU区域线宽不得小于300mil,外围区域宽度不小于500mil。

尽量采用覆铜方式,降低走线带来的压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜)。

电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧9个。

电源PCB设计

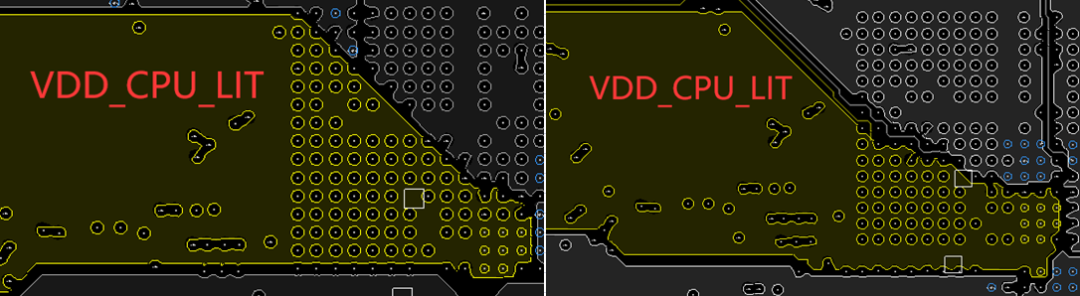

VDD_CPU_LIT

VDD_CPU_LIT覆铜宽度需满足芯片电流需求,连接到芯片电源管脚的覆铜足够宽。

路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

VDD_CPU_LIT的电源在外围换层时,要尽可能的多打电源过孔(9个以上0.5*0.3mm的过孔),降低换层过孔带来的压降。

去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

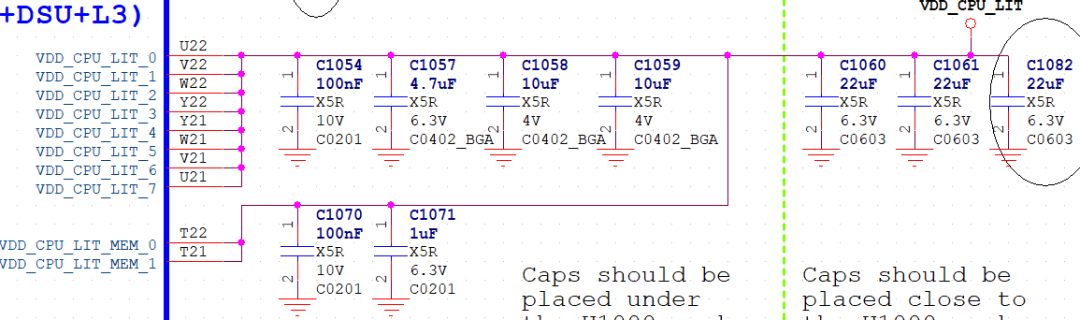

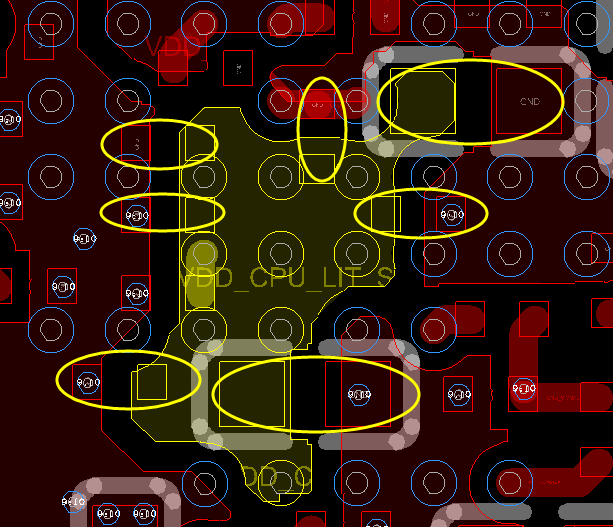

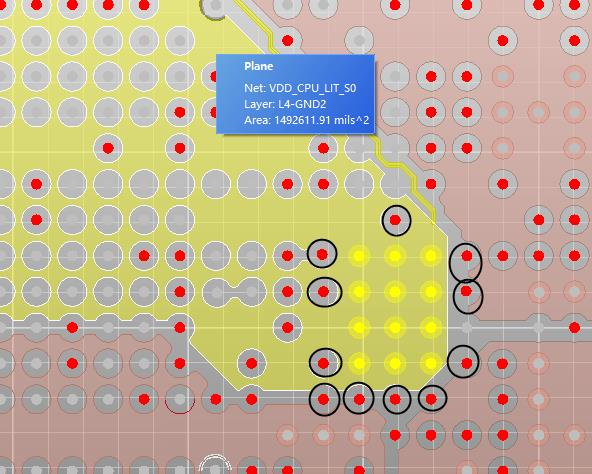

如下图(上)所示,原理图上靠近RK3588的VDD_CPU_LIT电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如下图(下)所示。

其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

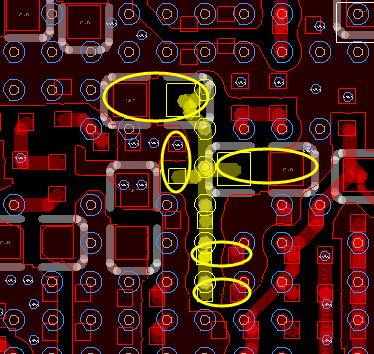

RK3588芯片VDD_CPU_LIT的电源管脚,每个管脚就近有一个对应过孔,并且顶层走“井”字形,交叉连接,如下图建议走线线宽10mil。

VDD_CPU_LIT电源在CPU区域线宽不得小于120mil,外围区域宽度不小于300mil。

采用双层电源覆铜方式,降低走线带来压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜)。

电源过孔40mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧9个。

电源PCB设计

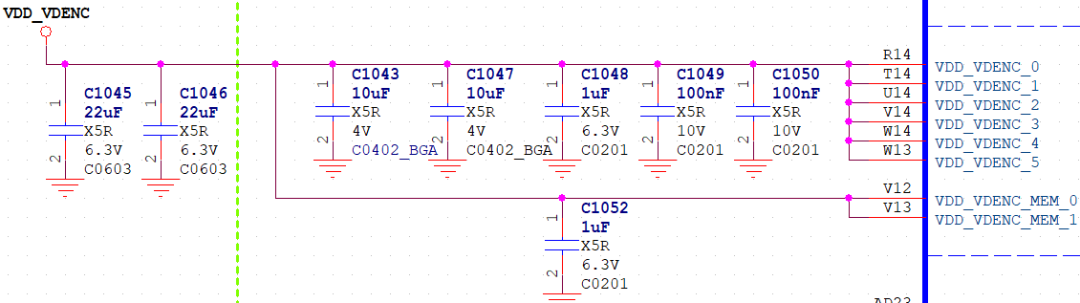

VDD_VDENC

VDD_VDENC覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽。

路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

VDD_VDENC电源在外围换层时,要尽可能的多打电源过孔(9个以上0.5*0.3mm的过孔),降低换层过孔带来的压降。

去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

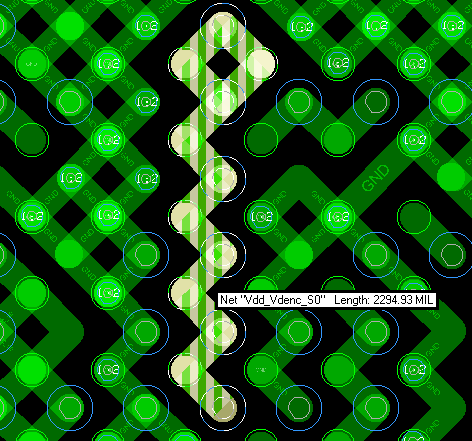

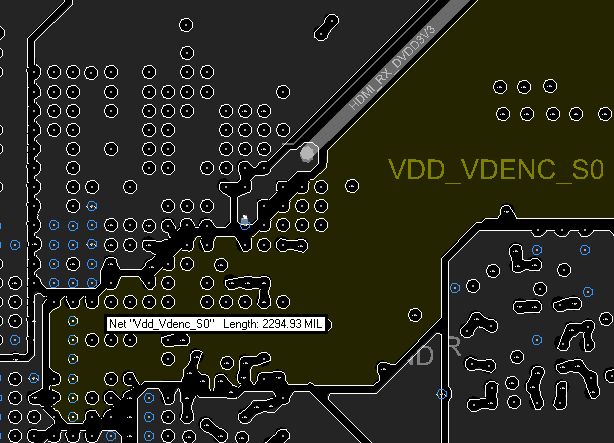

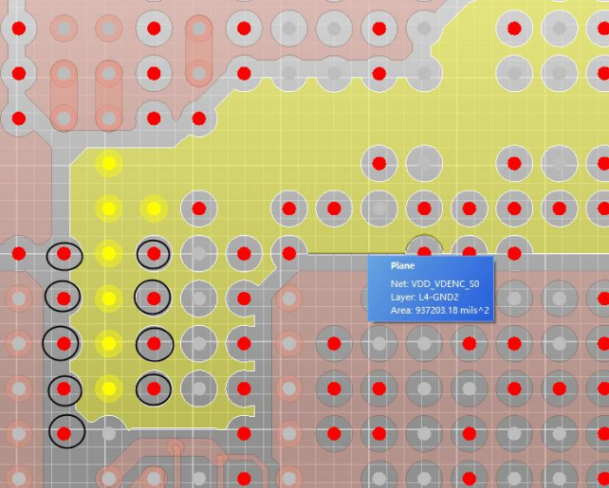

如下图(上)所示,原理图上靠近RK3588的VDD_VDENC电源管脚绿线以内的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,如下图(下)所示。

其余的去耦电容尽量摆放在RK3588芯片附近,并需要摆放在电源分割来源的路径上。

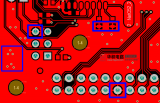

RK3588芯片VDD_VDENC的电源管脚,每个管脚就近有一个对应过孔,并且顶层走“井”字形,交叉连接,如下图建议走线线宽10mil。

VDD_VDENC电源在CPU区域线宽不得小于100mil,外围区域宽度不小于300mil,采用双层电源覆铜方式,降低走线带来压降。

电源过孔30mil范围(过孔中心到过孔中心间距)内的GND过孔数量,建议≧8个。

电源PCB设计

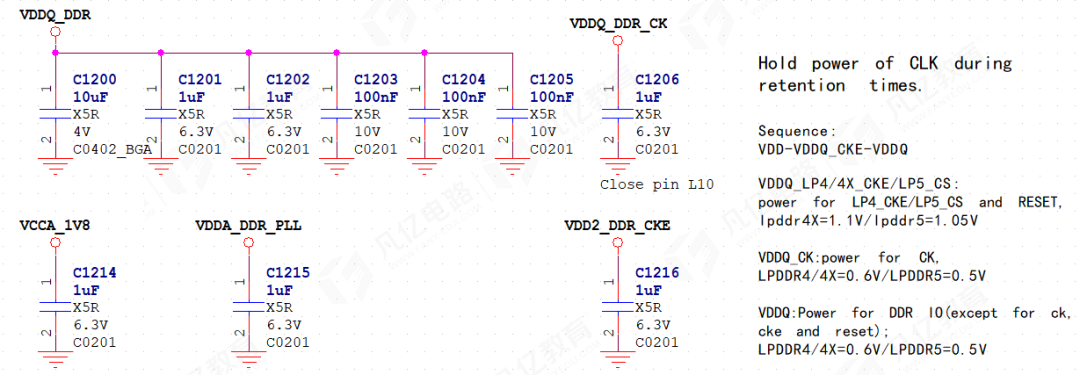

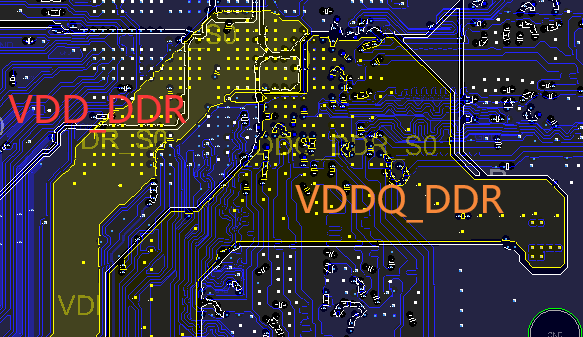

VCC_DDR

VCC_DDR覆铜宽度需满足芯片的电流需求,连接到芯片电源管脚的覆铜足够宽。

路径不能被过孔分割太严重,必须计算有效线宽,确认连接到CPU每个电源PIN脚的路径都足够。

VCC_DDR的电源在外围换层时,要尽可能的多打电源过孔(9个以上0.5*0.3mm的过孔),降低换层过孔带来的压降。

去耦电容的GND过孔要跟它的电源过孔数量保持一致,否则会大大降低电容作用。

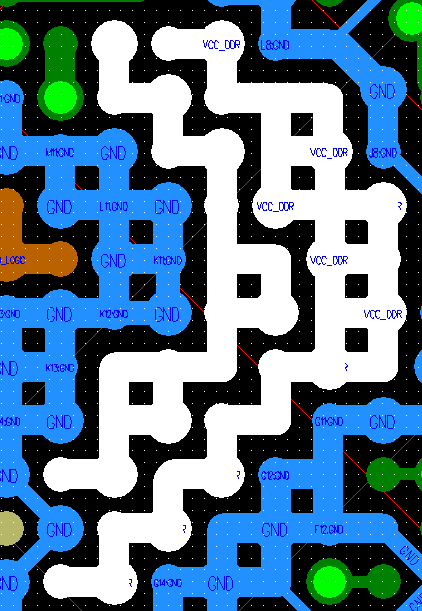

如下图(上)所示,原理图上靠近RK3588的VCC_DDR电源管脚的去耦电容务必放在对应的电源管脚背面,电容的GND PAD尽量靠近芯片中心的GND管脚放置,其余的去耦电容尽量靠近RK3588,如下图(下)所示。

RK3588芯片VCC_DDR的电源管脚,每个管脚需要对应一个过孔,并且顶层走“井”字形,交叉连接,如下图建议走线线宽10mil。

当LPDDR4x 时,链接方式如下图所示。

VCC_DDR电源在CPU区域线宽不得小于120mil,外围区域宽度不小于200mil。

尽量采用覆铜方式,降低走线带来压降(其它信号换层过孔请不要随意放置,必须规则放置,尽量腾出空间走电源,也有利于地层的覆铜)。

设计完PCB后,一定要做分析检查,才能让生产更顺利,这里推荐一款可以一键智能检测PCB布线布局最优方案的工具:华秋DFM软件,只需上传PCB/Gerber文件后,点击一键DFM分析,即可根据生产的工艺参数对设计的PCB板进行可制造性分析。

华秋DFM软件是国内首款免费PCB可制造性和装配分析软件,拥有300万+元件库,可轻松高效完成装配分析。其PCB裸板的分析功能,开发了19大项,52细项检查规则,PCBA组装的分析功能,开发了10大项,234细项检查规则。

基本可涵盖所有可能发生的制造性问题,能帮助设计工程师在生产前检查出可制造性问题,且能够满足工程师需要的多种场景,将产品研制的迭代次数降到最低,减少成本。

https://dfm.elecfans.com/uploads/software/promoter/HQDFM%20V3.7.0_DFMGZH.zip

专属福利

上方链接下载还可享多层板首单立减50元

每月1次4层板免费打样

并领取多张无门槛“元器件+打板+贴片”优惠券

华秋电子是一家致力于以信息化技术改善传统电子产业链服务模式的产业数智化服务平台,目前已全面打通产业上、中、下游,形成了电子产业链闭环生态,致力于为行业带来“高品质,短交期,高性价比”的一站式服务平台,可向广大客户提供媒体社区平台服务、元器件采购服务、PCB制造服务及可靠性制造分析服务、SMT贴片/PCBA加工服务,如有相关业务需求,请扫码填写以下表单,我们将为您对接专属服务。

原文标题:【华秋干货铺】电源PCB设计汇总

文章出处:【微信公众号:华秋电子】欢迎添加关注!文章转载请注明出处。

-

华秋电子

+关注

关注

19文章

475浏览量

13418

原文标题:【华秋干货铺】电源PCB设计汇总

文章出处:【微信号:huaqiu-cn,微信公众号:华秋电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

HDMI模块的PCB设计

专业PCB设计,高速PCB设计,PCB设计外包, PCB Layout,PCB Design,PCB画板公司,PCB设计公司,迅安通科技公司介绍

求助,关于双面板运放PCB铺铜遇到的疑问求解

PCB设计与PCB制板的紧密关系

PCB想要做好铺铜,这几点不容忽视!

PCB设计基本原则总结,工程师必看

PCB设计的EMC有哪些注意事项

LDO电源模块如何快速设计布局

多层pcb设计如何过孔的原理

浅谈PCB设计中铺铜的必要性

【华秋干货铺】电源PCB设计汇总

【华秋干货铺】电源PCB设计汇总

评论