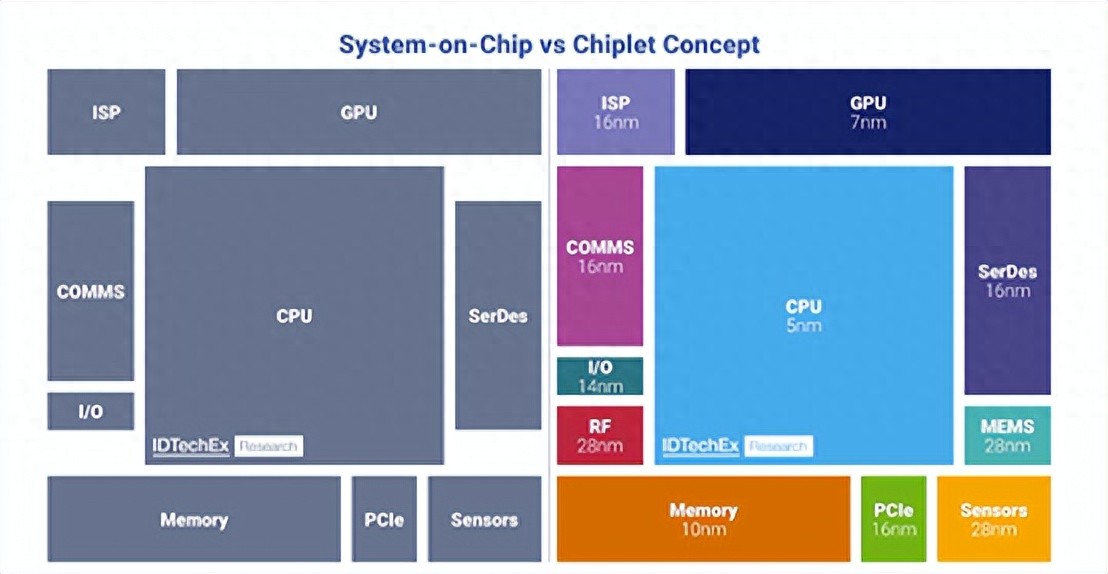

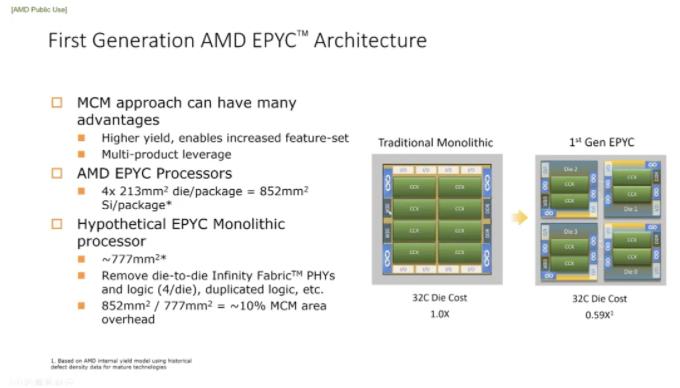

电子发烧友网报道(文/周凯扬)随着摩尔定律的失效或者说减弱已成定数,除了稳步发展半导体制造工艺外,半导体产业还涌现了不少继续提高性能的方法,比如Chiplet技术。该技术将复杂的SoC芯片设计分解成模块化的小芯片单元,再通过die-to-die(D2D)技术将其封装在一起。

如此一来设计更高效的重复利用成为现实,借助Chiplet设计芯片的厂商们不仅降低了成本,也极大加快了产品上市周期,更可以改善大型单片SoC的良率。当下Chiplet无论是从设计还是制造,以及标准化上都拥有了较为成熟的生态,从这些生态中我们也可以看出为何越来越多的SoC选择Chiplet设计。

EDA与IP

要说Chiplet生态除了造福下游一众初创半导体企业外,也带动了EDA与IP厂商的创新和发展,甚至说他们是直接受益人也不为过。从IP厂商来说的话,目前被Chiplet生态中利用最多的莫过于接口IP的Chiplet,比如新思等IP厂商的产品。同时,类似以太网等接口IP往往无需用到最先进的工艺,很适合用于节省芯片整体成本。

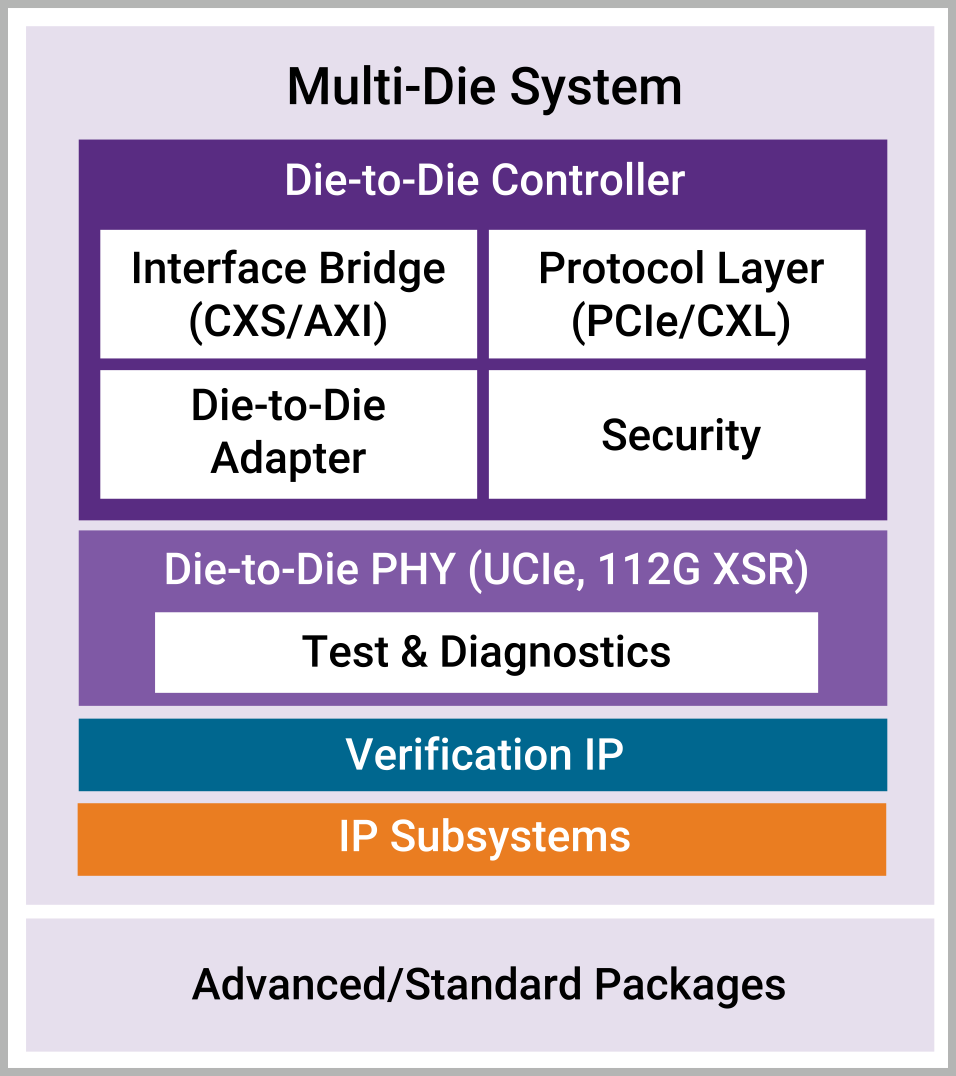

Designware多Die系统解决方案 / 新思

像Blue Cheetah这样的IP厂商,也推出了为Chiplet定制的D2D互联IP方案BlueLynx,支持到5nm、7nm、12nm和16nm的工艺节点,且不少Tier1和初创企业都将该方案用于其数据中心、网络和AI芯片中。

至于相关通用计算类IP在公开Chiplet化的进度上仍较为落后,毕竟这类IP往往是各大厂商最强竞争力的体现。拥有足够优秀IP的厂商往往会选择自研产品,而不是拿出来供市场公开重复利用。但RISC-V架构下的IP厂商倒是对此更加开放,而Arm也有心将其用于特定的应用中去,比如服务器CPU。

而EDA厂商目前对Chiplet生态的参与度也相当高,包括新思、Cadence这些本身就有IP业务的厂商在内,本身就有着全流程的EDA工具,自然也都早早参与到Chiplet生态的建设中来。与此同时,多个Chiplet设计的分层测试、诊断维护以及全面检测功能也属于EDA厂商的重心,毕竟这对于制造难易程度和长期系统可靠性来说至关重要。

而国产EDA厂商在Chiplet设计上的进度就有些慢了,目前绝大多数国产EDA厂商并没有提供Chiplet对应的方案,已知开始Chiplet相关技术研发的公司包括华大九天、合见工软等厂商,考虑到国内EDA厂商对这类先进封装方案的研究尚处于开始阶段,也需要更多的时间积累才有概率赶上国际大厂。

制造与封装

同样在半导体制造端,绝大多数厂商都已经开启了Chiplet的进程,出货量也在逐渐上升,对于他们来说对Chiplet的支持反而会给他们带来更多的订单。以台积电为例,Chiplet对于他们来说就是一个与3D堆叠技术完美结合的方案。

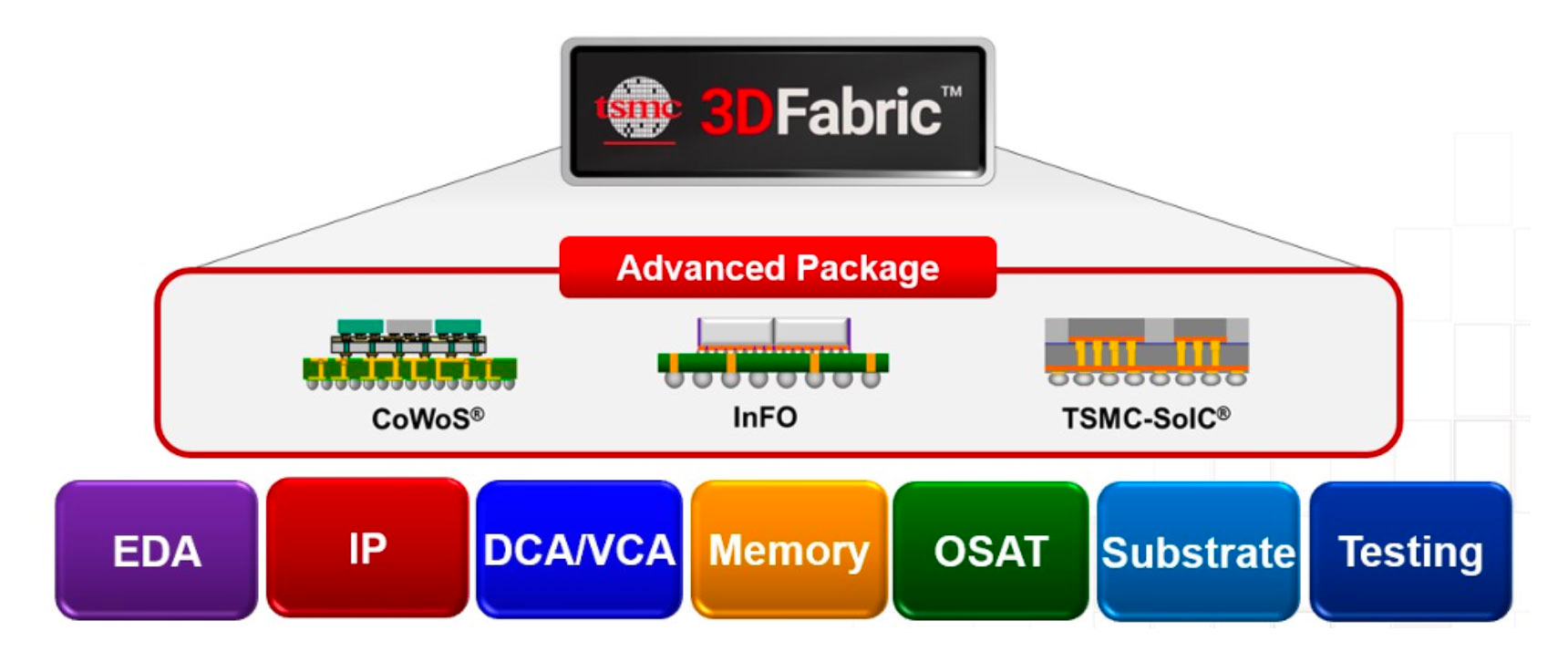

为此,台积电于去年在其OIP合作伙伴生态下,成立了新的3DFabric联盟,拉拢EDA/IP、DCA/VCA、内存、OAST、基板与测试厂商,一同推进Chiplet生态的发展。像AMD这样的厂商,早就和台积电合作打造了基于3D Chiplet技术的CPU和APU产品。

3DFabric联盟 / 台积电

除了3DFabric的3D堆叠和先进封装技术外,台积电还和EDA厂商合作打造了3Dblox这一标准,用于统一设计工具的工作流,让客户在台积电的平台上进行3D Chiplet IC设计时,拥有更高的灵活度和易用性。

与此同时,Chiplet为封装厂商创造了更多的机会,即便是初创企业也都有机会参与到最先进的半导体制造流程中来。今年年初,长电科技宣布其XDFOI Chiplet高密度多维异构集成系列工艺已经进入稳定量产阶段,且同步实现国际客户4nm节点的多芯片系统集成封装产品出货,最大可实现1500mm2的系统级封装面积。

据长电科技公布的数据,其XDFOI Chiplet技术可以实现50μm以内的中介层厚度,40μm的微凸点中心距,可以供客户在更小的单位面积内实现各种高密度工艺的集成,从而做到更小的封装尺寸。至于国际客户的4nm封装订单,则很有可能是来自某个高性能AI芯片。

再以周秀文、戴伟立夫妇二人和前长电科技执行副总裁韩丙濬2021年成立的Silicon Box为例。这家新加坡初创公司在近期宣布,他们耗资20亿美元在本地建立的先进半导体封装厂正式开放,主打解决Chiplet互联技术面临的挑战。

三大创始人的背景则足以证明了Chiplet的潜力,更何况周秀文早前就提出过Mochi这种模块化芯片架构的方案。且据CEO韩丙濬称,早在工厂尚未完工之前,客户就已经开始排队了。Silicon Box表示新封装厂的成立加上其专有的次5μm级互联技术,将帮助AI、数据中心和电动汽车等领域的客户实现更快的芯片上市周期,同时保证他们的IP安全性。

目前已知公开有合作意向的客户就包括了RISC-V AI芯片初创企业Tenstorrent,其两大高层Jim Keller和Raja Koduri都在近期参观了Silicon Box的新封装厂。从Tenstorrent的产品路线图来看,后续AI芯片中的Chiplet封装很可能会交由Silicon Box完成。

联盟与规范

当然了,作为力求席卷行业的一个技术,即便是不开源,也需要有一定的标准规范,比如上文中台积电联合EDA厂商推出的3Dblox。同时也需要行业个体和组织共同推动,比如UCIe联盟。UCIe联盟作为成立尚不足两年的Chiplet标准联盟,已经吸引了一大批巨头和初创企业的加入。

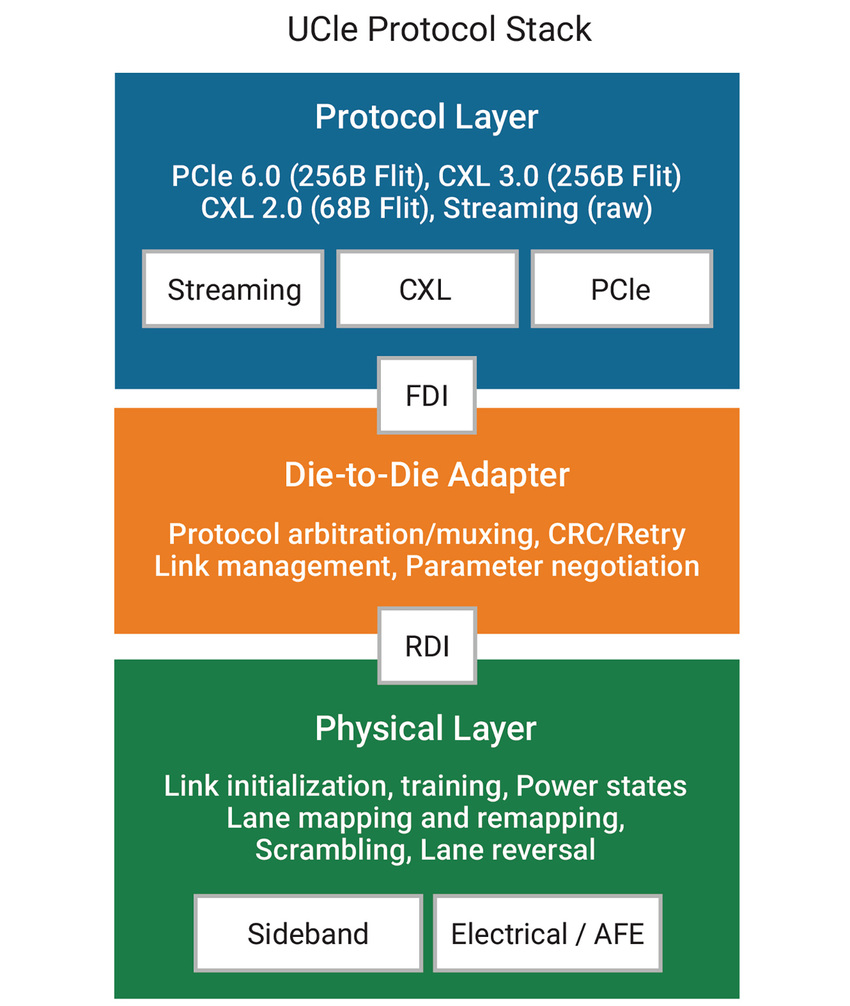

UCIe协议栈 / UCIe联盟

在第一版UCIe 1.0规范中,联盟定义了die-to-die I/O的物理层和协议,同时还有利用另外两大行业标准PCIe和CXL的软件栈模型。不过第一版仅仅只针对的是2D和2.5D的芯片封装,并没有对一些3D die-to-die 技术提供定义,毕竟这类3D封装技术还是仅限于部分先进制造厂商,且技术路线各有不同,但UCIe联盟仍在进行相关的努力。

不过即便是只有2D和2.5D封装,UCIe也展现出了可观的带宽性能,根据今年ISC2023上公布的数据,2D封装下的Chiplet可以实现4通道73GB/s的带宽,而2.5D封装下的Chiplet可以实现32通道630GB/s的带宽。这样的密度意味着其能效要远远大于标准的PCIe 5.0板载连接。

近日,UCIe联盟也终于发布了1.1版本的新规范,为Chiplet生态系统又带来了一些改进,尤其是针对汽车行业。比如预测性失效分析和健康度检测等,都是汽车这类高可靠性应用中的关键特性。同时,1.1版本还引入了新的凸点图降低了封装成本。相信随着UCIe规范的发展,以及越来越多的公司加入这一联盟,过去的共享IP池也能逐渐变为未来的共享Chiplet池。

写在最后

即便Chiplet技术对于整个行业来说,是又一次设计效率的蜕变,但我们也需要提防设计创新思维的僵化。未来基于第三方Chiplet打造的芯片会越来越多,却很有可能依然打着“完全自研”的旗号。Chiplet的存在无疑让设计公司对可靠IP的选择变得更加灵活,避免了重复造轮子的问题,即便如此,我们还是应该避免设计同质化的问题,这样对于市场多样性和创新发展来说,也能起到更大的推进作用。

-

chiplet

+关注

关注

6文章

434浏览量

12619

发布评论请先 登录

相关推荐

高性能KPC354x国产光电耦合器:适用于现代应用

Chiplet或改变半导体设计和制造

Chiplet技术有哪些优势

Chiplet将彻底改变半导体设计和制造

BGA芯片的封装类型 BGA芯片与其他封装形式的比较

名单公布!【书籍评测活动NO.43】 算力芯片 | 高性能 CPU/GPU/NPU 微架构分析

突破与解耦:Chiplet技术让AMD实现高性能计算与服务器领域复兴

西门子EDA创新解决方案确保Chiplet设计的成功应用

技术巅峰!探秘国内高性能模拟芯片的未来发展

构建高性能计算芯片

高端性能封装技术的某些特点与挑战

高性能可编程直流电源 在AFE、射频、激光器芯片测试中的应用

从设计到制造,Chiplet何以成为高性能芯片设计的首选

从设计到制造,Chiplet何以成为高性能芯片设计的首选

评论