1、set_output_delay的本质

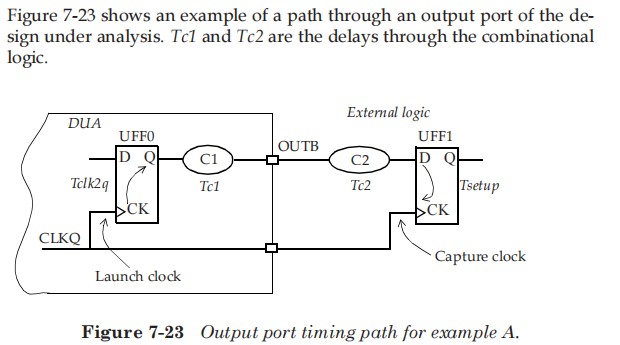

set_output_delay是对模块output信号在模块外部延迟的约束,本质上EDA工具会根据约束调整内部器件(UFF0)的类型,摆放位置以及组合逻辑(C1)以满足约束要求,即EDA工具保证模块DUA的UFF0的Tclk2q+Tc1延时能够满足约束要求。

约束指导原则:尽量照顾设计外部逻辑延时

max 正值尽量大

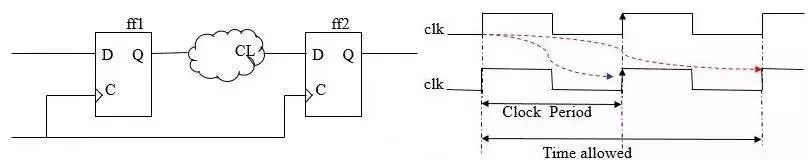

set_output_delay -max delay_vaule : delay_vaule 数值越大,对自身的约束越严格,对外部的要求越宽松,本质上是对setup time的约束。

set_output_delay -min delay_vaule : delay_vaule 可以是负值,delay_vaule 数值越小,需要自身的延时(Tclk2q+Tc1)越大,本质上是对hold time的约束。delay_vaule 为0 表示要求信号的自身的延时(Tclk2q+Tc1)至少要大于capture(UFF1)的hold time。

2、set_output_delay示意图

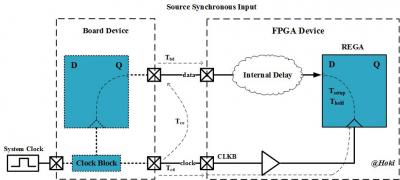

图7-23显示了DUA(the design under analysis )的输出路径。触发器UFF0在DUA内部,并向DUA外部的触发器UFF1提供数据。数据由UFF0的Q端输出,经过组合逻辑C1,通过输出端口OUTB输出经过组合逻辑C2到达UFF1。触发器UFF0和触发器UFF1的采样时钟均为CLKQ。不考虑CLKQ时钟偏移,该时钟周期是两个触发器UFF0和UFF1之间采样时间差。针对DUA输出管脚OUTB设置的set_output_delay指的就是相对于时钟CLKQ的Tc2延时加上UFF1的setup time延时。

set Tc2 3.9 set Tsetup 1.1 set_output_delay -clock CLKQ -max [expr Tc2 + Tsetup] [get_ports OUTB]

3、set_output_delay简单案例

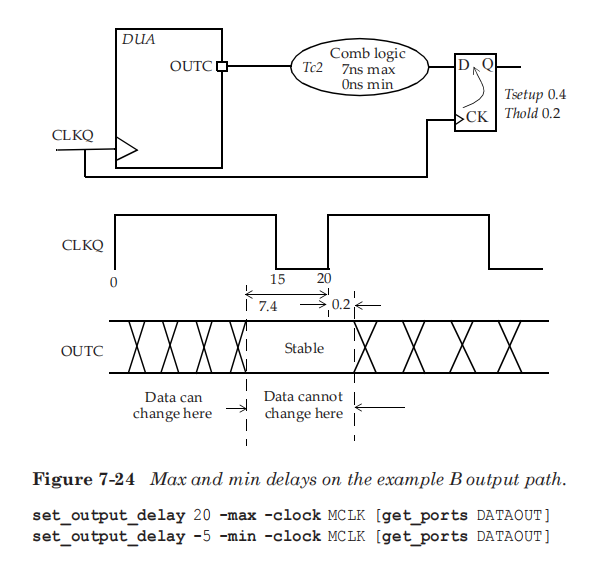

如图所示,组合逻辑Tc2的延时范围为0ns~7ns。外部触发器的Tsetup 为0.4ns,Thold为0.2ns,因此外部路径的最大延时为7.4ns (= max Tc2 plus Tsetup = 7 + 0.4),外部路径的最小延时为-0.2ns (= min Tc2 minus Thold = 0 - 0.2)。(PS:12nm~5nm工艺,hold time和setup time仅仅只有几十~十几ps。)

create_clock -period 20 -waveform {0 15} [get_ports CLKQ]

set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC]

set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]

审核编辑:刘清

-

EDA工具

+关注

关注

4文章

268浏览量

32228 -

触发器

+关注

关注

14文章

2027浏览量

61574 -

延时器

+关注

关注

1文章

36浏览量

15298 -

Dua

+关注

关注

0文章

3浏览量

7170 -

CLK

+关注

关注

0文章

127浏览量

17336

原文标题:浅谈时序:set_ouput_delay

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA设计约束技巧之XDC约束之I/O篇 (上)

Xilinx Vivado I/O延迟约束介绍

时序约束中如何精确找到匹配的template?

STM32上进行Delay延时的方法

详解FPGA的时序input delay约束

FPGA的虚拟时钟用于什么地方?

创建输入输出接口时序约束的窍门

介绍基本的sdc时序特例

怎样查看input/output delay是否生效

set_output_delay的本质是什么?浅谈set_ouput_delay时序

set_output_delay的本质是什么?浅谈set_ouput_delay时序

评论