如果你曾看过VexRSICV的设计,对于从事逻辑设计的你会惊讶从未想过逻辑设计还能这么来做。针对VexRSICV所衍生出的pipeline Lib,该系列会对pipeline进行一次梳理。诚如之前一篇博客曾讲,这是“勇者的游戏”。

虽然并未从事CPU设计,但这里pipeline的库读完还是当浮一大白~

》传统的设计思路

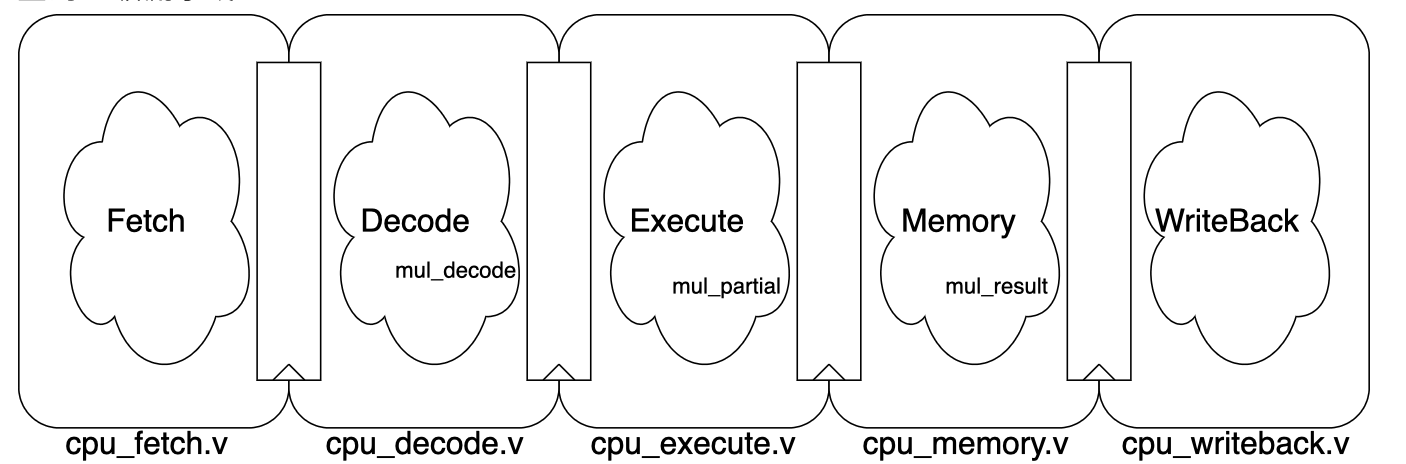

借用博客《The VexRiscV CPU - A New Way to Design》中的观点,在CPU设计里,一条典型的五级流水线:

在传统的流水线设计里,一条指令切分到不同的Stage中,每增加一条指令,我们可能就需要对各个Stage进行修改,牵一发而动全身。如果对于流水线每个阶段都了然于胸,那么自不是问题,否则那就是噩梦级别的难度了~。

那么,是否有新的方式来做一次流水线设计的创新呢?

来看看SpinalHDL里pipeline的设计思路。

》高端操作

本篇为开篇系列,先从整体架构上看SpinalHDL中pipeline的设计整体框架,暂不牵涉具体的设计细节。

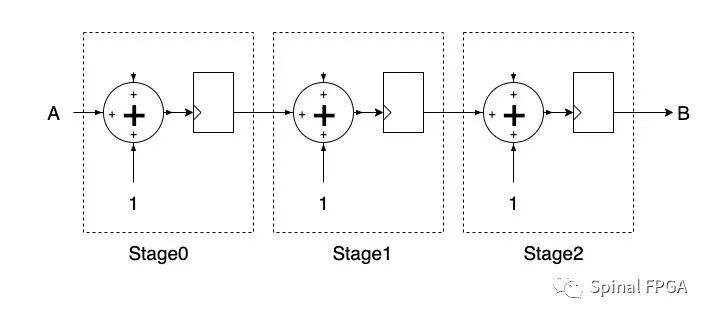

我们先来看一个非常简单的“pipeline”:

从A到B经历三级流水线,每经一级加一输出至下一级。

回到电路设计的本质。在FPGA里面,除了RAM、DSP这些资源,逻辑实现的核心只有LUT喝Reg。LUT负责实现逻辑实现,Reg负责状态保存。在上面的三级流水里,我们要思索的无非两个问题:

每一级流水线都做了什么

流水线各级是如何进行连接的

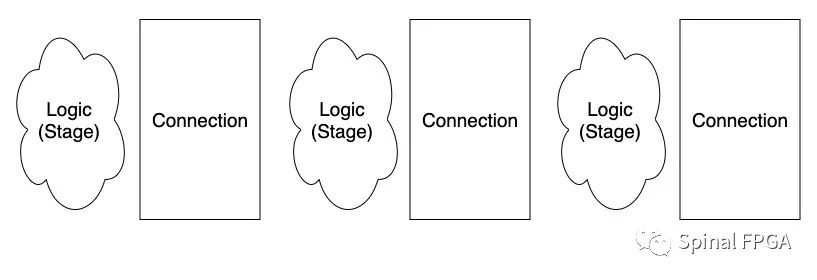

那么在看看上面的电路。每级流水线里面都是一个加法器和一个寄存器输出。加法器这些功能性的实现才是每一级Stage的功能。而寄存器则用于连接本级Stage与下一级Stage。也就意味着,每一级流水线都是逻辑电路负责实现功能,时序电路寄存器用于Stage连接。为此,对于pipeline我们可以抽象为下面的要素:

Stage:仅考虑具体的功能实现,它包含了输入、输出以及具体的逻辑实现。

Connection:仅用于实现各级Stage的连接。

在逻辑电路设计里,不要总是想着把功能实现和时序设计给拼到一块儿。将上面的概念与最上面的三级流水对照,那么加法器就是对应的Stage的功能,一个组合电路。而寄存器就对应Connection的功能。

SpinalHDL是基于Scala而设计,其能够帮助我们自动实现很多功能。比如两级Stage之间都有哪些信号是要通过Connection进行连接,对应的流水线功能如flush、halt能功能如何在各级Stage之间进行传播等功能。我们所需要做的,就是通过一定的规则告诉pipeline如何去做这些事情。

接下来,先针对pipeline所涉及的Pipeline、Stage、Connection、Stageable、StageableKey进行一个初步整体了解。

审核编辑:刘清

-

RAM

+关注

关注

8文章

1369浏览量

114805 -

加法器

+关注

关注

6文章

183浏览量

30162 -

Pipeline

+关注

关注

0文章

28浏览量

9372 -

CPU设计

+关注

关注

0文章

8浏览量

10552 -

FPGA开发板

+关注

关注

10文章

122浏览量

31552

原文标题:pipeline高端玩法(一)——系统架构

文章出处:【微信号:Spinal FPGA,微信公众号:Spinal FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

怎样使用SpinalHDL Pipeline组件里的resulting及overloaded?

在SpinalHDL里switch方法有何用处呢

在SpinalHDL里实现优雅的添加待跟踪波形信号

聊一聊SpinalHDL 1.6.1引入的blackbox inline功能

在SpinalHDL中关于casez的使用

分享一个在SpinalHDL里apply的有趣用法

SpinalHDL是如何让仿真跑起来的

如何在SpinalHDL里启动一个仿真

在SpinalHDL里有没有什么好的方式实现一个接口位宽转换呢

SpinalHDL里时钟域中的定制与命名

SpinalHDL里用于跨时钟域处理的一些手段方法

SpinalHDL里如何实现Sobel边缘检测

SpinalHDL里pipeline的设计思路

SpinalHDL里pipeline的设计思路

SpinalHDL里pipeline的设计思路

评论