问题:

请简述同步复位与异步复位的区别,说明两种复位方式的优缺点,并解释“异步复位,同步释放”。

简答:

1. 同步复位与异步复位的区别

同步复位是指在时钟沿变化时,复位信号满足复位条件,系统将完成复位动作;异步复位时钟复位信号不依赖与时钟,只要满足复位条件,系统就完成复位动作。

2. 同步复位的优缺点

优点:

有利于基于周期的仿真工具的仿真;

有利于静态时序分析工具的分析,可以综合出较高的工作频率;

抗干扰能力高,可以剔除复位信号中高于时钟频率的毛刺;

缺点:

复位依赖于时钟信号,当时钟信号出现故障时,系统将无法正常复位;

占用更多内部逻辑资源,逻辑门时延较高:由于多数逻辑器件的目标库内的D触发器只有异步复位端口,所以综合器在综合同步复位时将在寄存器的输入端口插入组合逻辑;

复位信号的有效脉冲宽度必须大于时钟周期:由于线路的时钟延时和路径延时,所以需要多个时钟周期的复位脉冲宽度,并且不能保证复位信号到达各个寄存器的时序。

3. 异步复位的优缺点

优点:

复位信号不依赖于时钟信号,电路在任何情况下都能实现复位;

节约内部逻辑资源,设计实现简单:由于多数逻辑器件的目标库内的D触发器都有异步复位端口,所以复位端口不需要设计额外的逻辑资源。

缺点:

复位信号对电路内的毛刺敏感,容易受到外界的干扰,出现频繁复位现象;

复位信号异步释放的随机性可能导致时序违规,当复位信号释放在时钟有效沿附近时,触发器输出可能处于亚稳态,导致复位操作失败;

不利于静态时序分析工具的分析,如果复位信号不是直接来自于 I/O 引脚,在 DFT (Design For Test)扫描和测试时,复位信号必须被禁止,因此需要添加额外的同步电路。

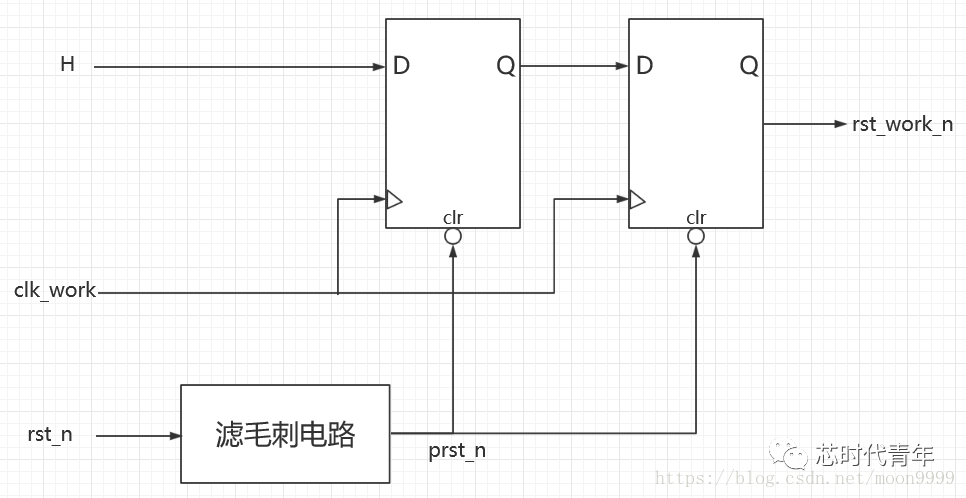

4. 异步复位 同步释放

复位设计通常采用“异步复位,同步释放”的方式:复位信号的到来与时钟信号无关,保证复位信号采集的可靠性;复位信号的释放发生于下一个时钟周期,有效防止复位信号释放时可能产生的亚稳态。

审核编辑:汤梓红

-

时钟

+关注

关注

10文章

1732浏览量

131437 -

触发器

+关注

关注

14文章

2000浏览量

61124 -

同步复位

+关注

关注

0文章

27浏览量

10710 -

异步复位

+关注

关注

0文章

47浏览量

13311

原文标题:FPGA逻辑题目001——同步复位与异步复位的区别

文章出处:【微信号:Carlinx FPGA,微信公众号:Carlinx FPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

同步复位与异步复位的区别

同步复位与异步复位的区别

评论