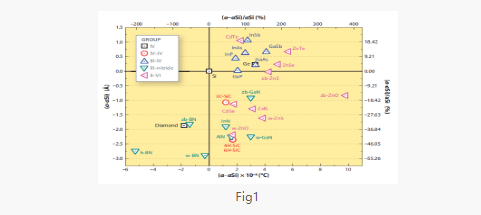

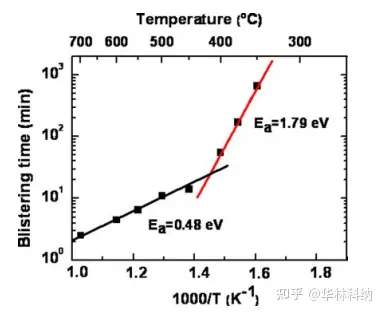

定制化合物半导体并将其集成到外国衬底上的能力可以带来卓越或新颖的功能,并对电子、光电子、自旋电子学、生物传感和光伏的各个领域产生潜在影响。这篇综述简要描述了实现这种异质集成的不同方法,重点介绍了离子切割工艺,也称为商业上的Smart CutTM工艺。该工艺结合了半导体晶片键合和使用光离子注入缺陷工程的底切。只要满足一系列技术标准,就可以生产出直接外延生长通常无法实现的体质量异质结构,从而在异质和柔性器件的设计和制造中提供了额外的自由度。离子切割是一种通用工艺,可用于从各种晶体中分离和转移精细的单晶层。介绍了材料和工程问题,以及我们目前对其应用于从独立的GaN、InP和GaAs晶片上切割薄层所涉及的基本物理的理解。

在他最近对技术本质的分析中,Arthur提出,所有技术都源于先前存在的技术,因此技术进步的本质是基于早期技术和精细技术的新组合。Arthur提出的组合进化概念与本综述的主题有关,即通过晶片键合和薄层转移实现化合物半导体(CS)的异质集成。将基于CS的器件结合到传统Si技术中的可能性引发了人们的兴趣激增,这是由于这种异质集成可能实现的新颖和改进的功能。在这种情况下,电荷载流子迁移率(与Si相比)高得多,以及一些CS由于其直接带隙(与Si的间接带隙相比)而有效发光,是异质器件发展的两大驱动力。

在大约半个世纪的时间里,器件缩小规模是提高硅金属氧化物半导体场效应晶体管(MOSFET)性能的最重要策略。然而,保持这种无情的小型化进程对未来的技术节点来说是非常具有挑战性的。这一点在2007年版的《国际半导体技术路线图》(ITRS)中得到了明确的证明,该路线图确定了半导体行业的技术挑战。例如,为了满足在10nm栅极长度及以下的高规模MOSFET的性能和功率要求,在源端具有增强的热载流子速度和注入的准弹道操作似乎是必要的。最终,可能需要引入新的器件结构,例如Si上的高传输Ge或CS沟道。如表1所示,与Si相比,几种CS具有高得多的电子迁移率。这激发了几种非Si晶体管的发展。从20世纪60年代中期开始,GaAs是第一个用于制造MOSFET的CS。诸如InP、GaAs、GaN的几种CS及其三元和四元合金(InGaAs、InAlAs、AlGaN、InGaP、InGaAsN、AlGaAs和GaAsSb)以及SiGe合金已经用于制造异质结双极晶体管。除了GaAs,GaN和InAs在高电子迁移率晶体管(HEMT)的制造中也引起了人们的极大关注。在最近的一项进展中,英特尔研究人员揭示了一种基于GaAs上InSb量子阱的新型超高速晶体管。尽管几十年前就已经认识到CS器件相对于Si器件的优势,但与Si结合的CS仅包含在2003年及以后的ITRS中。这是由于将非Si材料结合到互补金属氧化物半导体(CMOS)晶体管中以提高其性能并提高其能效的必要性日益增加。

异质集成的另一种外延形式是在硅上生长自组装CS纳米线。在所有合成方法中,气相-液相-固体(VLS)工艺在产生高密度单晶纳米线方面最成功。在这个过程中,纳米线的生长是通过液态金属簇实现的,该液态金属簇在催化作用下充当气相反应物吸收的能量有利位点,并且在饱和时充当结晶和一维生长的成核位点。在20世纪90年代初,Hiruma及其同事首次证明了使用Au作为催化剂,通过VLS工艺生长GaAs和InAs纳米线。最近,几个小组报道了在硅上生长无缺陷单晶CS纳米线的情况。尽管自组装纳米线可以避免工程异质外延层中面临的晶格和热失配问题,但由于涉及尺寸、位置、分布、,以及生长纳米线的取向,以及CS薄膜器件相关加工中面临的上述问题。

在不需要直接外延的情况下,可以通过使用晶片键合和层转移技术来实现不同半导体材料在同一平台内的组合。在第一步中,供体晶片和宿主晶片紧密结合以形成单个实体(92–94)。通常,这可以通过遵循图2中所示的不同粘合过程之一来实现。结合工艺的选择通常取决于初始基底的性质、它们对温度的耐受性以及最终应用。原则上,各种材料可以独立于它们的结构(单晶、多晶、非晶)、它们的晶体取向和它们的晶格参数而结合。由于篇幅有限,我们不讨论粘合过程的历史和基本问题,而是引导读者阅读相关书籍和评论文章。

为更好的服务客户,华林科纳特别成立了监理团队,团队成员拥有多年半导体行业项目实施、监督、控制、检查经验,可对项目建设全过程或分阶段进行专业化管理与服务,实现高质量监理,降本增效。利用仿真技术可对未来可能发生的情况进行系统的、科学的、合理的推算,有效避免造成人力、物力的浪费,助科研人员和技术工作者做出正确的决策,助力工程师应对物理机械设计和耐受性制造中遇到的难题。

审核编辑 黄宇

-

半导体

+关注

关注

334文章

26988浏览量

215997 -

晶体管

+关注

关注

77文章

9629浏览量

137808 -

GaN

+关注

关注

19文章

1917浏览量

72940

发布评论请先 登录

相关推荐

苏州华林科纳半导体设备技术有限公司招贤纳士

详解:半导体的定义及分类

III-V族化合物,III-V族化合物是什么意思

我国应把握5G 机遇,加速提升化合物半导体产业竞争力

一文解读化合物半导体产业发展形势及前景

化合物半导体应用前景及最新应用

集成电路产业深刻变革催化着化合物半导体市场的发展

从英国化合物半导体中心看化合物半导体集群

国内化合物半导体集成电路市场前景分析

LEKIN完成对LG Innotek光电化合物半导体资产的收购

华林科纳研究化合物半导体中离子注入引起的起泡和薄层分裂现象学

华林科纳的化合物半导体异质集成

华林科纳的化合物半导体异质集成

评论