作为IC设计人员,熟练掌握数字前端语法检查工具Spyglass的重要性不言而喻,本文讲解景芯SoC的Spyglass检查。

启动Spyglass软件:spyglass &

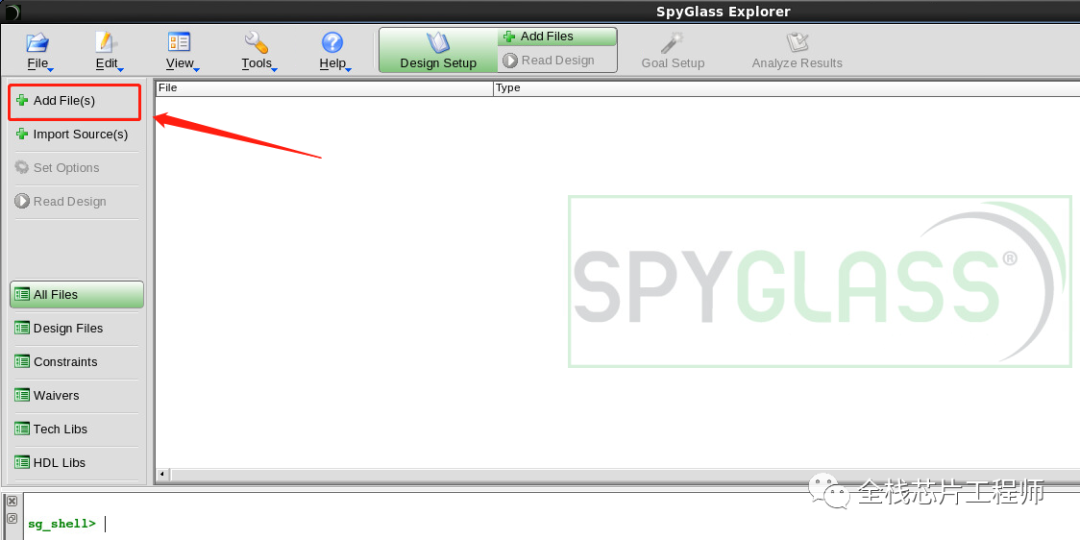

点击左边Add File(s):

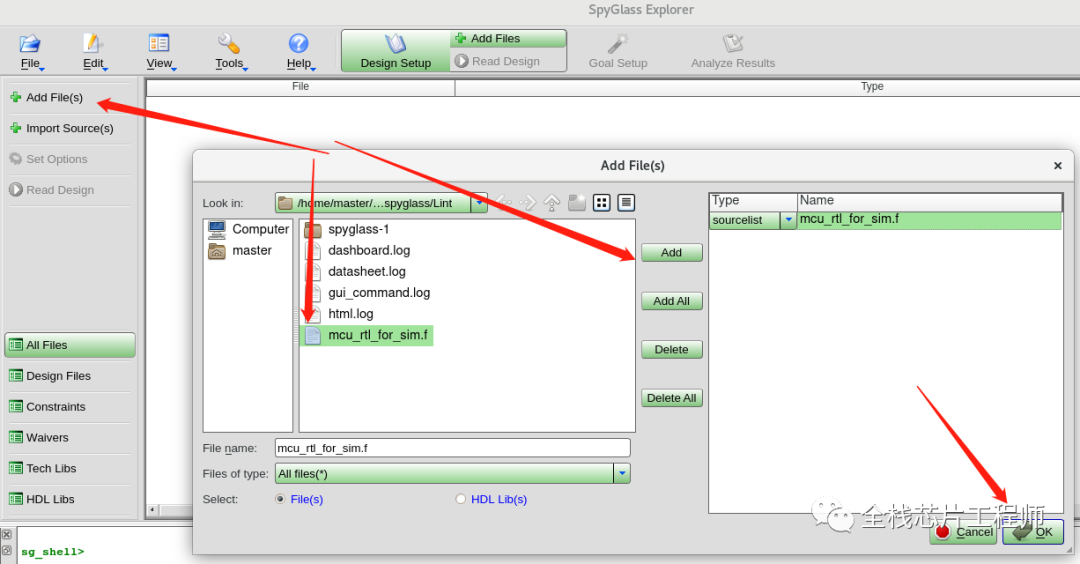

将.v文件通过rtl.f统一添加,如下图,点击OK:

或者通过命令添加:

sg_shell> read_file -type sourcelist mcu_rtl_for_sim.f

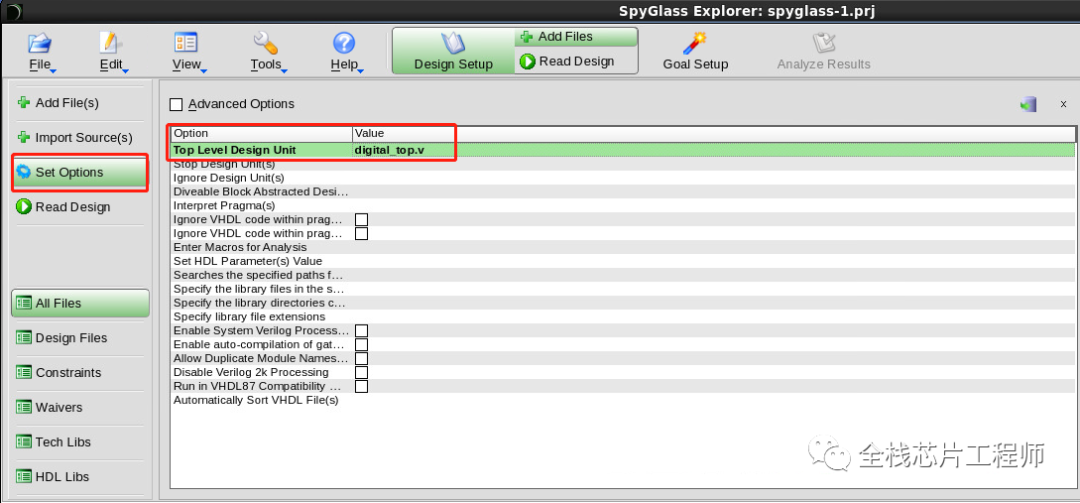

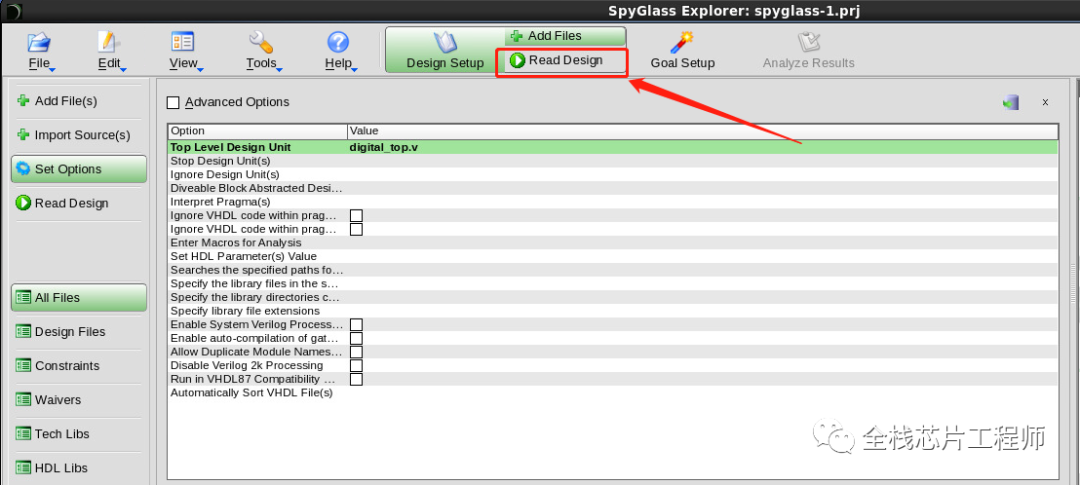

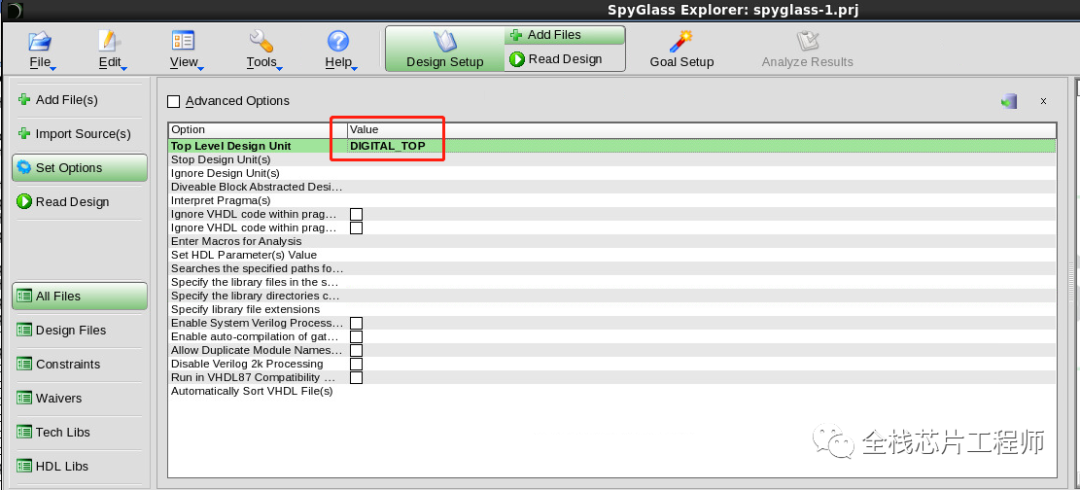

设置顶层,选中下图左边Set Options,手动设置Value为digital_top.v,这里我们留一个bug,后面看得到。

或者通过命令添加:

sg_shell> set_option top digital_top.v

我们也可以默认缺省顶层文件,此处,我们暂时不用remove_option top命令,注意刚才我们留了一个bug。

sg_shell> remove_option top

点击Read Design,

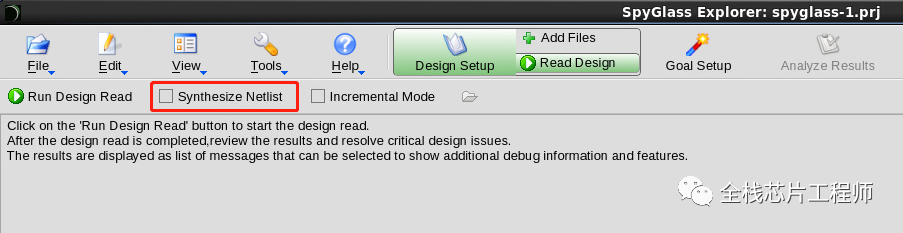

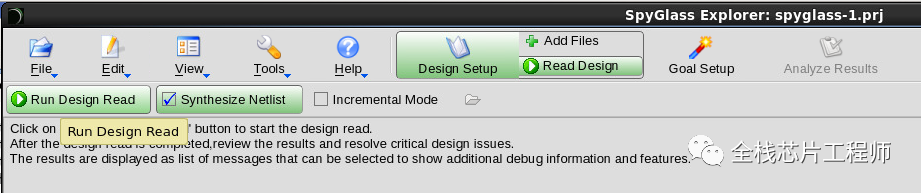

选择SynthesizeNetlist,在读入设计的同时进行综合

点击Run Design Read:

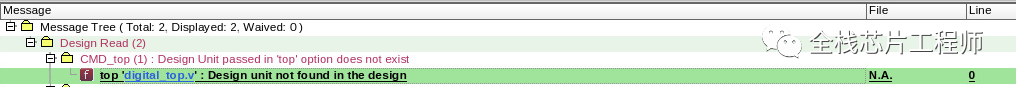

读取完成发现:

top 'digital_top.v' : Design unit not found in the design

bug来了,什么问题呢?找不到Design unit, 这是培训的同学经常发生的错误,顶层是指module名,不是module文件名。如下图所示:

也就是说设置Top level Design Unit的value为DIGITAL_TOP, 而不是digital_top.v。

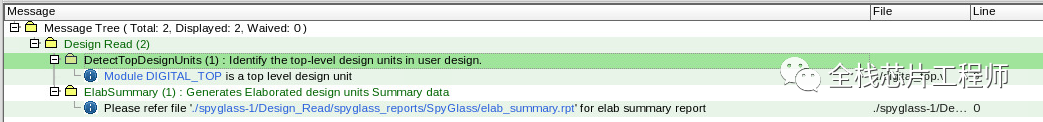

再次Run Read Design,如下图,读取成功。

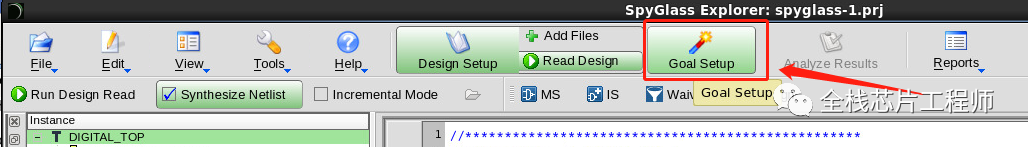

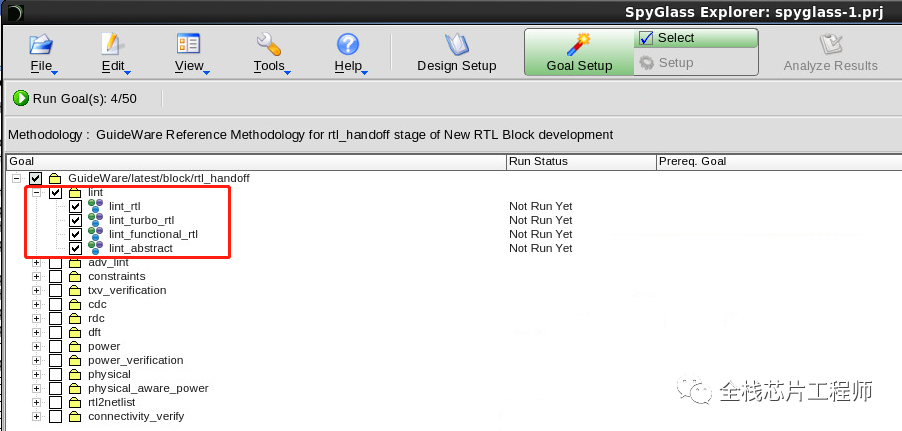

接着,设置Goal Setup:

首先选中lint,我们先看lint, 点击Run Goal:

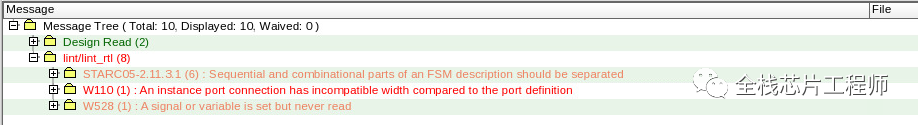

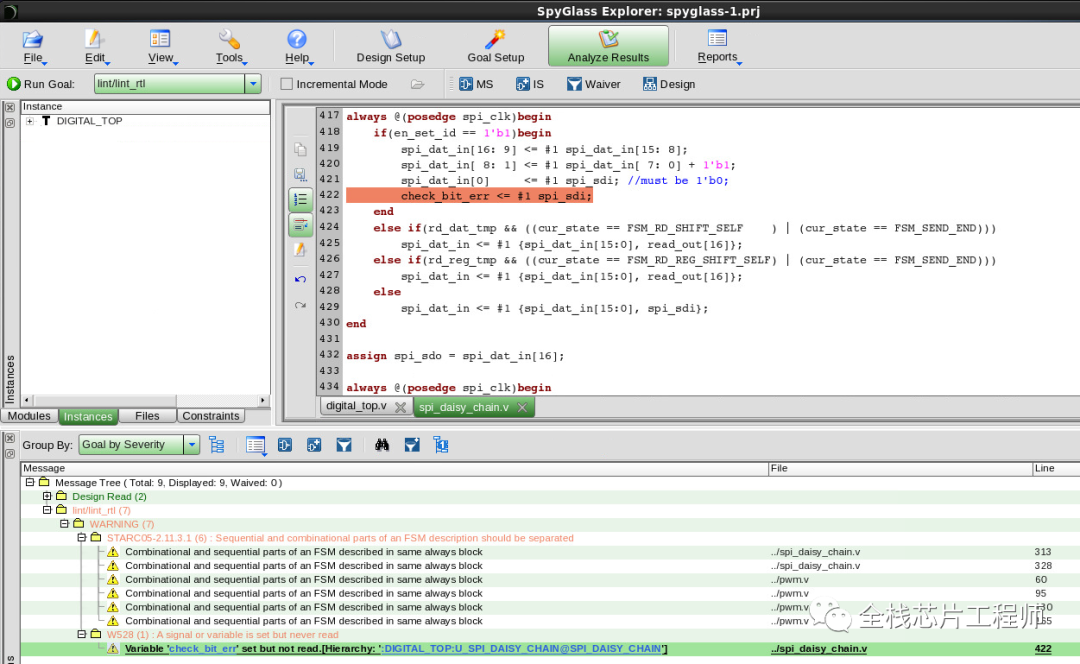

运行得到结果如下,我们开始逐一解析错误的原因,并给出RTL修改办法,具体参见知识星球。

在看到一条条lint Warning信息后,怎么才能更清晰地知道warning的具体原因呢?告诉你一个好习惯!

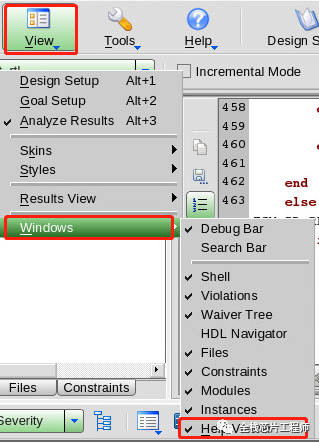

Spyglass的Analyze Results默认GUI界面如下,

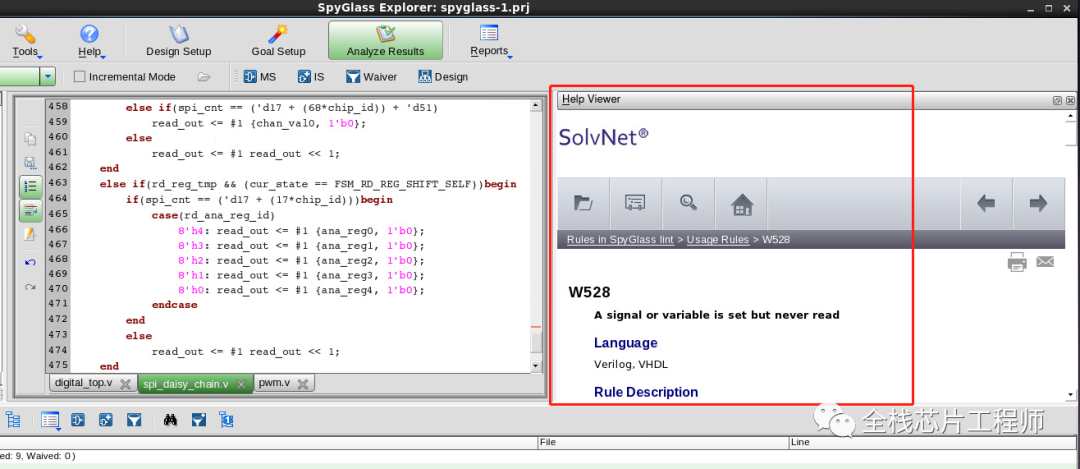

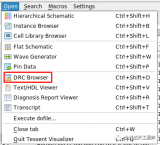

我们通过View-> Windows -> Help Viewer 来查看SolvNet对每个RTL lint warning类型的解释。

举个例子:

W528 : A signal or variable is set but never read

W528是Warning类型,说一个信号或者变量没有负载。

举个例子:

信号bigbus在第一个assign statement中被赋值了256bit位宽,但是在第二个assign statement中,bigbus仅128 bits (2**(13-7+1) 或者 2**(6-0+1)) 会被选择。因此,W528 的warning message就会出现。

module test1 (a, b); input [13:0] a; output [1:0] b; wire [255:0] bigbus; assignbigbus={{16{4'h0}},{16{4'h0}},{16{4'h0}},{16{4'h0}}}; assign b={bigbus[a[13:7]],bigbus[a[6:0]]}; endmodule

那么上面代码应该怎么修改才能避免这个warning message呢?答案参见全栈芯片工程师】知识星球。

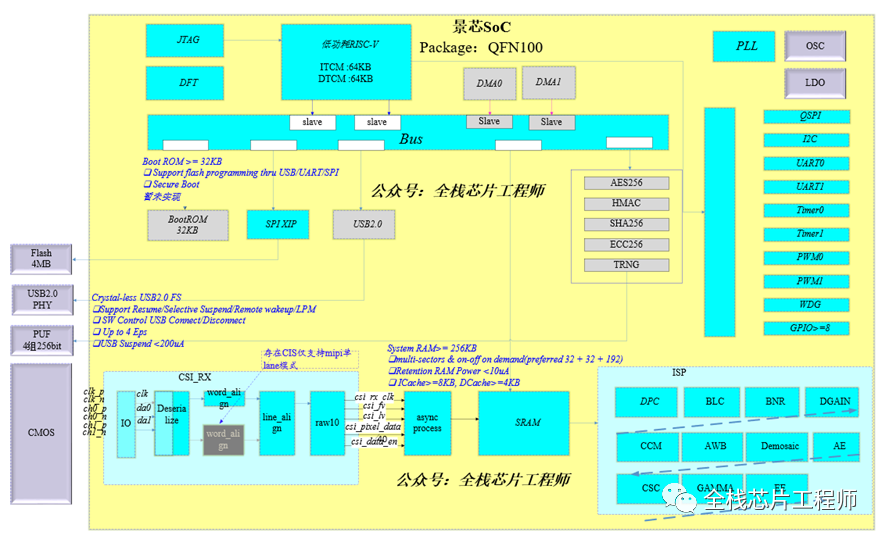

【全网唯一】景芯SoC是一款低功耗ISP图像处理SoC,采用低功耗RISC-V处理器,内置ITCM SRAM、DTCM SRAM,集成包括MIPI、ISP、CNN、QSPI、UART、I2C、GPIO、百兆以太网等IP,采用SMIC40工艺设计流片。

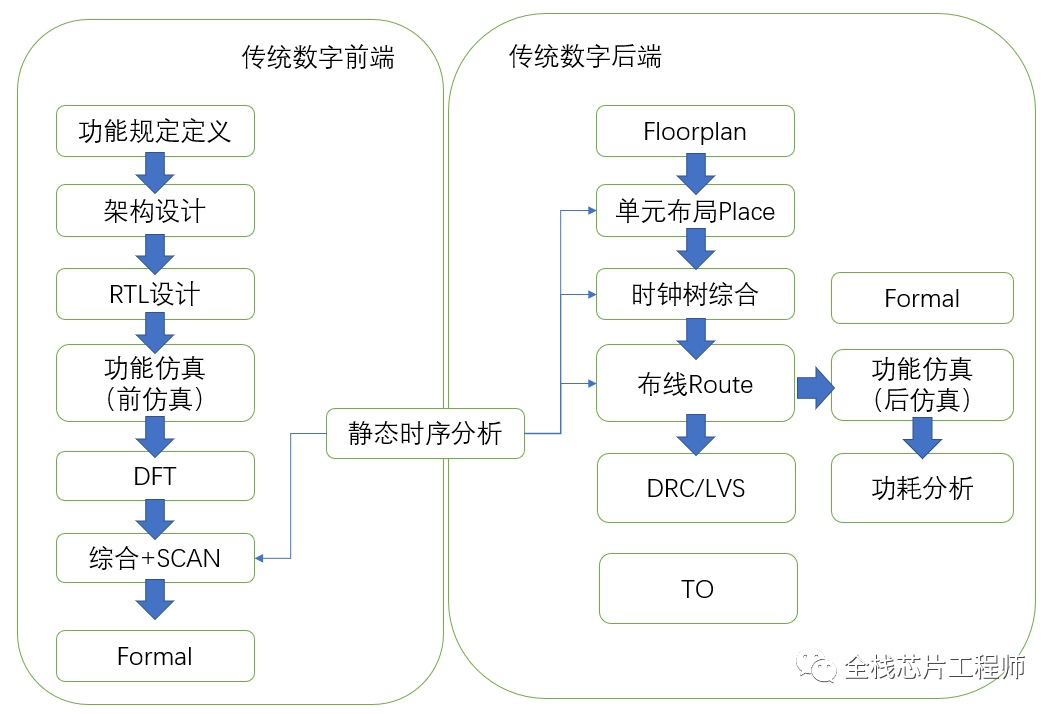

培训数据包括SoC前端设计、DFT设计、低功耗UPF设计、布局布线,提供服务器供大家实践!带你从算法、前端、DFT到后端全流程参与SoC项目设计。更多内容,请报名登录服务器实践,工程数据分割为如下三个部分。

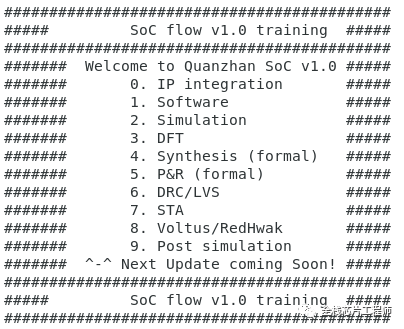

一键式完成C代码编译、仿真、综合、DFT插入、形式验证、布局布线、寄生参数抽取、PT分析、DRC/LVS、后仿真、形式验证、功耗分析等全流程。V1.0工程仿真如下。

SoC一键式执行flow

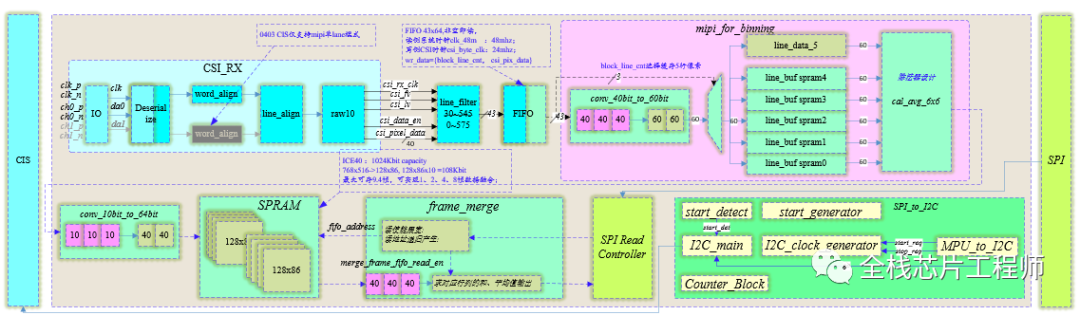

MIPI设计

ISP图像处理

dpc - 坏点校正

blc - 黑电平校正

bnr - 拜耳降噪

dgain - 数字增益

demosaic - 去马赛克

wb - 白平衡增益

ccm - 色彩校正矩阵

csc - 色彩空间转换 (基于整数优化的RGB2YUV转换公式)

gamma - Gamma校正 (对亮度基于查表的Gamma校正)

ee - 边缘增强

stat_ae - 自动曝光统计

stat_awb - 自动白平衡统计

仿真结果:

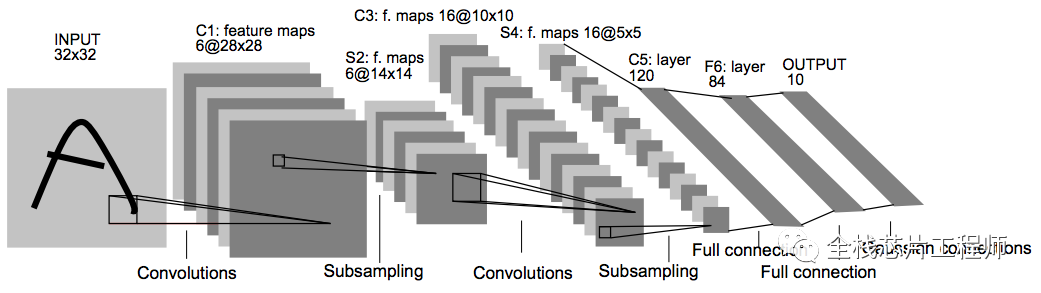

CNN图像识别

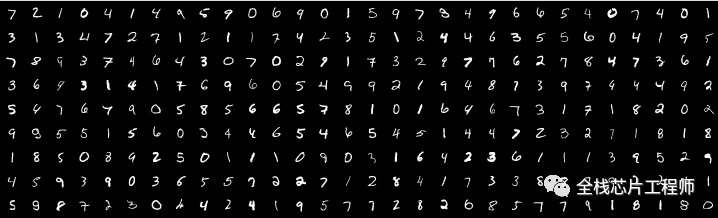

支持手写数字的AI识别:

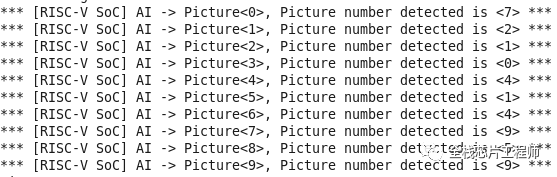

仿真结果:仿真识别上图7、2、1、0、4、1、4、9

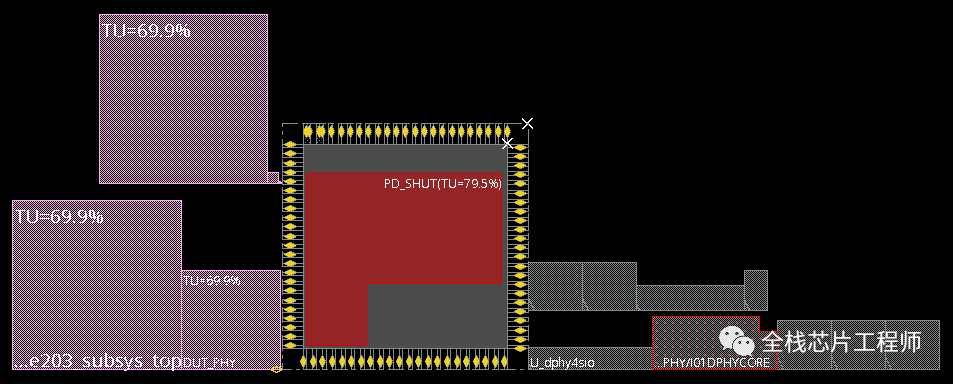

UPF低功耗设计

支持UPF低功耗设计(含DFT设计):

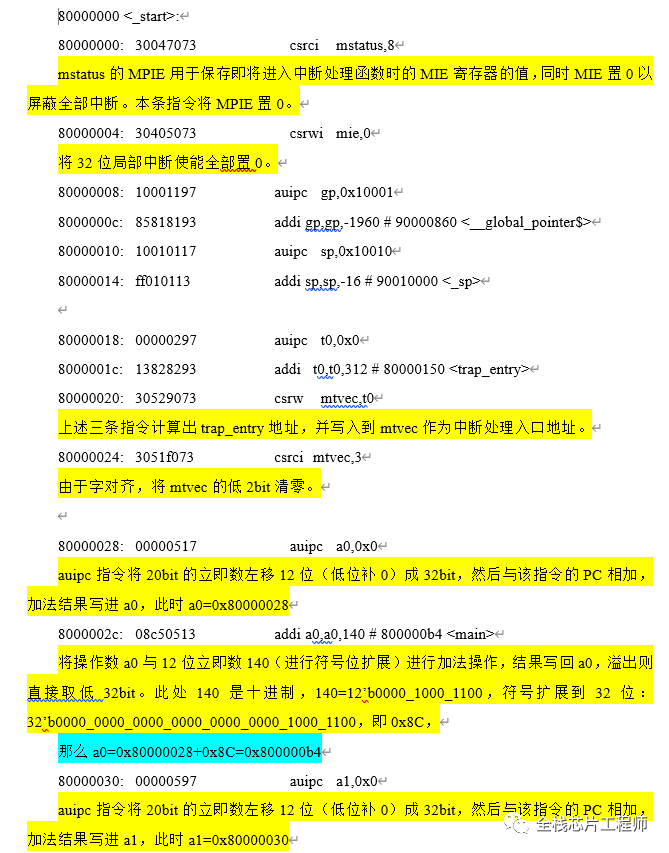

CPU启动指令分析

审核编辑:汤梓红

-

IC设计

+关注

关注

38文章

1405浏览量

108405 -

soc

+关注

关注

40文章

4619浏览量

230087 -

命令

+关注

关注

5文章

758浏览量

23914

原文标题:Spyglass检查(一)

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

重庆电感供应/锰芯共模电感-谷景电子

重庆电感器厂家/锰芯共模电感器-谷景电子

分享一些语法检查的工具

SOC、MCU工作不起来要检查哪些硬件问题

芯愿景成科创板首个EDA公司?

EDA厂商芯愿景终止深交所主板IPO

详解Spyglass使用(一)

详解Spyglass使用(二)

手把手教你学习Spyglass工具

景芯SoC/MCU v2.0重磅升级!9.1号涨价了

景芯SoC的Spyglass检查

景芯SoC的Spyglass检查

评论