小编在本节完整给出一个设计过程,可利用ISE或Vivado硬件编程软件实现。

1 HDL代码、逻辑电路和器件

- 编写“HDL代码”来描述电路功能

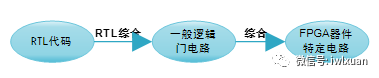

- EDA工具中进行“RTL综合”和“综合”

“RTL综合”将HDL代码转换为逻辑电路

“综合”这一步将经过“RTL综合”后的门电路映射为FPGA器件的物理结构 - “实现”这一步将对FPGA器件进行最终的布局布线

- 综合实现的结果将会被转换为可以最终运行在FPGA器件上的二级制烧录文件

2 HDL代码实例

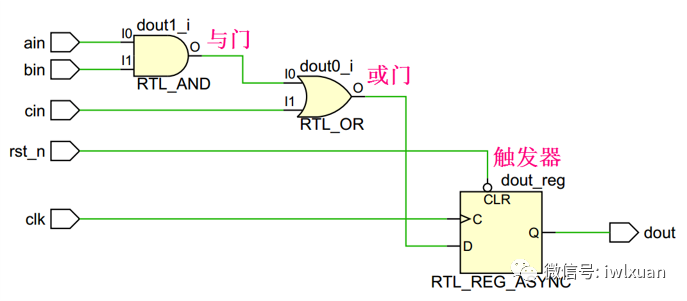

- 在每个时钟clk信号的上升沿,实现输出信号dout的值为输入信号ain、bin和cin的2级门运算的结果

- 这个门运算先是ain和bin“逻辑与”,它们得到的结果再和cin“逻辑或”

- 输入复位信号rst_n为异步复位信号,任何时刻这个信号的下降沿将直接触发输出信号dot取值为0

举个栗子

module at7(

clk,rst_n,

ain,bin,cin,dout

);

input clk;

input rst_n;

input ain,bin,cin;

output reg dout;

always @(posedgeclk or negedgerst_n)

if(!rst_n)

dout <= 1'b0;

else

dout <= (ain & bin) | cin;

endmodule

3 RTL综合

- “RTL综合”后的逻辑电路原理图,它很好的以门电路的形式表达了我们的实例代码

- “RTL综合”门电路和HDL代码所描述的功能完全一致,大家对比下图和第2节的代码。下图即是代码RTL综合后的布局。

图1 RTL综合后的逻辑电路原理图

4 综合

- “RTL综合”是指将HDL代码转换为逻辑门电路形式来表达的一个过程;“综合”却是将已经用逻辑门关系表达的电路进一步转换为FPGA器件实际物理结构相对应的电路形式 “综合”电路中看不到任何的“门”

- “综合”的结果是所使用的特定FPGA器件中实际存在着的物理结构,如“输入缓冲”、“查找表”、“触发器”和“输出缓冲”等

图2 RTL综合与综合的关系

图3 综合后的逻辑电路原理图

5 实现

- 在“综合”给出HDL代码与实际FPGA器件的映射关系后,做具体执行的工作

- 如果把“综合”结果比喻为电路板设计的“原理图”阶段,那么“实现”这个步骤就是具体的“布局布线(layot)”阶段

图4 布线图

6 生成烧录文件

- 如同电路板的layout完成后要生成gerber,FPGA工具最终也要产生一个bit文件用于烧录到FPGA中运行了

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21748浏览量

603853 -

逻辑电路

+关注

关注

13文章

494浏览量

42641 -

HDL

+关注

关注

8文章

327浏览量

47404 -

代码

+关注

关注

30文章

4791浏览量

68681 -

Vivado

+关注

关注

19文章

812浏览量

66609

发布评论请先 登录

相关推荐

如何在FPGA上实现HDL代码完成MATLAB转换

如果您正在使用 MATLAB 建模数字信号处理(DSP)或者视频和图像处理算法,并且最终将其用于 FPGA 或 ASIC,本文可能将为你带来帮助。 从 MATLAB 生成 HDL 代码 FPG

如何使用Verilog HDL进行FPGA设计

FPGA设计流程是利用EDA开发软件和编程工具对FPGA芯片进行开发的过程。FPGA的设计流程如上图所示:包括设计定义、代码

发表于 04-04 10:29

•2352次阅读

FPGA设计中 Verilog HDL实现基本的图像滤波处理仿真

今天给大侠带来FPGA设计中用Verilog HDL实现基本的图像滤波处理仿真,话不多说,上货。

1、用matlab代码,准备好把图片转化成Vivado Simulator识别的

发表于 05-20 16:44

基于模型设计的HDL代码自动生成技术综述

、基于模型设计的HDL代码自动生成技术应用需求近年来,现场可编程门阵列(FPGA)被广泛应用于航空航天、汽车、通信、工业自动化、电机控制、医学成像等嵌入式应用领域。传统的FPGA上的数

发表于 06-08 09:29

FPGA双沿发送之Verilog HDL实现 精选资料推荐

1.1 FPGA双沿发送之Verilog HDL实现1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA双沿发送之

发表于 07-26 06:20

FPGA双沿采样之Verilog HDL实现 精选资料分享

1.1 FPGA双沿采样之Verilog HDL实现1.1.1 本节目录1)本节目录;2)本节引言;3)FPGA简介;4)FPGA双沿采样之

发表于 07-26 07:44

基于Verilog HDL语言的FPGA设计

采用 Verilog HDL 语言在Altera 公司的FPGA 芯片上实现了RISC_CPU 的关键部件状态控制器的设计,以及在与其它各种数字逻辑设计方法的比较下,显示出使用Verilog

发表于 08-21 10:50

•69次下载

Verilog HDL与VHDL及FPGA的比较分析

Verilog HDL与VHDL及FPGA的比较分析. Verilog HDL优点:类似C语言,上手容易,灵活。大小写敏感。在写激励和建模方面有优势。

发表于 01-11 10:45

•1380次阅读

MathWorks推出基于MATLAB生成HDL代码的产品

MathWorks 近日宣布推出 HDL Coder,该产品 支持MATLAB 自动生成 HDL 代码,允许工程师利用广泛应用的 MATLAB 语言实现

发表于 03-07 09:27

•2164次阅读

基本组合逻辑功能双向管脚的Verilog HDL源代码

电子发烧友网核心提示: 本例程是Verilog HDL源代码:关于基本组合逻辑功能中双向管脚的功能实现源代码。 Verilog HDL: B

发表于 10-15 11:28

•1613次阅读

MathWorks网络研讨会:高性能FFT的HDL实现与验证

Virtex-7 FPGA 上运行进行了优化)。演示的工作流程从参考 MATLAB 代码开始,强调了模型开发、定点转换、优化 HDL 代码生成以及

发表于 02-09 02:26

•378次阅读

System Generator实现串口通信(一行HDL代码都不用写)

一直都在System Generator下做图像处理相关的算法,感觉SysGen挺强大的,前几天突发奇想,能否直接用SysGen实现数据的通信呢,毕竟一句HDL代码都不写对于做FPGA

发表于 02-10 19:51

•2940次阅读

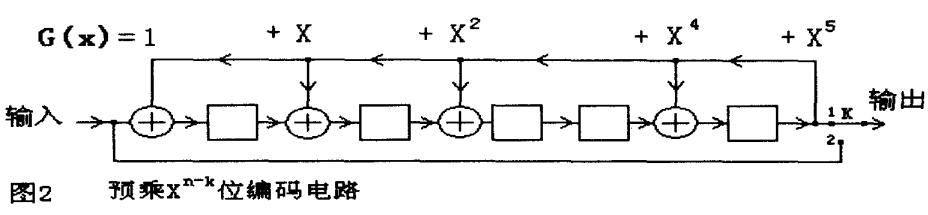

并行CRC电路HDL代码的快速生成

CRC校验的实现基于串行位移寄存器,如果要处理并行数据,需要对电路进行改进。本文介绍了一种并行CRC电路HDL代码的快速生成钟算法,只需要带入不同的参数,可自动生成不同长度以及并行度的并行CRC电路的

发表于 03-28 09:29

•16次下载

FPGA HDL代码实现过程

FPGA HDL代码实现过程

评论