小编在本节介绍FPGA芯片外围电路设计规范和配置过程,篇幅比较大,时钟的设计原则就有17条,伙伴们耐心读一读。

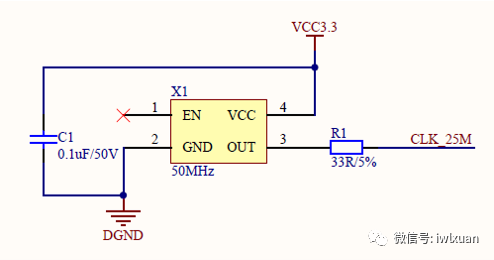

a. 时钟电路的设计选型需要考虑的因素

- 系统运行的时钟频率是多少?(可能有多个时钟)

- 是否有内部的时钟管理单元可用(通常是有)?它的输入频率范围(需要查看器件手册进行确认)?

- 尽可能选择专用的时钟输入引脚

图1 参考晶振设计

b. 时钟电路PCB layout设计原则

- 时钟晶振源应该尽可能放在与其连接的FPGA时钟专用引脚的临近位置

- 时钟线尽可能走直线。如果无法避免转弯走线,使用45度线,尽量避免T型走线和直角走线

- 尽量避免同时在多个信号层走时钟线

- 时钟走线尽量不要使用过孔,因为过孔会导致阻抗变化及反射

- 靠近外层的地层能够最小化噪声。如果使用内层走时钟线,要有良好的参考平面,且走带状线

- 时钟信号应该有终端匹配电路,以最小化反射

- 尽可能使用点到点的时钟走线

- 对于时钟差分对的走线,必须严格按照D>2S规则,以最小化相邻差分对间的串扰

- 确保差分对在整个走线过程中的线间距恒定

- 确保差分对的走线等长,以最小化偏斜和相移

- 同一网络走线过程中避免使用多个过孔,以确保阻抗匹配和更低的感抗

- 高频的时钟走线尽可能短

- 高频时钟或周期性信号尽可能远离高速差分对以及任何引出的连接器(例如I/O、数据或电源连接器)。

- 应当保证所有走线有持续的地和电源参考平面

- 为了最小化串扰,尽量缩短高频时钟或周期性信号与高速信号并行走线的长度。推荐的最小间距是3倍的时钟信号与最近参考面间距

- 当一个时钟驱动多个负载时,使用低阻抗传输线以确保信号通过传输线

- 信号换层时使用回路过孔

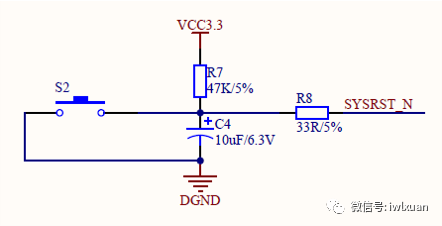

c. 复位电路设计原则

- 尽可能使用FPGA的专用时钟或复位引脚

- 上电复位时间的长短需要做好考量

- 确保系统正常运行过程中复位信号不会误动作

- 复位信号尽量不要靠近连接器附近,尤其是和面板连接的连接器,避免外部ESD误触发复位信号

图2 复位电路设计

d. 配置电路设计原则

- 配置芯片尽量靠近FPGA

- 考虑配置信号的完整性问题,必要时增加电阻做阻抗匹配

- 相关配置引脚正确的添加上拉或下拉电阻

- 部分配置引脚可以被复用,但是要谨慎使用,以免影响器件的上电配置过程

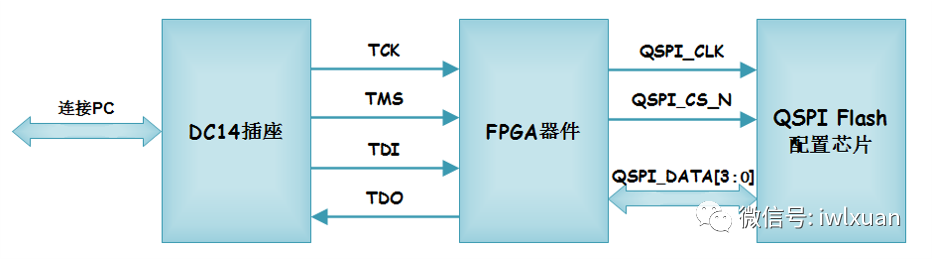

e. 配置电路框图

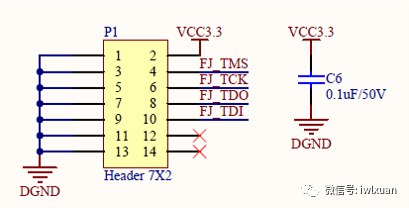

- DC14插座将FPGA器件的JTAG专用引脚TCK、TMS、TDI、TDO引出

- USB下载器连接DC14插座和PC机,实现FPGA器件的在线烧录或配置芯片(QSPI FLASH)的固化

- FPGA器件的固化代码可以存储在QSPI FLASH中,当FPGA器件每次上电时,都会直接从QSPI FLASH中读取固化代码并运行

图3 配置电路框图

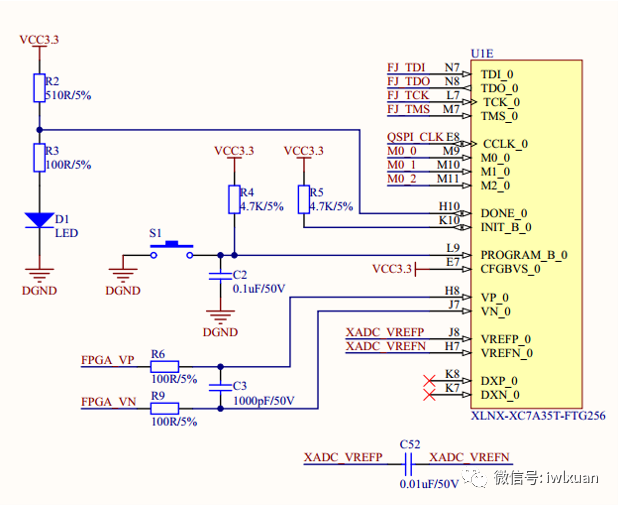

f. 配置电路设计

- MSEL0/MSEL1/MSEL2引脚设定FPGA器件在上电后直接进入QSPI FLASH加载的配置模式,MSEL0/MSEL1/MSEL2分别配置为不同设置对应不同加载方式

- 当JTAG在线配置FPGA时,FPGA器件都会优先运行JTAG最新烧录的代码

- INIT_B_0PROGRAM_B_0信号分别上拉到3.3V

- PROGRAM_B_0连接按键S1,可以通过这个按键使FPGA器件重新加载配置代码

- DONE_0信号指示当前FPGA的上电加载配置是否完成,通过指示灯D1的亮灭状态来示意

图4 配置电路

图5 JTAG电路框图

g. 供电电路设计

- VCCO为FPGA的IO接口电压

- VCCINT为FPGA的核心电压

- VCCADC为FPGA内部的AD转换电路的供电电压

- VCCAUX为FPGA的辅助电压

- VCCBRAM为FPGA内嵌的块RAM存储器的供电电压

- P2是跳线插座,若连接2.5V,对应Bank的IO电压可用于LVDS接口电平,若连接3.3V,则对应Bank的IO可作为LVTTL电平使用

h. 供电电路PCB layout设计

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1664文章

22509浏览量

639543 -

外围电路

+关注

关注

7文章

80浏览量

34364 -

时钟电路

+关注

关注

10文章

247浏览量

53958 -

FPGA芯片

+关注

关注

4文章

250浏览量

41124 -

PCB

+关注

关注

1文章

2357浏览量

13204

发布评论请先 登录

相关推荐

热点推荐

JTAG电路设计规范

JTAG电路设计规范:本技术设计规范根据国家标准和原邮电部标准以及国际标准IEEE STD 1149.1 系列标准编制而成。

目前,使用的芯片中越来越多的CPU、EPLD、FPGA、

发表于 09-19 07:40

•94次下载

华为同步电路设计规范

华为同步电路设计规范

为了增加可编程逻辑器件电路工作的稳定性,一定要加强可编程逻辑器件设计的规范要求,要尽量采用同步电路设计。对于设计中的异步

发表于 02-11 10:04

•128次下载

FPGA芯片外围电路设计规范和配置过程

FPGA芯片外围电路设计规范和配置过程

评论