本文转自TechSugar

感谢TechSugar对新思科技的关注

虽然摩尔定律走到极限已成行业共识,但是在现代科技领域中,先进制程芯片的设计仍是实现高性能、低功耗和高可靠性的关键。芯片开发者正在致力于研发更先进的芯片,一方面是在工艺制程不断推进,向3nm、2nm甚至是1nm进击;另一方面是采用新的架构,如Chiplet、2.5D/3D封装,将多芯片系统集成在一起。

无论是单片SoC还是多芯片系统,目前芯片的复杂度和挑战已经来到一个制高点。为了在日益竞争激烈的市场中脱颖而出,芯片开发者必须克服众多挑战,并采用先进的技术和工具来保证设计的最终实现。

工艺、电压、温度,先进制程芯片的“三大拦路虎”

当代芯片设计和制造正朝着大尺寸、高功耗、2.5D/3D封装、复杂互联、FinFET/GAA技术等方向发展。与此同时,为了满足市场需求和技术要求,还需要在设计过程中最大化处理性能利用率、优化功耗效率并提升芯片的可靠性。这些发展趋势给芯片设计和制造带来了一系列挑战。其中,工艺(process)、电压(voltage)和温度(temperature)(简称为PVT)正成为先进制程芯片设计中的“三大拦路虎”。

工艺:在先进制程芯片的演变过程中,随着晶体管密度的增加,新兴的FinFET和GAA(Gate-All-Around)技术在性能方面带来了巨大的潜力,但也需要应对工艺变异和制造复杂性等方面的挑战。再加上像Chiplet这种新型封装方式将不同工艺的芯片组合在一起,这可能导致性能和可靠性方面的不确定性。

温度:今天复杂的处理器芯片已经包含有1000多亿个晶体管,芯片上的晶体管数量还在增加,芯片的尺寸在不断变大。如此多晶体管的散热问题正成为困扰目前芯片开发者的一大难题,事实上,异构芯片中的逻辑芯片、存储器、功率器件以及电感器之间的热串扰也带来了前所未有的设计挑战。

2.5D/3D封装是现代先进芯片的主流封装方式之一,但这些先进封装技术在散热方面带来了巨大的挑战。在这些新型封装中,芯片在运行过程中可能会出现多个热点,即局部温度较高的区域,这可能导致散热不良和性能下降。

电压下降(IR):目前的芯片尺寸越来越小,但其中集成的晶体管数量却在不断增加,当芯片在高负载情况下运行时,电流流过如此多的晶体管会产生一定的电阻,从而引起电压下降问题,电压下降会造成一系列不良影响,包括信号完整性降低、时序噪声增加、功耗增加、性能下降等。随着芯片规模和复杂度的增加,电流的大小和波动性也会增加,从而导致电压下降问题更加显著。

此外,芯片在设计过程中还可能会因为用户需求、应用程序要求等原因发生变化,面临难以预测的工作负载的挑战。功率不确定性也是一大挑战,芯片的功率消耗也可能会出现波动,过高或过低的功率都会影响芯片的正常运行和性能。

PVT监控器:先进制程芯片成功的关键

面对上述众多挑战,芯片开发者的任务变得异常艰巨。芯片制造商已经不能再忽视芯片内部发生的情况,而且还需全面了解芯片在生命周期各个阶段的“一举一动”。为了确保芯片的高性能和高可靠性,需要对工艺、电压和温度(PVT)等参数进行监测和控制,一款良好的PVT监控器(monitor)将是解决这些问题的关键。

采用PVT监控器,就像是在芯片设计虚拟运行的过程中配备了“眼睛和耳朵”,PVT监控器能够实时感知和记录芯片的工艺、电压和温度状态。通过监测这些参数,开发者能够及时调整芯片的工作模式和参数,以确保芯片的正常运行。

因此,PVT监控器已经成为实现先进节点半导体器件可靠运行和最佳性能的关键所在。

作为全球领先的EDA厂商之一,新思科技一直致力于为芯片的全生命周期进行全方位的保驾护航。新思科技有着强大的硅生命周期管理(SLM)解决方案,而PVT监控IP也是SLM系列的一部分。这一解决方案建立在丰富的片内可观察性、分析和集成自动化的基础之上。它通过收集有意义的数据,在设备生命周期的每个阶段提供持续的分析和可操作的反馈,从而改善芯片健康和操作指标。

新思科技用于先进节点工艺技术的模块化SLM PVT IP/监控 IP

值得一提的是,新思科技已在台积公司的N5和N3E制程上成功完成了PVT监控IP测试芯片的流片,这是一个关键的里程碑:一方面,对于新思科技而言,IP对工艺和制造技术非常敏感,因此实现经过验证的芯片性能是赢得芯片制造商信任的很关键一步。

另一方面,经过验证的IP可以大幅节省设计周期和成本,当下芯片厂商之间的竞赛比以往任何时候都要激烈,新思科技经过硅验证的PVT监控IP将对准备采用台积公司N5和N3E先进制程工艺的客户受益。

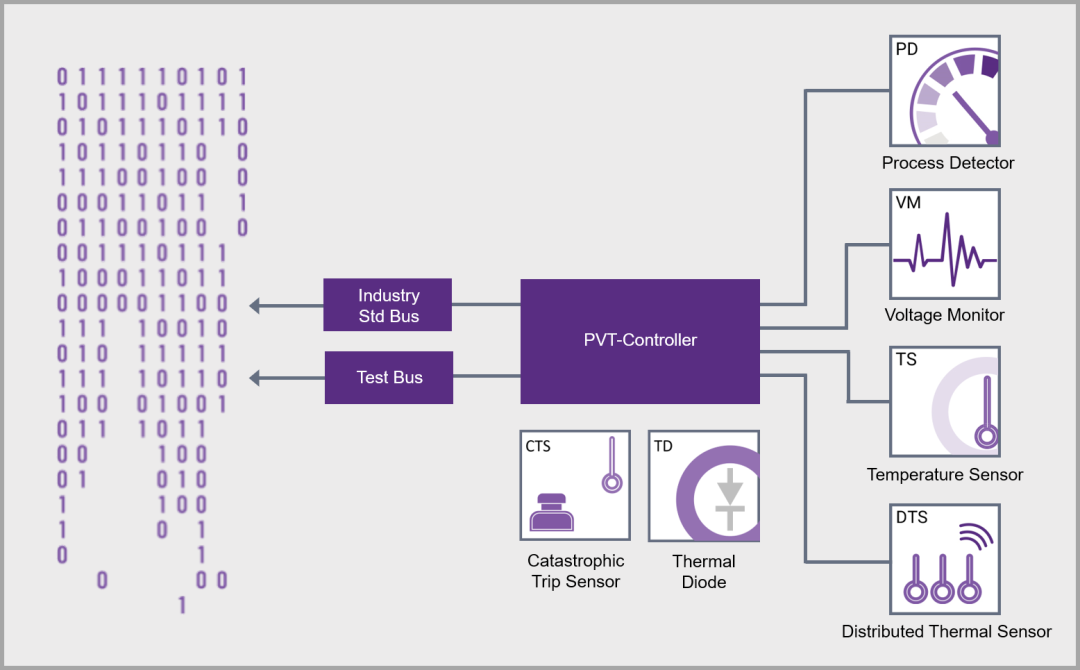

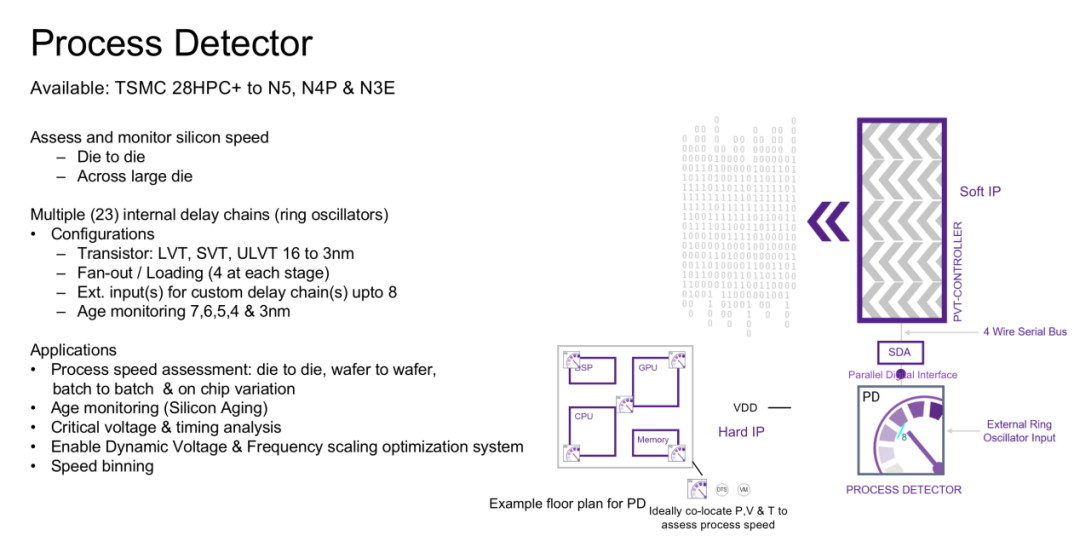

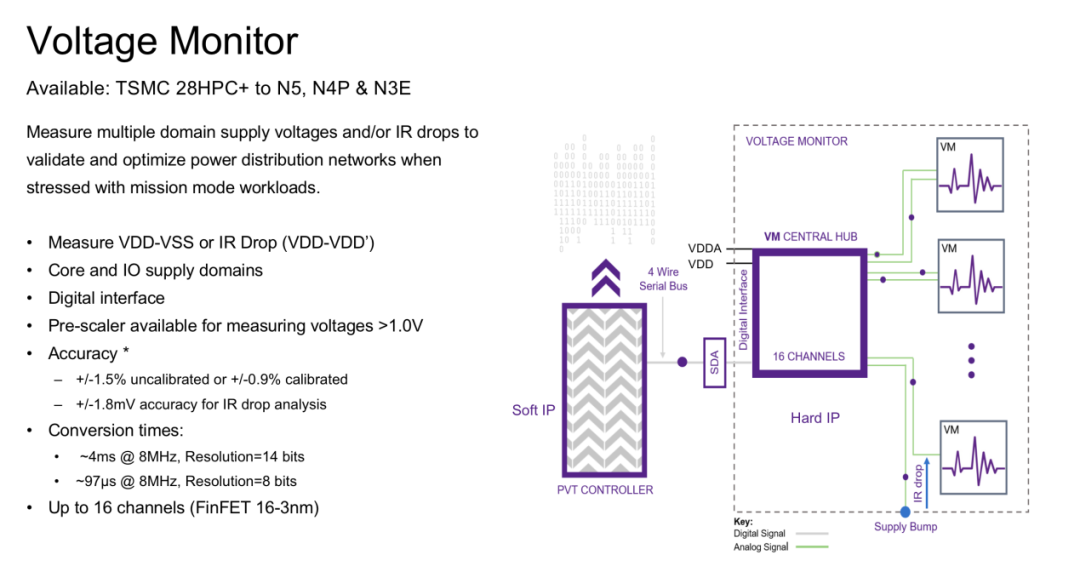

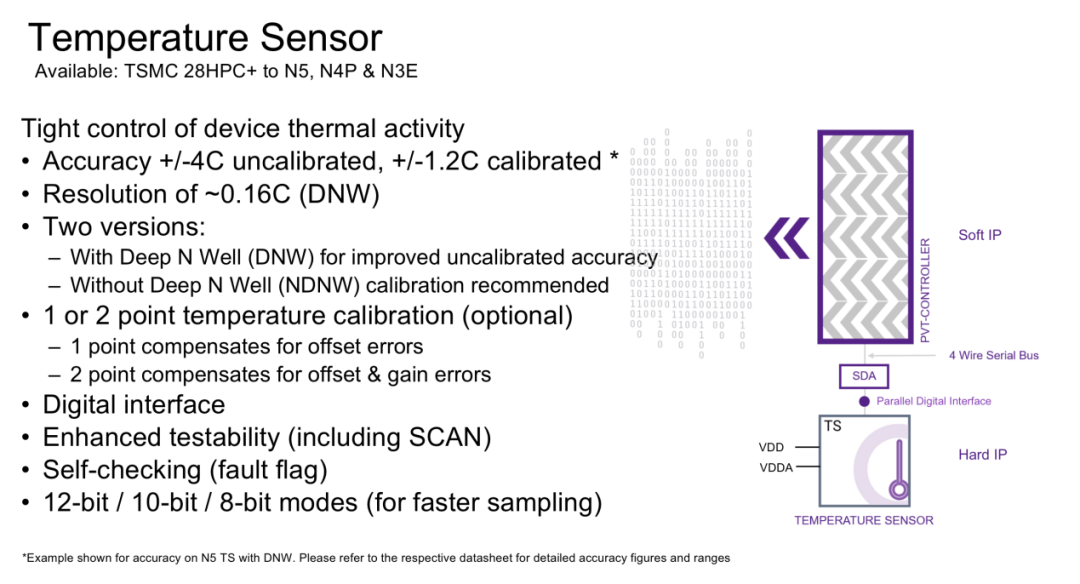

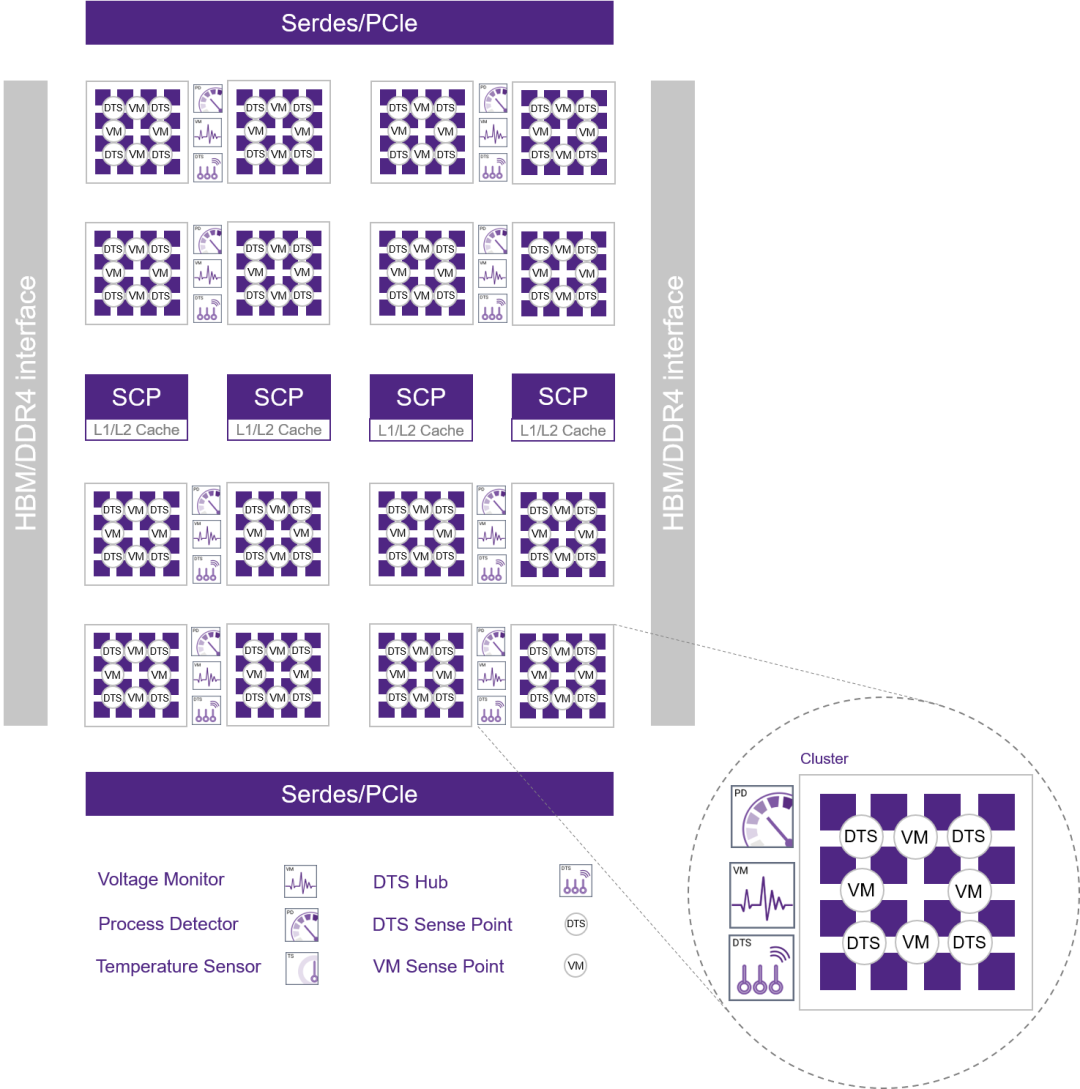

新思科技的片内PVT子系统解决方案由多个片内监控器组成,这些监控器可分别用于工艺检测、电压监控和温度传感,具体工作原理如下:

-

工艺检测器可帮助评估和监控die与die之间以及大芯片之间的速度。所收集的数据可帮助深入了解硅片老化情况,并用于电压/时序分析、动态电压和频率缩放优化以及速度分档。

-

电压监控器可测量多个域的电源电压和静态压降,以验证和优化器件的配电网络,特别是在承受任务模式工作负载压力时。

-

温度传感器可以检测芯片温度的变化,提醒设备的热管理系统启动冷却措施以防止过热。在不进行初始化校准情况下的精度为+/-4°C,进行初始化校准情况下的精度为+/-1.2°C,分辨率约为0.16°C(DNW)。温度传感器可实现对器件温度的变化进行严格控制。

嵌入式监控IP提供了对PVT参数的可见性,PVT监控将数据反馈到PVT控制器中,这些数据可通过标准(APB)接口来访问。PVT监控可以根据客户的不同应用场景进行不同的配置,并且可以轻松地集成到设计流程和芯片的架构中。

新思科技的SLM PVT监控IP可应用于多种用途,从实时热映射到能耗/功率优化和硅评估,涵盖从设计到上线、测试和现场操作的全过程。除此之外,新思科技正在不断推动PVT监控技术的创新和发展,以满足不断演进的先进制程芯片设计需求。例如,正在开发中的Droop Detector将用于与Droop相关的早期内核故障检测。

新思PVT监控IP核适用多个目标市场应用

新思科技的PVT监控IP核已被纳入台积公司库和IP质量管理计划(TSMC9000计划)中,并已被全球140多家客户采用,实现了600多个设计,广泛应用于人工智能(AI)、数据中心、高性能计算(HPC)、消费电子和5G等多种目标市场应用。

以AI芯片设计中的方法学为例。在AI芯片的设计过程中,由于大规模的工作负载,带来了重大散热、高功率分布和静态压降的难题,高功率不仅限制了性能,还增加了成本和二氧化碳排放量。通过使用新思科技的SLM PVT监控IP,可以显著提高该AI芯片的多核利用率,通过将监控放置在靠近热点的位置,更好地管理多个热点的不可预测性,优化每瓦的性能,保持关键逻辑运算的供电余量。

SLM PVT监控IP在AI芯片的应用案例

新思科技SLM PVT监控IP实际应用案例分享

最具代表性的案例之一是为世界上最大的芯片Cerebras WSE-2提供最佳PPA和优化。Cerebras在84个WSE-2晶粒上各分布了8个温度传感器和8个电压监控器(每个有16个电压感应点)。每个晶圆上共有10,752个电压检测点和672个温度传感器,从而实现了通过集群内感应和热节流实现细粒度热管理,精确感测待优化的电压裕度,并实时监测轮询情况,监控突发AI工作负载导致的静态压降,评估跨芯片的局部工艺变化,以实现电压扩展和性能优化。在从设计、测试、生产到现场运行的器件生命周期的各个阶段,硅健康状况的可视性。

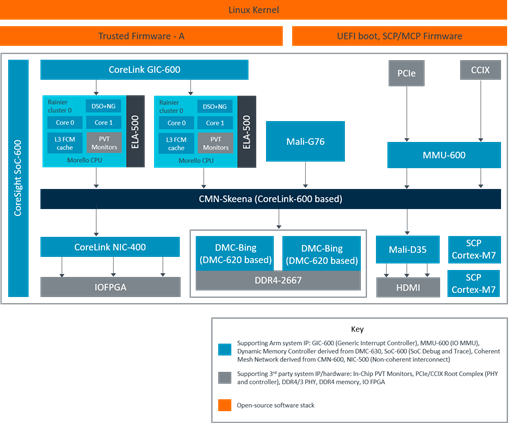

另一个案例是在Arm安全硬件架构SoC上的应用。Arm在Morello SoC中使用了3个温度传感器、4个电压监视器和1个工艺检测器。这样,应用软件可以利用这些温度传感器来测量CPU的温度,当温度超过可配置的警戒阈值时,软件会发出警告或进行关机操作,以保护设备的安全。

终端用户可以通过配置Arm的Cortex MCore软件中的温度级别来访问新思温度传感器,从而配置警报和关机阈值。ATE测试程序则可以使用新思工艺监视器来判断每个设备相对于整体群体的工艺偏差。

最后,PVT控制器来管理这些温度传感器、电压监视器和工艺检测器的子系统,这样的做法减轻了系统控制处理器的许多相关任务,确保监测和管理的高效性和准确性。

PVT监控在Arm Morello SoC中的应用

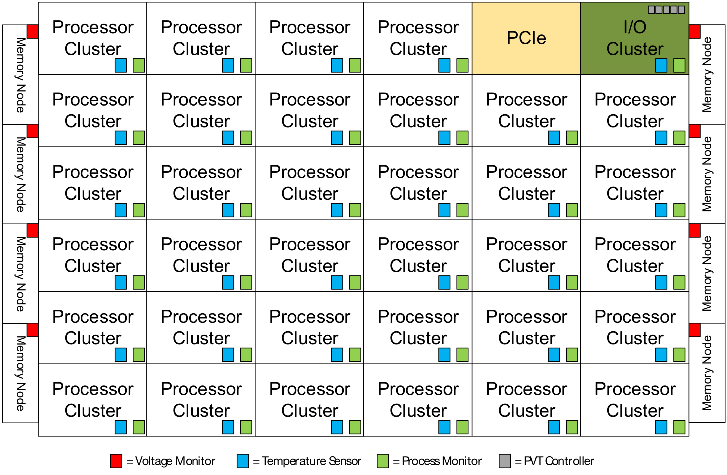

第三个案例是在Esperanto公司的推理处理器芯片中使用片内PVT监控器进行芯片健康评估。Esperanto在其推理芯片中分布了35个温度传感器和工艺检测器,每个处理器集群和I/O集群各一个,还嵌入了热敏二极管。每个存储器节点中嵌入了8个电压监控器(每个有16个电压感应点),以主动监控来自处理器集群的关键电源。采用5个PVT控制器来收集数据,并通过APB和JTAG接口,将数据嵌入CPU中。这些监控器在ATE(自动测试设备)运行操作期间被使用。

通过将工艺监视器变化与设备内测得的误码率和性能计数器相结合,可以报告设备的健康状况。

新思PVT监控在Esperanto公司的推理处理器芯片中的应用

结语

随着AI、5G、消费电子、高效能计算等应用领域对更小、更强大的电子设备的需求不断增长,先进制程芯片的演进还在继续。实现芯片内部可视性和洞察力是帮助优化半导体生命周期各个阶段、并最终提高芯片质量的关键工具。PVT监视器将成为实现先进制程芯片设计成功的关键!

在这一发展趋势下,新思科技的PVT监控子系统,再配以全方位的SLM技术解决方案,为先进制程芯片的成功提供了一种了解芯片的内部和外部情况的准确有效的方法,更好地帮助芯片开发者来应对先进制程芯片不断增加的设计和制造挑战。

我们将在9月14日召开的线上研讨会中揭示如何在IC设计中嵌入分布式PVT IP,通过实时收集参数和PVT controller分析,优化性能,提高可靠性。了解更多关于SLM PVT IP信息,请扫码报名线上研讨会:

-

新思科技

+关注

关注

5文章

798浏览量

50343

原文标题:新思科技PVT IP:从源头解决先进制程芯片“三大拦路虎”

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

三星芯片代工新掌门:先进与成熟制程并重

锐成芯微推出基于8nm工艺的PVT Sensor IP

苹果加速M5芯片研发,争夺AI PC市场,台积电先进制程订单激增

喆塔科技先进制程AI赋能中心&校企联合实验室落户苏州

新思科技发布全球领先的40G UCIe IP,助力多芯片系统设计全面提速

芯片微型化挑战极限,成熟制程被反推向热潮

新思科技PCIe 7.0验证IP(VIP)的特性

新思科技携手英特尔推出可量产Multi-Die芯片设计解决方案

新思科技面向英特尔代工推出可量产的多裸晶芯片设计参考流程,加速芯片创新

台积电回应先进制程涨价传闻:定价以策略为导向

台积电2023年报:先进制程与先进封装业务成绩

M31推出5纳米先进制程高速接口IP,满足AI与边缘运算需求

新思科技与英特尔深化合作加速先进芯片设计

新思科技与英特尔深化合作,以新思科技IP和经Intel 18A工艺认证的EDA流程加速先进芯片设计

芯片先进制程之争:2nm战况激烈,1.8/1.4nm苗头显露

新思科技PVT IP:从源头解决先进制程芯片“三大拦路虎”

新思科技PVT IP:从源头解决先进制程芯片“三大拦路虎”

评论