一、SerDes-PHY结构:

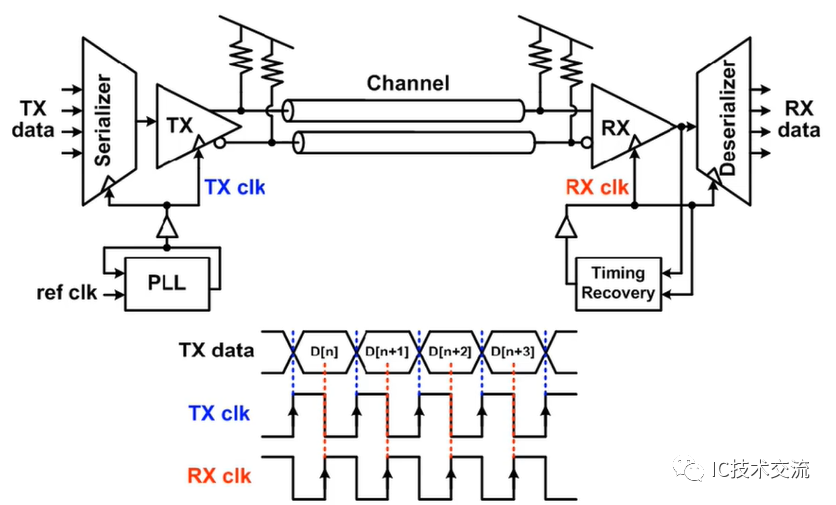

SerDes是串化(Serializer)和解串(Deserializer)的简称,下图给出了PHY的简图。发送端发送并行数据,时钟由ref_clk经过PLL锁相环振出的时钟提供,经过差分对信号传输至接收端,通过CDR恢复时钟并解串数据。

二、差分传输的优势

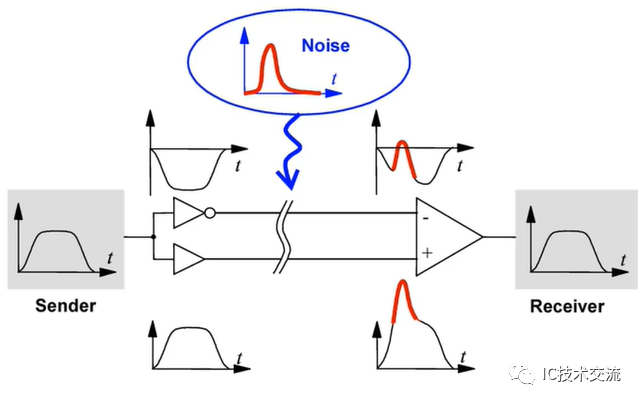

高速通信普遍采用差分信号传输,通过P/N信号间的电平差传输数据,差分对由于相位相反可以抵消相互间的串扰,同时抗干扰能力强,两者间的电平差可以抵消传输过程中的噪声影响。

发送频率过快,如数字信号的上升沿和下降沿,可能会产生大量EMI。单端和差分信号都会产生EMI,但差分对中的两个信号会产生大小相等但极性相反的电磁场。差分对导体之间紧密接触(如双绞线),确保差分信号发射在很大程度上相互抵消。

差分信号利用D+/D-间的差值发送数据,相比较单端信号,电压摆幅减半,同时提高信噪比,电压降低进一步减小了功耗和EMI效应。此外相比较单端信号通过地回流,差分对极性相反,无需通过地回流,这使得电源系统更加独立。

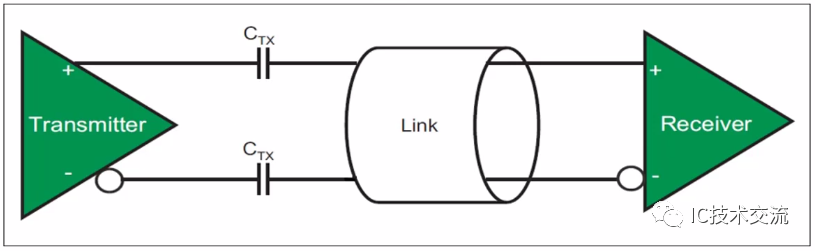

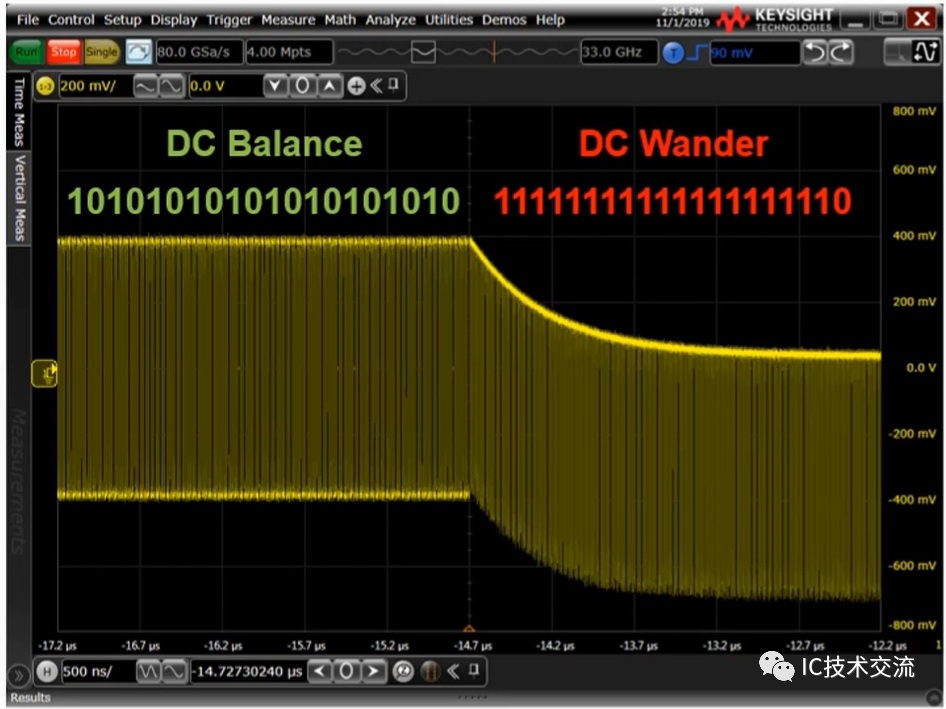

发送端和接收端通过电容进行耦合,因为不同板卡的共模电压不同,AC耦合可以使tx/rx都工作在自己的电压范围内。AC耦合带来的问题是,当发送端码流一直为0或1时会出现DC Wander的情况,电压幅值会走低,因此发送端应避免该情况出现(8b/10b编码原因)。

四、时钟数据恢复电路(CDR)

差分信号只发送数据,没有时钟,接收端通过CDR电路从码流中恢复时钟,本质上是个PLL锁相环电路,排除连续N个0或1的极端情况外,CDR可以一直保持锁定状态,这也是采用8b/10b(连续码流不能超过5个0或1)编码的原因。

五、8b/10b编码

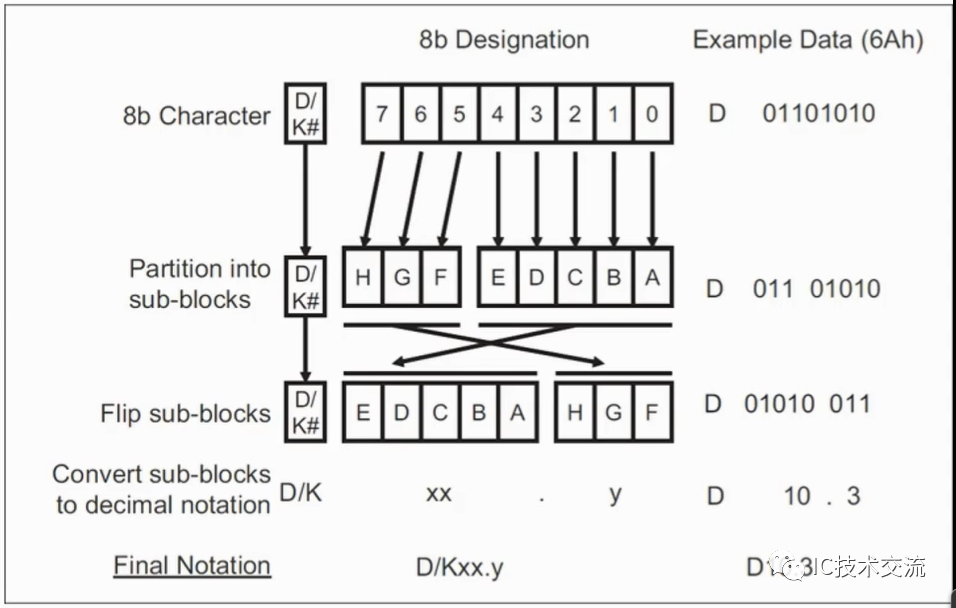

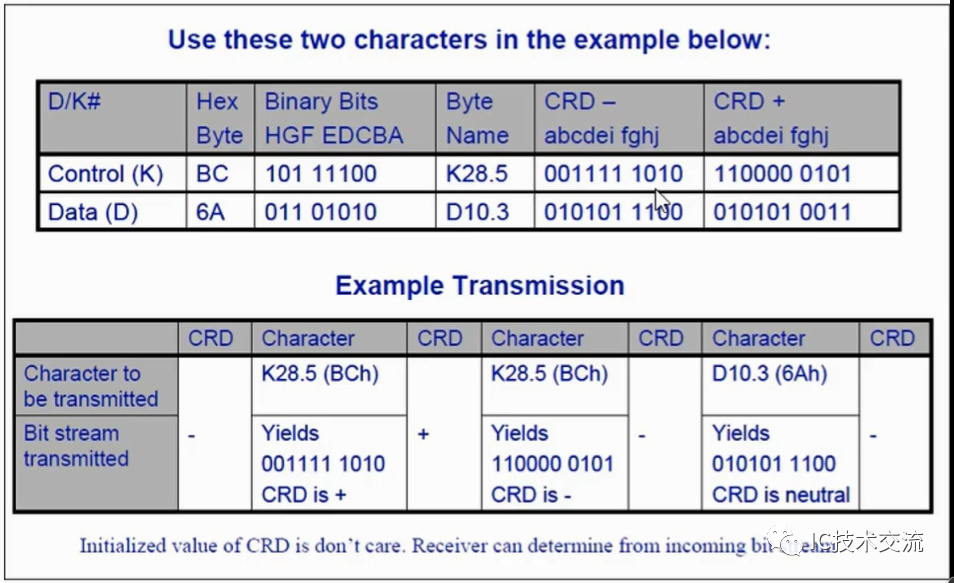

8b/10b编码顾名思义就是8bit数据编码为10bit数据。对于连续的码流,为了保证DC Balance,0和1的数量要尽可能一致,如果0的数量比1多,则极性为负(-),反之极性为正(+)。8bit数据共有256种情况,10bit数据共有1024种情况,每个8bit根据不同极性有2个10bit数据与之对应,然而如果0和1数量一致,则只对应1个10bit数据,总而言之,用不到512个10bit码型,这有利于纠错。K码是控制码字,D码是数据码字,8bit数据中3bit为一组,5bit为一组,然后编为4bit和6bit,Dxx.x表示数据,Kxx.x表示K码。

编码过程中,极性是时时刻刻改变的,本次码字极性为0则下次码字就要极性为1,以此循环往复以保持0/1数量一致。如果码字极性为中(0/1数量一致),则极性保持不变。

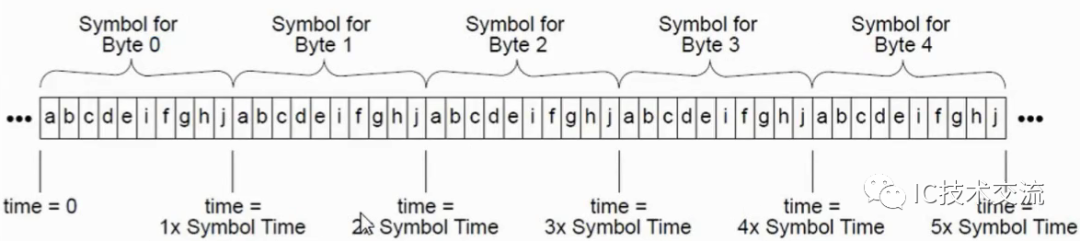

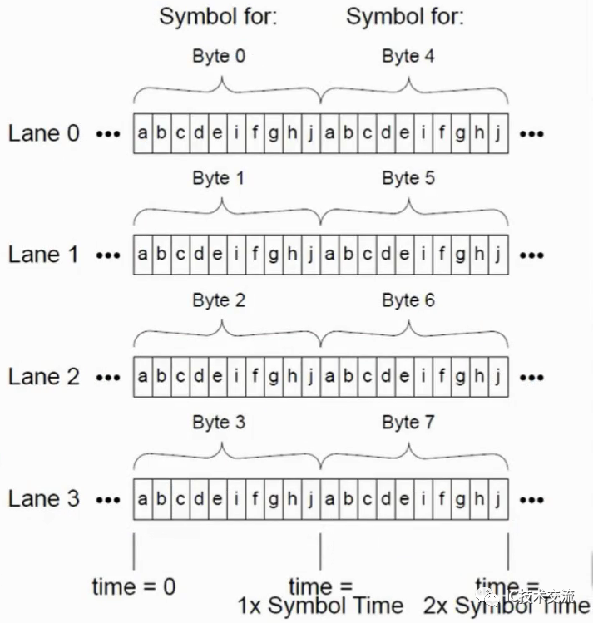

如果只有一条lane,则低字节(bit0)先发送,如果有四条lane,则数据并行发送

单lane发送的情况:

4条lane发送的情况:

8b/10b编码会报出两种类型的错误:

1、码字错误,即接收到的码字不在编码范围内;

2、极性错误,即接收码字极性没有按照正负交替出现;

六、扰码

8b/10b保证了0和1的平衡,为什么需要扰码呢?如果MAC层数据流发送相同的pattern呢?PCS中即使做了8b/10b发送数据依旧为周期短脉冲,这时信号能量集中在固定频点,EMI效应严重。为了避免这种情况就需要增加扰码。

扰码就是LFSR,伪随机噪声,LFSR位数越多,循环一次所需时间越长,这样就避免了周期短脉冲。LFSR与发送数据异或,在接收端再做一次异或恢复。

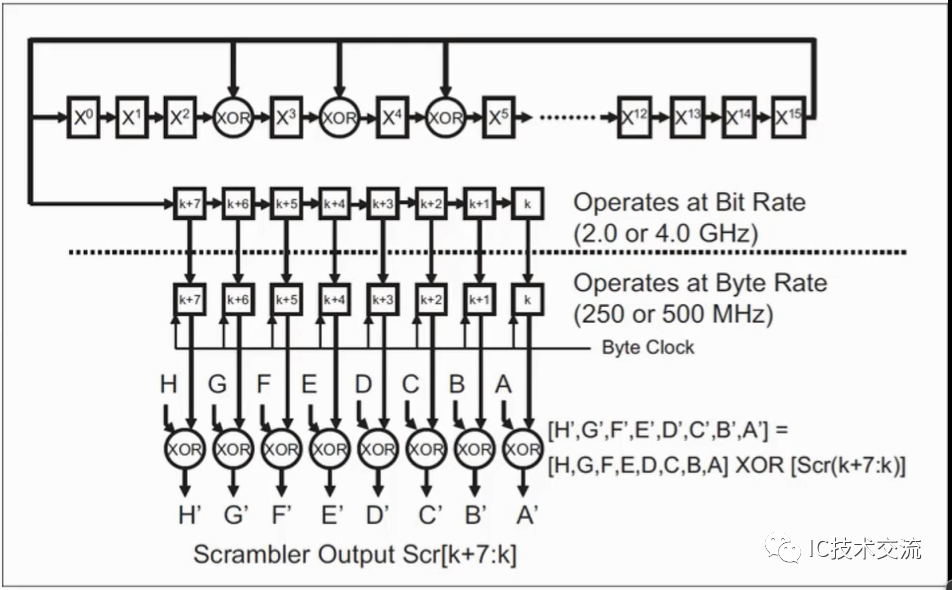

PCIE gen1/2(2.5G/5.0G)中使用16位LFSR:

G(X)=X16+X5+X4+X3+1

LFST的时钟速率是数据的8倍,即每循环8次与数据做一次异或:

七、参考时钟

PCIE要求发送端和接收端PHY的参考时钟100MHz偏差在±300ppm(gen1-4),±100ppm(gen5)。

PHY参考时钟有四种情况:

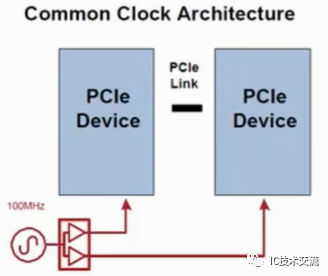

1、Common Clock:发送/接收端共用参考时钟

2、Data Clock:发送端有参考时钟,接收端完全用CDR恢复的时钟

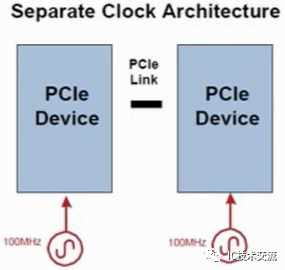

3、SRNS:发送/接收端有独立的参考时钟,不带SSC扩频

4、SRIS:发送/接收端有独立的参考时钟,带有SSC扩频

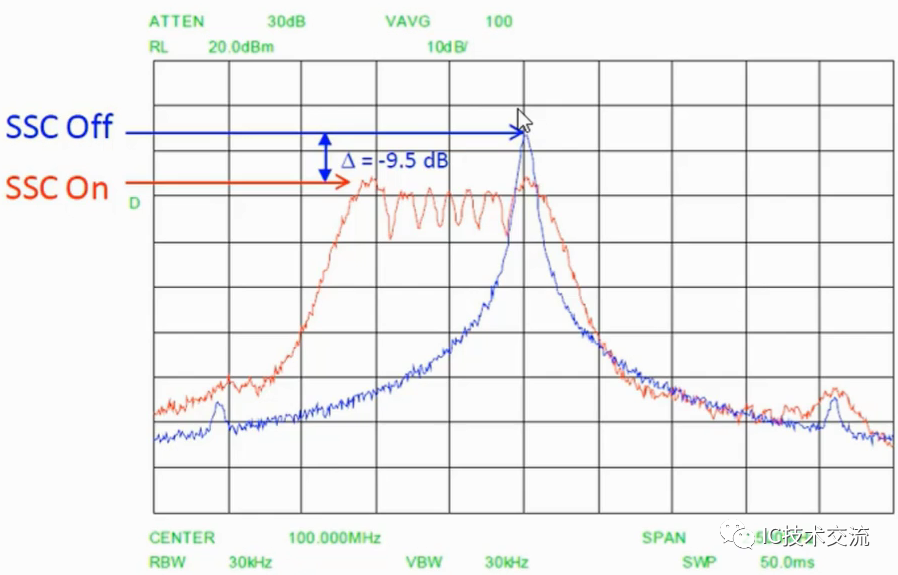

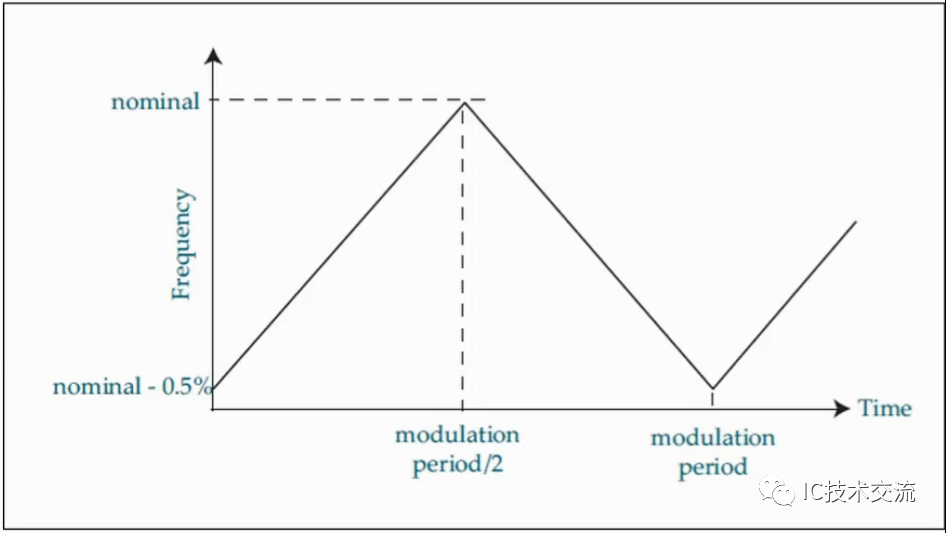

这里需要说下SSC扩频通信,理论上说,发送的0/1持续时间是一样的,扩频通信就是让每个bit的周期变得不一样,一会变长一会变短,这样时间频率上的周期改变使得整体信号的频域展宽,EMI效应更小。

PCIE支持参考时钟以30kHz-33kHz的变动频率加入0%到-0.5%的扩频,即100MHz降到99.5MHz再升到100MHz,这样的周期性变动为30kHz-33kHz。

八、时钟频偏容忍

在发送/接收端晶振都存在频偏的情况下,需要考虑频偏造成的影响,简言之就是发送端速率可能超过接收端的,这导致接收端处理不过来,为了解决频差,PCS中EB(弹性缓存)的功能就体现出来了,发送端每N个码字中插入SKIP码,接收端丢弃SKIP无用码字以纠频偏。频差越大,插入SKIP码的比例越高,有效带宽越低。

审核编辑:刘清

-

PHY

+关注

关注

2文章

308浏览量

51932 -

电磁场

+关注

关注

0文章

797浏览量

47452 -

EMI设计

+关注

关注

0文章

44浏览量

10525 -

PLL电路

+关注

关注

0文章

92浏览量

6495 -

SERDES接口

+关注

关注

0文章

28浏览量

3079

原文标题:协议类:SerDes-PHY

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

SerDes-PHY结构是由哪些部分组成的?差分传输的优势有哪些?

SerDes-PHY结构是由哪些部分组成的?差分传输的优势有哪些?

评论