串联电阻R与半导体ESD 电路布线中,哪个应放置靠近被保护IC?

在信号线防浪涌保护中,信号线时常会串一颗小阻值的电阻作为保护器件来抑制浪涌电流,起到限流的作用。但对于更大的电流和电压防护,还需搭配一颗TVS或ESD ,对后级芯片起到更高的防浪涌保护。

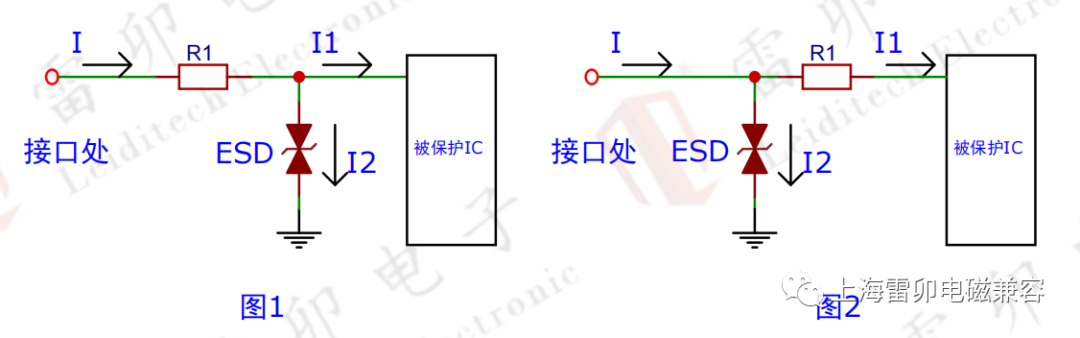

串联电阻R和ESD怎么放呢?是串联电阻靠近被保护芯片放,ESD靠近接口放;还是ESD靠近芯片放,串联电阻靠近接口放。上海雷卯工程师发现其实放置不同,防浪涌等级是不同的。

2.理论分析

在如图1所示的情况下, ESD动作时, I=I1+I2, I>I1, 在R1上会流过比ESD中更大的电流。虽然在这种情况下被保护电路在一定程度上得到保护,但电阻R1,却经不起大电流的考验而损坏,结果造成接口故障、系统故障。

在如图2所示的情况下, ESD动作保护有效时, ESD的阻抗很低, 大部分电流从ESD中流过,即I2, 而在R1中流过的电流I1远远小于I2,那就更小于I。虽然在这种情况下ESD要经受比如图1所示的情况更大的电流, 但是ESD与电阻相比更能经受得起大电流,因此芯片的防浪涌等级实际升高了。

实际试验中图1信号接口的抗浪涌电压能力比图2接口要差很多。上海雷卯电子工程师常发现图1接口失效是由于串联在接口电路上的电阻损坏造成的,而ESD没有损坏;图2接口失效是由于ESD被击穿短路造成的,电阻没有损坏。由此上海雷卯工程师得出结论:电阻靠近被芯片放置,而ESD靠近接口放置这种搭配时防护能力更强。

需要注意的是,在设计防浪涌保护电路时,应根据具体应用的需求来选择合适的串联电阻和TVS。阻值的选择通常在几十至几百欧姆之间,应考虑平衡信号质量和保护效果。TVS的额定电压应大于预期的过电压水平。

3.上海雷卯接口电路防护电路推荐

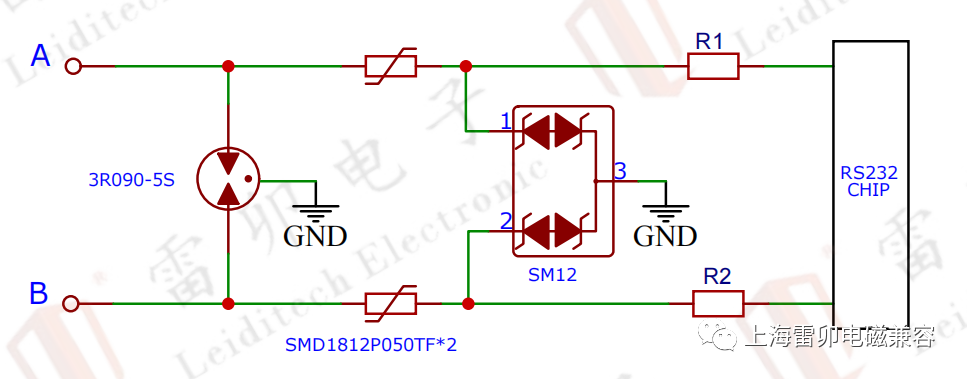

1)RS485接口浪涌防护电路

2)RS232接口浪涌防护电路

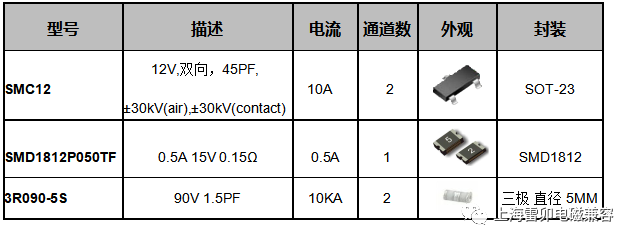

3)RS485接口浪涌防护元件列表

4)RS232接口浪涌防护元件列表

审核编辑:刘清

-

串联电阻

+关注

关注

1文章

191浏览量

14791 -

ESD

+关注

关注

49文章

2030浏览量

172953 -

TVS管

+关注

关注

1文章

279浏览量

20273 -

浪涌电压

+关注

关注

1文章

52浏览量

13870 -

RS485接口

+关注

关注

2文章

62浏览量

14140

原文标题:串联电阻R与半导体ESD电路布线与防浪涌关系

文章出处:【微信号:上海雷卯电磁兼容,微信公众号:上海雷卯电磁兼容】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

串联电阻R与半导体ESD电路布线中,哪个应放置靠近被保护IC?

串联电阻R与半导体ESD电路布线中,哪个应放置靠近被保护IC?

评论