采集时间

采集时间是从释放保持状态(由采样-保持输入电路执行)到采样电容电压稳定至新输入值的1 LSB范围之内所需要的时间。采集时间(Tacq)的公式如下:

混叠

根据采样定理,超过奈奎斯特频率的输入信号频率为“混叠”频率。也就是说,这些频率被“折叠”或复制到奈奎斯特频率附近的其它频谱位置。为防止混叠,必须对所有有害信号进行足够的衰减,使得ADC不对其进行数字化。欠采样时,混叠可作为一种有利条件。

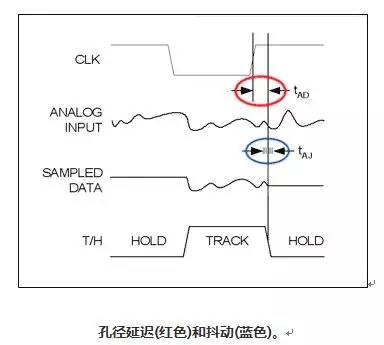

孔径延迟

ADC中的孔径延迟(tAD)是从时钟信号的采样沿(下图中为时钟信号的上升沿)到发生采样时之间的时间间隔。当ADC的跟踪-保持切换到保持状态时,进行采样。

孔径抖动

孔径抖动 (tAJ) 是指采样与采样之间孔径延迟的变化,如图所示。典型的ADC孔径抖动值远远小于孔径延迟值。

二进制编码(单极性)

准二进制是一种常用于单极性信号的编码方法。二进制码(零至满幅)的范围为从全0 (00...000)到全1的正向满幅值(11...111)。中间值由一个1 (MSB)后边跟全0 (10...000)表示。该编码类似于偏移二进制编码,后者支持正和负双极性传递函数。

双极性输入

术语“双极性”表示信号在某个基准电平上、下摆动。单端系统中,输入通常以模拟地为基准,所以双极性信号为在地电平上、下摆动的信号。差分系统中,信号不以地为基准,而是正输入以负输入为参考,双极性信号则指正输入信号能够高于和低于负输入信号。

共模抑制(CMRR)

共模抑制是指器件抑制两路输入的共模信号的能力。共模信号可以是交流或直流信号,或者两者的组合。共模抑制比(CMRR)是指差分信号增益与共模信号增益之比。CMRR通常以分贝(dB)为单位表示。

串扰(Crosstalk)

串扰表示每路模拟输入与其它模拟输入的隔离程度。对于具有多路输入通道的ADC,串扰指从一路模拟输入信号耦合到另一路模拟输入的信号总量,该值通常以分贝(dB)为单位表示;对于具有多路输出通道的DAC,串扰是指一路DAC输出更新时在另一路DAC输出端产生的噪声总量。

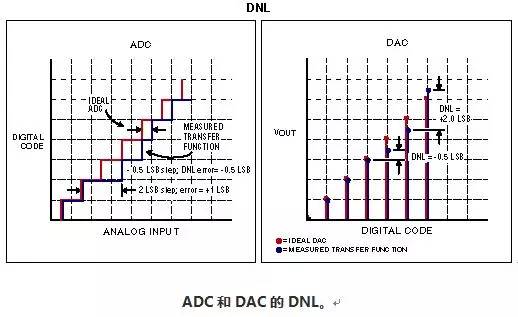

微分非线性(DNL)误差

对于ADC,触发任意两个连续输出编码的模拟输入电平之差应为1 LSB (DNL = 0),实际电平差相对于1 LSB的偏差被定义为DNL。对于DAC,DNL误差为连续DAC编码的理想与实测输出响应之差。理想DAC响应的模拟输出值应严格相差一个编码(LSB)(DNL = 0)。(DNL指标大于或等于1LSB保证单调性。)(见“单调”。)

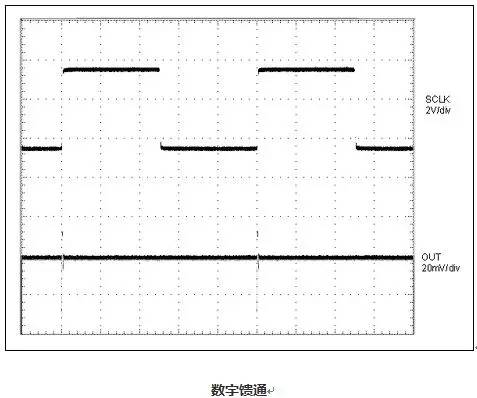

数字馈通

数字馈通是指DAC数字控制信号变化时,在DAC输出端产生的噪声。在下图中,DAC输出端的馈通是串行时钟信号噪声的结果。

动态范围

动态范围定义为器件本底噪声至其规定最大输出电平之间的范围,通常以dB表示。ADC的动态范围为ADC能够分辨的信号幅值范围;如果ADC的动态范围为60dB,则其可分辨的信号幅值为x至1000x。对于通信应用,信号强度变化范围非常大,动态范围非常重要。如果信号太大,则会造成ADC输入过量程;如果信号太小,则会被淹没在转换器的量化噪声中。

有效位数(ENOB)

ENOB表示一个ADC在特定输入频率和采样率下的动态性能。理想ADC的误差仅包含量化噪声。当输入频率升高时,总体噪声(尤其是失真分量)也增大,因此降低ENOB和SINAD(参见“信号与噪声+失真比(SINAD)”)。满幅、正弦输入波形的ENOB由下式计算。

加载-感应输出

一种测量技术,在电路的远端点加载电压(或电流),然后测量(检测)产生的电流(或电压)。例如,带有集成输出放大器的DAC有时就包含加载-感应输出。输出放大器可提供反相输入用于外部连接,反馈通路必须通过外部形成闭环。

全功率带宽(FPBW)

ADC工作时施加的模拟输入信号等于或接近转换器的规定满幅电压。然后将输入频率提高到某个频率,使数字转换结果的幅值降低3dB。该输入频率即为全功率带宽。

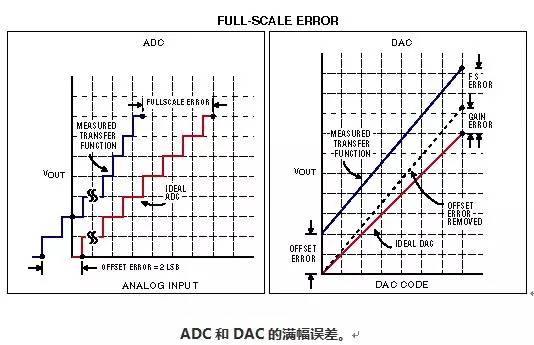

满幅(FS)误差

满幅误差为触发跳变至满幅编码的实际值与理想模拟满幅跳变值之差。满幅误差等于“失调误差+增益误差”,如下图所示。

FS增益误差(DAC)

数/模转换器(DAC)的满幅增益误差为实际与理想输出跨距之差。实际跨距为输入设置为全1时与输入设置为全0时的输出之差。所有数据转换器的满幅增益误差都与选择用于测量增益误差的基准有关。

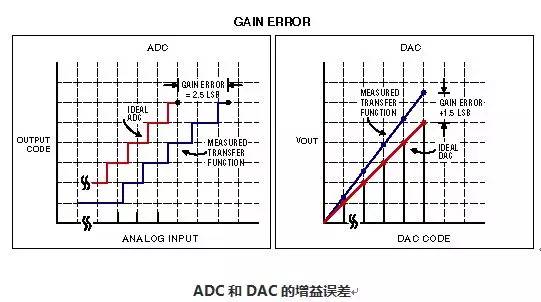

增益误差

ADC或DAC的增益误差表示实际传递函数的斜率与理想传递函数的斜率的匹配程度。增益误差通常表示为LSB或满幅范围的百分比(%FSR),可通过硬件或软件校准进行消除。增益误差等于满幅误差减去失调误差。

增益误差漂移

增益误差漂移指环境温度引起的增益误差变化,通常表示为ppm/°C。

增益一致性

增益一致性表示多通道ADC中所有通道增益的匹配程度。为计算增益的一致性,向所有通道施加相同的输入信号,然后记录最大的增益偏差,通常用dB表示。

尖峰脉冲

尖峰脉冲指MSB跳变时在DAC输出端产生的电压瞬态振荡,通常表示为nV?s,等于电压-时间曲线下方的面积。

谐波

周期信号的谐波为信号基频整数倍的正弦分量。

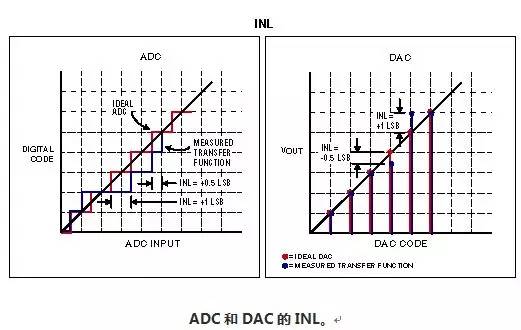

积分非线性(INL)误差

对于数据转换器,积分非线性(INL)是实际传递函数与传递函数直线的偏差。消除失调误差和增益误差后,该直线为最佳拟合直线或传递函数端点之间的直线。INL往往被称为“相对精度”。

互调失真(IMD)

IMD是指由于电路或器件的非线性产生的原始信号中并不存在的新频率分量的现象。IMD包括谐波失真和双音失真。测量时,将其作为将所选交调产物(即IM2至IM5)的总功率与两个输入信号(f1和f2)的总功率之比。2阶至5阶交调产物如下:

·2阶交调产物(IM2):f1 + f2、f2 - f1

·3阶交调产物(IM3):2 x f1 - f2、2 x f2 - f1、2 x f1 + f2、2 x f2 + f1

·4阶交调产物(IM4):3 x f1 - f2、3 x f2 - f1、3 x f1 + f2、3 x f2 + f1

·5阶交调产物(IM5):3 x f1 - 2 x f2、3 x f2 - 2 x f1、3 x f1 + 2 x f2、3 x f2 + 2 x f1

最低有效位(LSB)

在二进制数中,LSB为最低加权位。通常,LSB为最右侧的位。对于ADC或DAC,LSB的权重等于转换器的满幅电压范围除以2N,其中N为转换器的分辨率。对于12位ADC,如果满幅电压为2.5V,则1LSB = (2.5V/212) = 610μV

MSB跳变

MSB跳变(中间刻度点)时,MSB由低电平变为高电平,其它所有数据位则由高电平变为低电平;或者MSB由高电平变为低电平,而其它数据位由低电平变为高电平。例如,01111111变为10000000即为MSB跳变。MSB跳变往往产生最严重的开关噪声(见尖峰脉冲)。

单调

在序列中,如果对于每个n,Pn + 1总是大于或等于Pn,则说该序列单调增大;类似地,如果对于每个n,Pn + 1总是小于或等于Pn,则说该序列单调减小。对于DAC,如果模拟输出总是随DAC编码输入的增大而增大,则说该DAC是单调的;对于ADC,如果数字输出编码总是随模拟输入的增大而增大,则说该ADC是单调的。如果转换器的DNL误差不大于±1LSB,则能够保证单调。

最高有效位(MSB)

在二进制数中,MSB为最高加权位。通常,MSB为最左侧的位。

乘法DAC (MDAC)

乘法DAC允许将交流信号施加至基准输入。通过将感兴趣的信号连接至基准输入,并利用DAC编码缩放信号,DAC可用作数字衰减器。

无丢失编码

当斜线上升信号施加至ADC的模拟输入端时,如果ADC产生所有可能的数字编码,则该ADC无丢失编码。

奈奎斯特频率

奈奎斯特定理说明:ADC的采样率必须至少为信号最大带宽的两倍才能无失真地完整恢复模拟信号。该最大带宽被称为奈奎斯特频率。

偏移二进制编码

偏移二进制是一种常用于双极性信号的编码方法。在偏移二进制编码中,负向最大值(负向满幅值)用全0 (00...000)表示,正向最大值(正向满幅值)用全1 (11...111)表示。零幅由一个1 (MSB)后边跟全0 (10...000)表示。该方法与标准二进制类似,后者常用于单极性信号(参见二进制编码,单极性)。

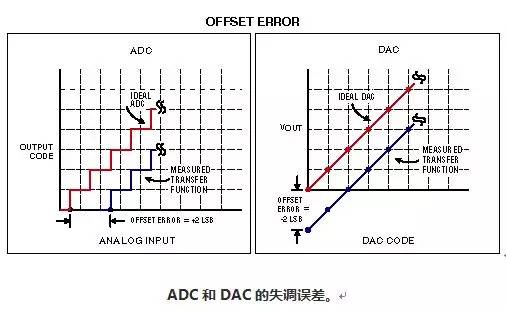

失调误差(双极性)

双极性转换器失调误差的测量与单极性转换器失调误差的测量类似,但在双极性传递函数的中间点测量零幅处的误差(参见失调误差单极性)

失调误差(单极性)

失调误差常称为“零幅”误差,指在某个工作点,实际传递函数与理想传递函数的差异。对于理想数据转换器,第一次跳变发生在零点以上0.5LSB处。对于ADC,向模拟输入端施加零幅电压并增加,直到发生第一次跳变;对于DAC,失调误差为输入编码为全0时的模拟输出。

失调误差漂移

失调误差漂移指环境温度引起的失调误差变化,通常表示为ppm/°C。

过采样

对于ADC,如果采样模拟输入的频率远远高于奈奎斯特频率,则称为过采样。过采样有效降低了噪底,所以提高ADC的动态范围。提高动态范围又进而提高了分辨率。过采样是Σ-Δ ADC的基础。

相位匹配

相位匹配表示施加至多通道ADC所有通道的完全相同信号的相位匹配程度。相位匹配指所有通道中的最大相位偏移,通常用度表示。

电源抑制比(PSRR)

电源抑制比(PSRR)指电源电压变化与满幅误差变化之比,以dB表示。

量化误差

对于ADC,量化误差定义为实际模拟输入与表示该值的数字编码之间的差异(参见“量化”)。

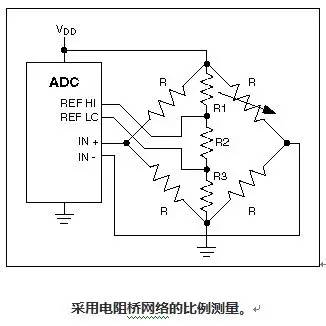

比例测量

施加至ADC电压基准输入的电压不是恒定电压,而是与施加至变送器(即负载单元或电桥)的信号成比例。这种类型的测量称为比例测量,它消除了基准电压变化引起的所有误差。下图中使用电阻桥的方法就是比例测量的一个例子。

分辨率

ADC分辨率为用于表示模拟输入信号的位数。为了更准确地复现模拟信号,就必须提高分辨率。使用较高分辨率的ADC也降低量化误差。对于DAC,分辨率与此类似:DAC的分辨率越高,增大编码时在模拟输出端产生的步进越小。

有效值(RMS)

交流波形的RMS值为有效直流值或该信号的等效直流信号。计算交流波形的RMS值时,先对交流波形进行平方以及时间平均,然后取其平方根。对于正弦波,RMS值为峰值的 2/2 (或0.707)倍,也就是峰-峰值的0.354倍。

采样率/频率

样率或采样频率以“采样/秒”(sps)表示,指ADC采集(采样)模拟输入的速率。对于每次转换执行一次采样的ADC(如SAR、Flash ADC或流水线型ADC),采样速率也指吞吐率。对于Σ-Δ ADC,采样率一般远远高于数据输出频率。

建立时间

对于DAC,建立时间是从更新(改变)其输出值的命令到输出达到最终值(在规定百分比之内)之间的时间间隔。建立时间受输出放大器的摆率和放大器振铃及信号过冲总量的影响。对于ADC,采样电容电压稳定至1 LSB所需的时间小于转换器的捕获时间至关重要。

信纳比(SINAD)

SINAD是正弦波(ADC的输入,或DAC恢复的输出)的RMS值与转换器噪声加失真(无正弦波)的RMS值之比。RMS噪声加失真包括奈奎斯特频率以下除基波和直流失调以外的所有频谱成分。SINAD通常表示为dB。

信噪比(SNR)

信噪比(SNR)是给定时间点有用信号幅度与噪声幅度之比,该值越大越好。对于由数字采样完美重构的波形,理论上的最大SNR为满幅模拟输入(RMS值)与RMS量化误差(剩余误差)之比。理想情况下,理论上的最小ADC噪声仅包含量化误差,并直接由ADC的分辨率(N位)确定:

(除量化噪声外,实际ADC也产生热噪声、基准噪声、时钟抖动等。)

带符号二进制编码

带符号二进制编码方法中,MSB表示二进制数的符号(正或负)。所以,-2的8位表示法为10000010,+2的表示法为00000010。

摆率

摆率是DAC输出变化的最大速率,或者不会造成ADC数字输出错误的输入变化的最大速率。对于带有输出放大器的DAC,规定摆率通常是放大器的摆率。

小信号带宽(SSBW)

为测量小信号带宽,向ADC施加一个幅值足够小的模拟输入信号,其摆率不会限制ADC的性能。然后,扫描输入频率,直到数字转换结果的幅值降低3dB。小信号带宽往往受限于相关采样-保持放大器的性能。

无杂散动态范围(SFDR)

无杂散动态范围(SFDR)是基波(信号成分最大值)RMS幅值与第二大杂散成份(不包含直流失调)的RMS值之比。SFDR以相对于载波的分贝(dBc)表示。

总谐波失真(THD)

THD测量信号的失真成分,用相对于基波的分贝(dB)表示。对于ADC,总谐波失真(THD)是所选输入信号谐波的RMS之和与基波之比。测量时,只有在奈奎斯特限值之内的谐波被包含在内。

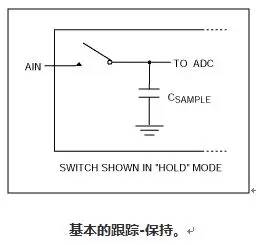

跟踪-保持

跟踪-保持往往也被称为“采样-保持”,指ADC的输入采样电路。跟踪-保持输入的最基本表示形式是模拟开关和电容(见图)。开关闭合时,电路处于“跟踪”模式;开关开路时,采样电容保持输入的最后瞬态值,电路处于“保持”模式。

转换噪声

转换噪声指引起ADC输出在相邻输出编码之间切换的输入电压变化范围。当增大模拟输入电压时,由于相关瞬态噪声的原因,触发每个编码发生跳变(编码边缘)的电压是不确定的。

二进制补码编码

二进制补码编码方法用于正数和负数编码,简化加法和减法计算。该编码方法中,-2的8位表示法为11111110,+2的表示法为00000010。

欠采样

欠采样技术中,ADC采样率低于模拟输入频率,该条件下将引起混叠。根据奈奎斯特定理,自然知道欠采样将丢失信号信息。然而,如果对输入信号进行正确滤波,以及正确选择模拟输入和采样频率,则可将包含信号信息的混叠成分从较高频率搬移至较低频率,然后进行转换。该方法有效地将ADC用作下变频器,将较高带宽信号搬移到ADC的有效带宽。要想该技术取得成功,ADC跟踪-保持电路的带宽必须能够处理预期的最高频率信号。

单极性

对于单端模拟输入ADC,单极性信号输入范围为零幅(通常为地)至满幅(通常为基准电压);对于差分输入ADC,信号输入范围为零幅至满幅,以正输入相当于负输入测量输入范围。

零幅误差

参见失调误差(单极性)。

免责声明:本文转自网络,版权归原作者所有,如涉及作品版权问题,请及时与我们联系,谢谢!

加入粉丝交流群

-

模拟技术

+关注

关注

17文章

469浏览量

39731 -

张飞电子

+关注

关注

54文章

175浏览量

12587

原文标题:(建议收藏)56个常用的ADC和DAC技术术语

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

采用什么方法可以消除ADC,DAC的偏置误差与增益误差?

想做一个采集设备,请问选用什么样的ADC和DAC合适?

如何设计ADC和DAC的基准源,以及基准源如何影响ADC与DAC那些性能?

适用于THS14xx和THS56xx DAC系列的THS14xx/5691 EVM

(建议收藏)56个常用的ADC和DAC技术术语

(建议收藏)56个常用的ADC和DAC技术术语

评论