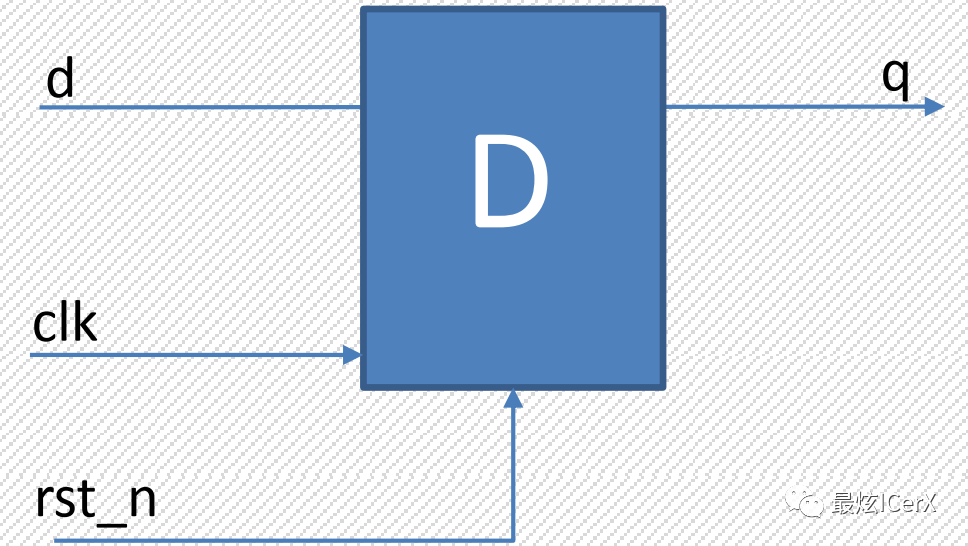

1、D触发器及代码

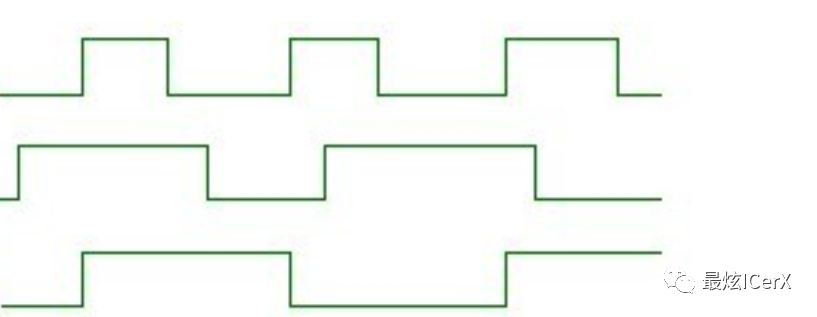

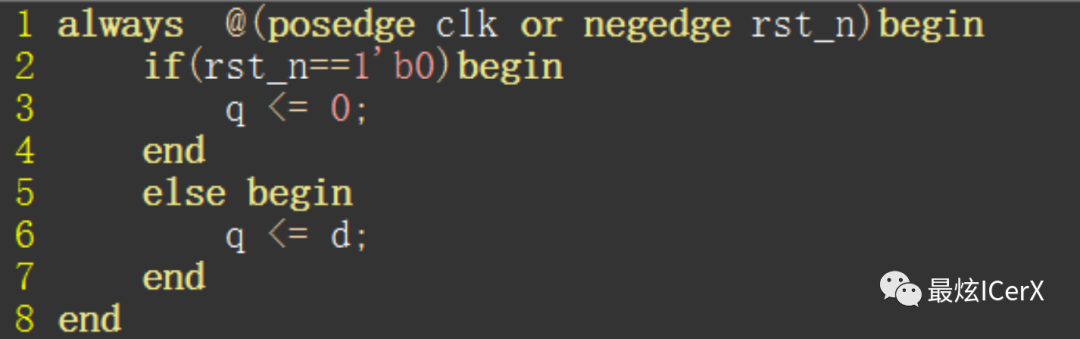

D触发器结构如下图所示,先有时钟上升沿,然后才有D的值赋给Q,没有上升沿Q值保持不变,时序逻辑在时钟上升沿/下降沿后才变化

2、硬件设计思维

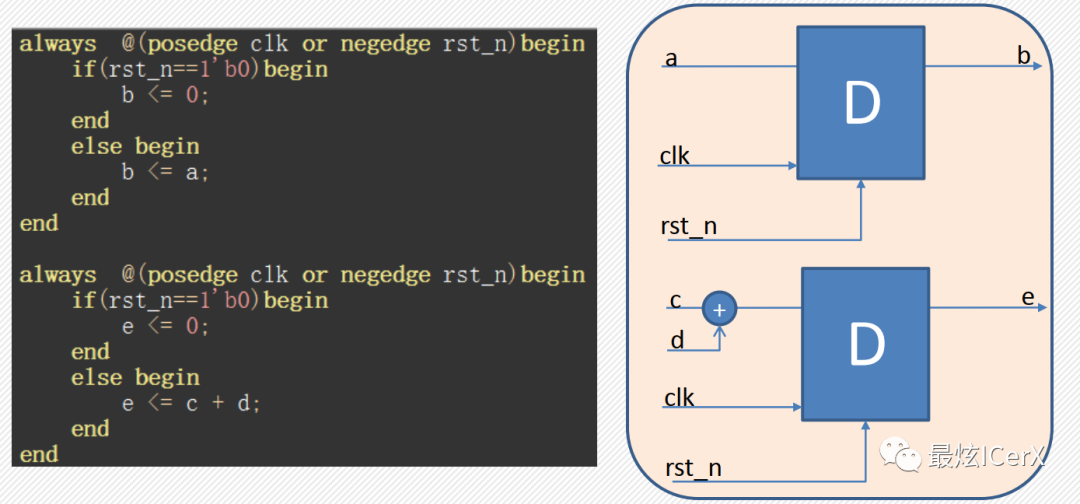

如下图所示,一个always对应一个D触发器,一个信号,always,模块就是一个元器件

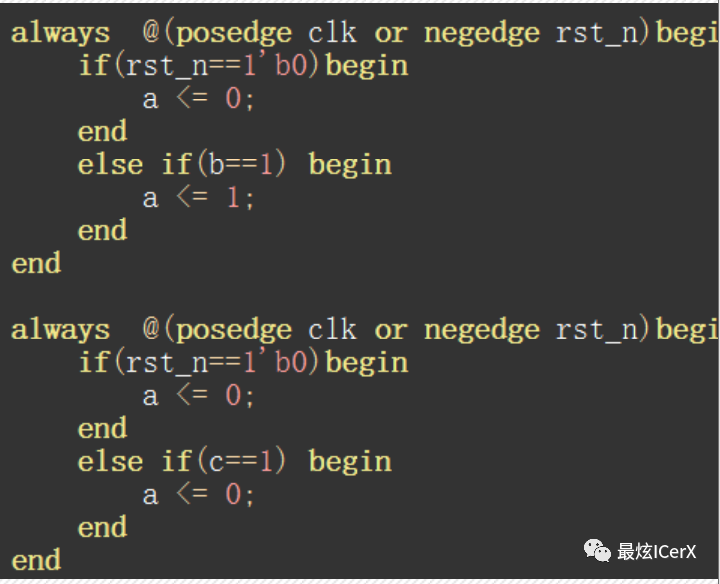

如下图所示,一个信号不能在多个always中设计,一个信号在一个always

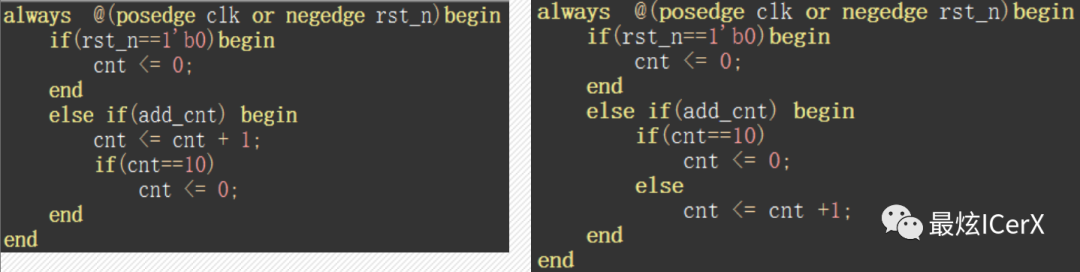

如下图对比,左边为软件思维描述过程,右边是硬件思维是描述功能,

硬件设计思路应逐个定义好每个信号/元器件的功能,然后连接,根据每个信号的功能画波形,来实现最终目标

3、一个RTL用例设计

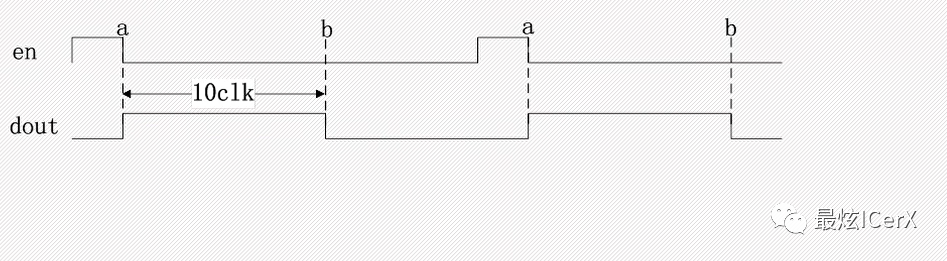

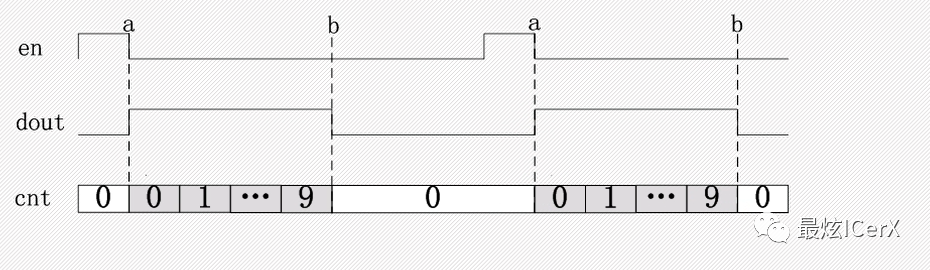

计数器用例,要求:当收到en后,dout产生一个宽度为10个时钟周期的高电平脉冲,信号示意如下,这是一个计数器用例,硬件设计步骤分解如下

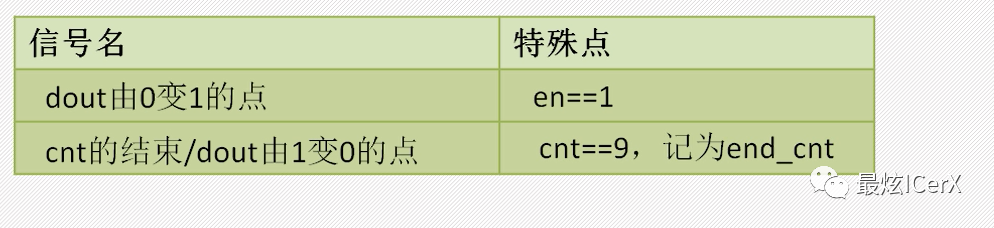

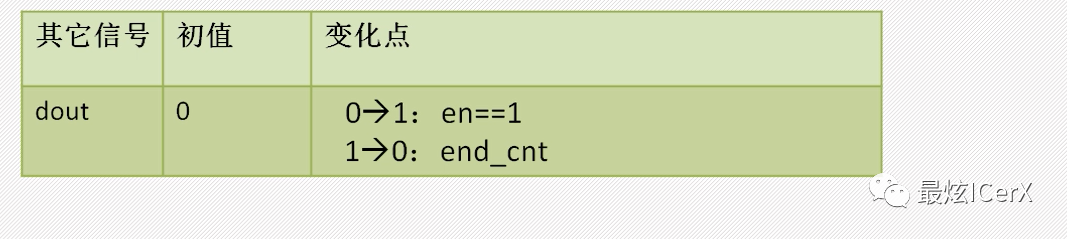

第一步明确功能,确定信号真值表。

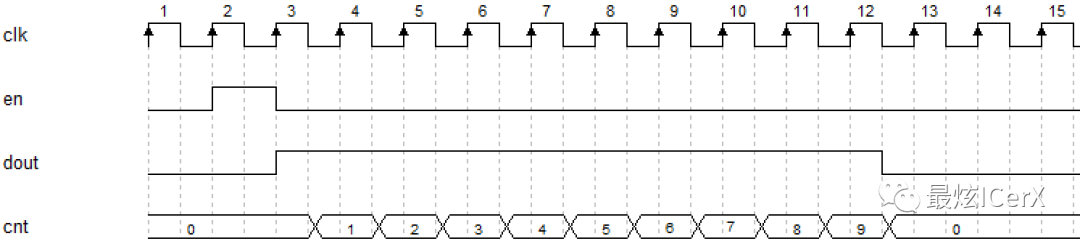

第二步画出功能波形,通过Timegen绘制如下信号波形,详细用法可阅读软件---TimeGen安装与使用,本用例所有信号都是在时钟上升沿过后进行判断的,下图en是在clk第三个上升沿时完成判断,记住先有时钟再有信号。

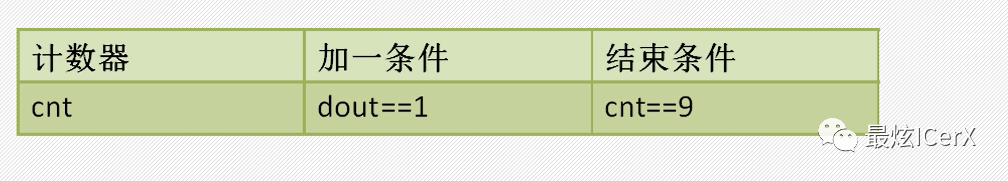

第三步明确计数器结构,本设计计数器默认都是从0开始计数

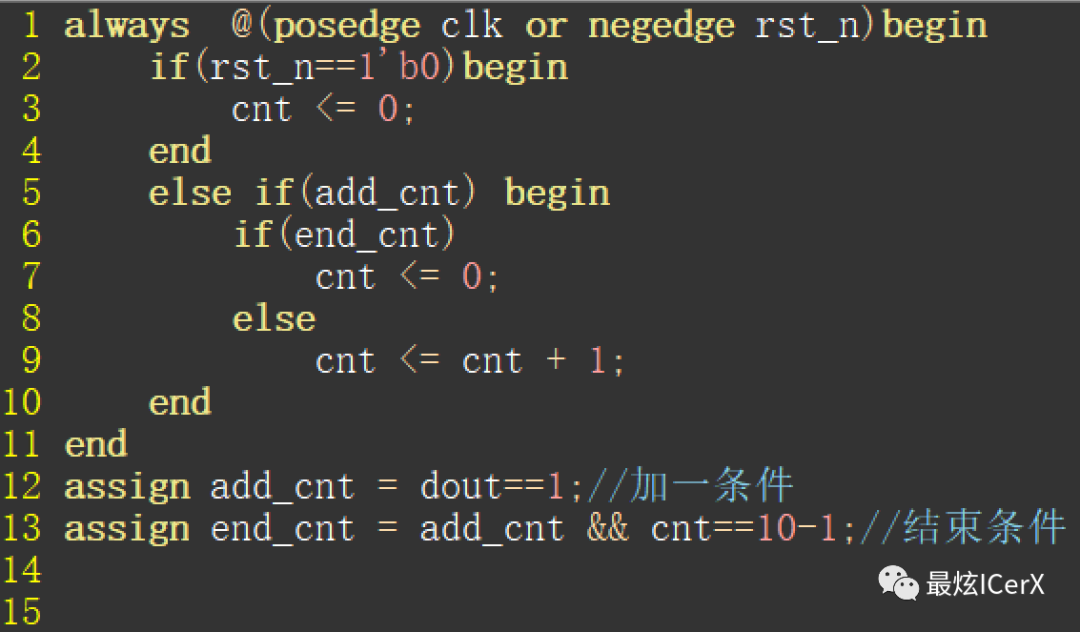

第四步明确计数器结构,确定设计中的加一及结束条件,代码如下,下面代码可作为计数器代码通用模板

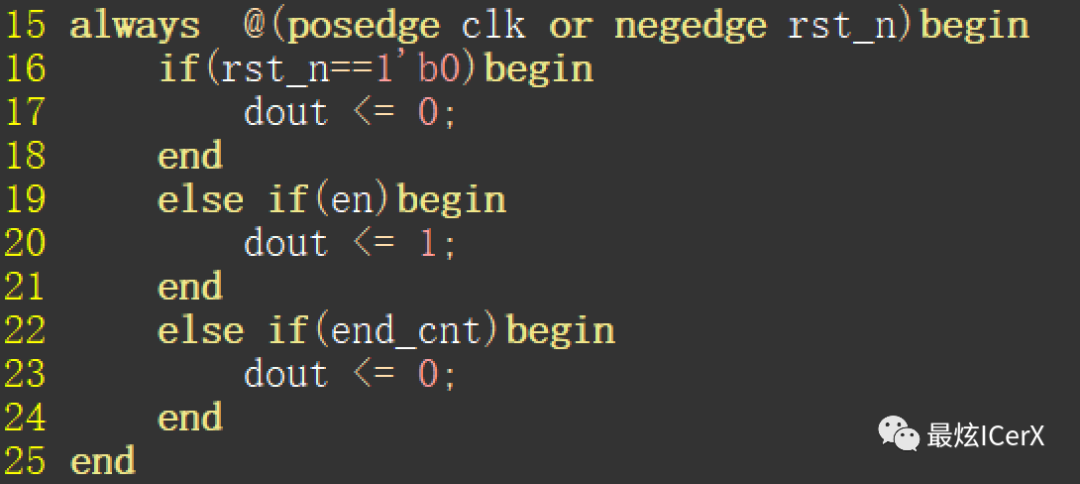

第五步定义特殊点,编写输出信号变化情况,如下代码

第六步完整性检查

第七步编写计数器代码,见上述计数器代码

第八步功能代码,见上述输出信号dout代码,补全其它代码

总结设计,规范硬件设计思路,第一步-->第二步......,按照步骤实现,检查设计过程。本设计中首先画出信号波形,接着确定计数器结构,接着确定计数器加一与结束条件,接着确定输出信号变低,变高时间点及条件,最后写计数器代码,输出信号代码,接口定义。接下来会继续介绍Verilog设计规范及对应用例。

审核编辑:刘清

-

计数器

+关注

关注

32文章

2255浏览量

94469 -

RTL

+关注

关注

1文章

385浏览量

59752 -

D触发器

+关注

关注

3文章

164浏览量

47896 -

时序逻辑电路

+关注

关注

2文章

94浏览量

16537 -

Verilog语言

+关注

关注

0文章

113浏览量

8224

原文标题:RTL设计规范

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在SpinalHDL的设计中集成现有RTL设计(IP)的渠道——BlackBox

RTL8139C RTL8139C-LF RTL8139CL RTL8139CL-LF

RTL设计规范有哪些?一个RTL用例设计介绍

RTL设计规范有哪些?一个RTL用例设计介绍

评论