在UVM寄存器模型的操作中,寄存器用于设置DUT状态和芯片状态信息的上报,有前门和后门读写两种方式。

推而广之,其他的DUT内部信号,由于验证的需要,有时也需要进行后门读写。这些信号除了包含前门可读的寄存器以外,还会包含reg/wire信号、状态机的状态值、memory内容等。

总的来看,获取DUT内部状态分为前门和后门两种方式。

前门读写

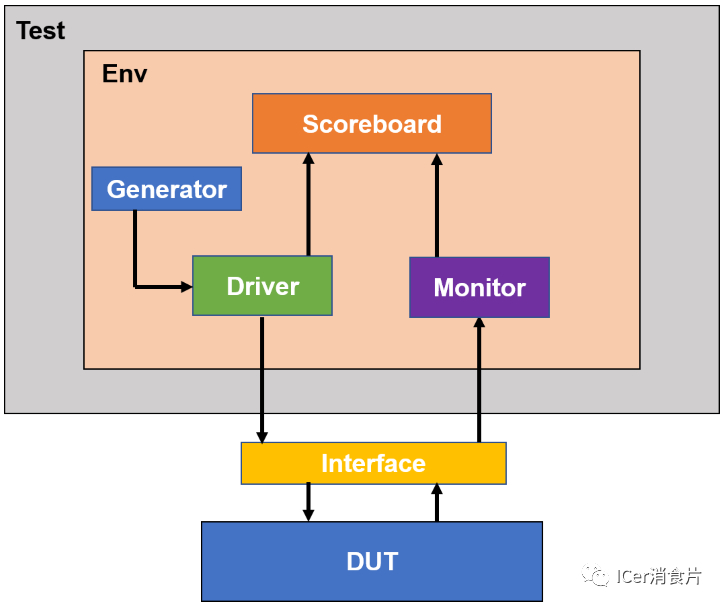

前门读写:使用总线对DUT发起真实的读写,一般需要总线VIP支持,仅针对DUT内部可访问的地址空间,如配置和上报寄存器、memory。

这种方式好处在于能够和芯片真实的工作场景保持高度相似,能够发现时序配合上的一些问题。

缺点一方面也是前门的“真实性”,当需要读写的地址空间数量很大时,会消耗非常多的仿真时间,影响用例的执行效率。

另一方面是这种耗时的读写不满足“实时性”比对的验证要求。某些验证环境中,可能需要在几个cycle内完成对DUT状态的获取和比对,这种场景下前门读取方式则无法满足。

后门读写

后门读写:绕过前门总线,直接通过DUT内信号的hierarchy路径强制force或者读取信号值。

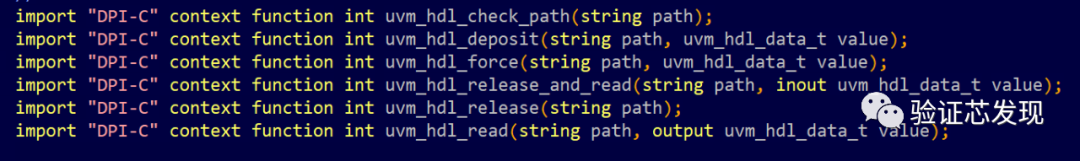

后门操作的方式可以分为:按信号的Hierarchy读取、interface连接DUT信号、和VPI访问。

1. 信号的Hierarchy读取

DUT经过编译后,内部的信号都有对应的hierarchy路径,如dut.a.b.c,dut.out。在验证环境中可以直接使用,例如:

bit A; A=dut.sub_block.A; if(A==0) begin ..... end

bitA; bit[15:0] B if(uvm_hdl_read("dut.sub_block.A",A))begin ..... end //bit[31:0] Y uvm_hdl_read("dut.X.Y[15:0]",B)//错误!使用VPI访问缺点:不能按位域驱动和读取。对于多bit信号,无法只对其中的部分bit操作。

一般而言对于黑盒验证中的加密代码,使用Hierarchy和VPI方式都是无法获取加密代码内部信号的状态。当然如果在已知加密代码层次前提下,通过一些处理,还是可以通过Hierarchy方式进行后门操作。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50844浏览量

423846 -

寄存器

+关注

关注

31文章

5343浏览量

120416 -

仿真

+关注

关注

50文章

4086浏览量

133640 -

信号

+关注

关注

11文章

2791浏览量

76789 -

DUT

+关注

关注

0文章

189浏览量

12391

原文标题:验证环境获取DUT内部信号的方法

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

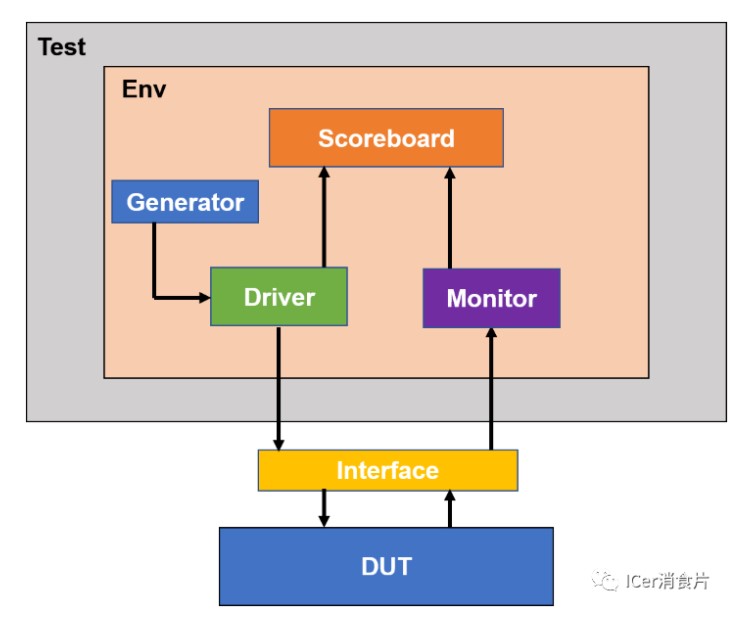

基于VMM验证方法学的MCU验证环境

基于VMM的验证环境的验证MCU指令实现设计

基于VMM验证方法学的MCU验证环境实现方法介绍

SoC验证环境搭建方法的研究

DUT 和 testbench 连接教程

验证组件配置参数

基于DUT内部寄存器值的镜像

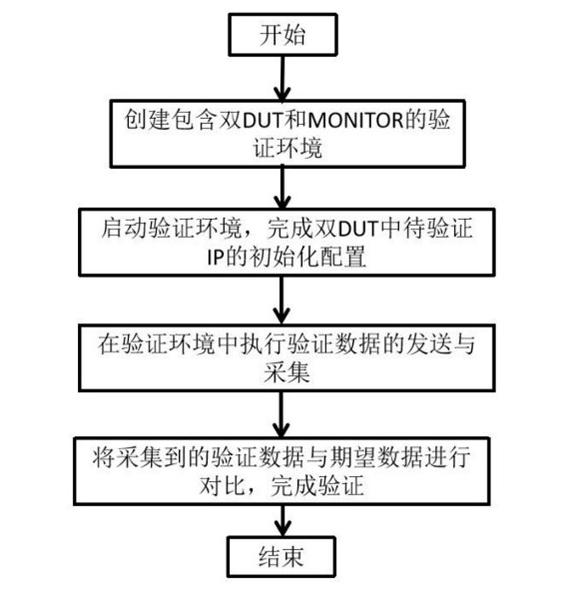

北京清微智能科技有限公司发布IC验证新方法,实现双DUT验证

验证环境获取DUT内部信号的方法

验证环境获取DUT内部信号的方法

评论