在进行数字电路后仿真时,经常会遇到很多时序为例,通常这些违例都是由网表中大量的时序检查报出的。这些常见的时序检查系统任务如下表所示:

| 时序检查系统任务 | 说明 |

|

$setuphold |

检查建立时间和保持时间,当setup违例时,出现此信息 |

|

$setuphold |

检查建立时间和保持时间,当hold违例时,出现此信息 |

| $setup | 检查建立时间 |

| $hold | 检查保持时间 |

| $recovery | 检查恢复时间(以复位信号为例,可以理解为rst必须在时钟沿之前的有效的最小时间),一般用于复位、置位等 |

| $removal | 检查撤销时间(以复位信号为例,可以理解为rst必须在时钟沿之后的有效的最小时间),一般用于复位、置位等 |

| $recrem | 检查恢复和撤销时间,一般常用于复位、置位等 |

| $period | 检查周期信号的最小周期,一般常用于时钟 |

| $skew | 检查两个信号之间的最大时间差 |

| $width | 检查脉冲的最小宽度 |

因为在仿真的过程中,有些报出的违例我们是不关心的,这些信息的大量出现可能会淹没我们真正需要观测的信息,为此需要在仿真时讲这些冗余的信息屏蔽掉。针对大家经常使用的NCSIM、VCS和ModelSim(QuestaSim),下文将说明如何在这两种EDA工具中屏蔽冗余的违例信息。

1 NCSIM

屏蔽使用的命令格式:

% irun-tfile myfile.tfile[other_options] source_files

上述命令中myfile.tfile中包含屏蔽信息,其中主要内容如下表:

| 参数 | 说明 |

|

-iopath +iopath |

不使能路径延迟 使能路径延迟 |

|

-prim +prim |

不使能指定的instance中原语的延迟 使能指定的instance中原语的延迟 |

|

-port +port |

删除指定的instance的port延迟 使能指定的instance的port延迟 |

|

[SystemTimingTask] -tcheck [SystemTimingTask] +tcheck |

屏蔽掉不关心的违例 |

【示例】*.tfile中内容格式

PATH top.foo -tcheck // 屏蔽所有关于foo的时序检查

PATH top.foo$setup $hold-tcheck // 屏蔽所有关于foo的setup和hold时序检查

PATH :SOC.lcsoc.syn_reg$setup-tcheck // 屏蔽:SOC.lcsoc.syn_reg的setup检查

注意:如果要屏蔽其他检查,只需将示例中的$setup或者$hold换成SystemTimingTask中的任何一个即可。

2 VCS

命令格式如下:

tcheck

tcheck

上述命令使用时需要注意以下几点:

1>在simv的option中,即 % ./simv -ucli run.tcl,其中run.tcl中增加需要屏蔽的信号,将tcheck中的内容增加的run.tcl中;

2>该命令仅对Verilog/SystemVerilog使用;

3>该命令使用时,待检测的源代码必须包括时序检查系统任务,否则将会产生warning信息;

上述命令格式中使用的相关参数的说明如下表所示。

| 参数 | 说明 |

| instance | port | 要被屏蔽的时序检查的实例或者端口的全路径名称 |

| tcheck_type | 指定需要进行屏蔽的时序检查类型:HOLD|SETUP|SETUPHOLD|WIDTH|RECOVERY|REMOVAL|RECREM|PERIOD|SKEW|ALL |

| -disable | -enable | 使能或不使能相关时序检查,如果要求屏蔽其中SETUP,则在tcheck_type指定SETUP后,需要在tcheck中使用-disable |

| -msg | -xgen |

A.指定的实例或者端口违例信息是否被显示 B.指定的实例或者端口notifier信息是否被显示 |

| -r | 指定是否递归式的对所有指定的instance及其以下层次所有的instance进行时序检查 |

【示例】(可以通过-ucli do.tcl直接添加到simv中)

tcheck {top_tb.C40010001} WIDTH -msg -disable

#对top_tb.C40010001不进行WIDTH时序检查,即屏蔽掉top_tb.C40010001的WIDTH检查

tcheck {top_tb.C40010001} -query

#显示对top_tb.C40010001的时序检查信息

3 ModelSim(QuestaSim)

命令格式如下:

tcheck_set[-quiet]

上述命令格式中使用的相关参数的说明如下表所示。

| 参数 | 说明 |

|

|

实例(模块或者线网)的全路径名称,该项是必须的 |

| -m | -n |

指定屏蔽操作的对象是模块还是线网,该项可选。 -m:此时命令中指定的instance是module(Verilog)或者entity(VHDL),此时的屏蔽操作将作用于指定的模块的所有实例 -n:此时命令中指定的instance指向一个线网,tcheck_set将应用于所有连接该线网的实例 |

| -quiet |

用于指定配置信息不显示于Transcript窗口,该参数的指定必须先于 |

| -r [-v] | 指定是否递归式的对所有指定的instance及其以下层次所有的instance进行时序检查,默认情况下,递归过程中被改变的instance的信息不会输出到Transcript,可以用-v将这些信息输出至Transcript中,该项可选 |

| tcheck_type | 指定需要进行屏蔽的时序检查类型:HOLD|SETUP|SETUPHOLD|WIDTH|RECOVERY|REMOVAL|RECREM|PERIOD|SKEW|ALL |

|

|

使能或者禁止是否将指定的时序检查违例信息和不定态产生的信息报出,该项可设置的值为“ON”和“OFF”,该项可选 |

|

|

控制指定时序检查的违例信息和不定态信息,其中 |

【示例】

tcheck_set top_tb.u1.u2 “(WIDTH (negedge clk))”OFF

#示例中,top_tb.u1.u2下的(WIDTH (negedge clk))检查产生的所有信息都将被屏蔽掉。如果对于示例中时序检查表达式的写法不了解,可以使用“tcheck_statustop_tb.u1.u2”来查看top_tb.u1.u2下所有的时序检查表达式,具体应用如下所示:

% tcheck_status top_tb.u1.u2

% #0 (WIDTH (negedge clk)) MsgOn XOn

% #1 (WIDTH (posedge clk)) MsgOn XOn

% #2 (SETUP (negedge d)(posedge clk)) MsgOn XOFF

% #3 (HOLD (posedge clk)(negedge d)) MsgOn XOFF

最后在使用上述EDA工具时,因为不同的工具提供的路径不同,在具体使用时,一定要使用对应的工具获得该工具可识别的路径信息。

审核编辑:汤梓红

-

仿真

+关注

关注

50文章

4099浏览量

133712 -

eda

+关注

关注

71文章

2767浏览量

173421 -

数字电路

+关注

关注

193文章

1608浏览量

80682 -

时序

+关注

关注

5文章

389浏览量

37355 -

VCS

+关注

关注

0文章

80浏览量

9625

原文标题:NCSIM、VCS和QuestaSim(ModelSim)后仿真如何屏蔽违例!

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

检测内存泄漏和内存违例,Valgrind不可少!

robei EDA简介Robei可视化EDA工具

NCSIM、VCS和QuestaSim后仿真如何屏蔽冗余的违例信息呢?

EDA工具手册

多种EDA工具的FPGA协同设计

IC设计中Accellera先进库格式语言与EDA工具的结合

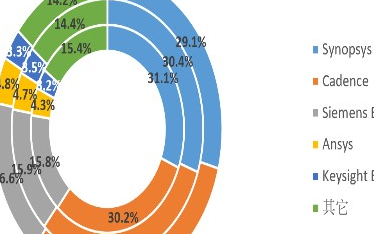

什么是EDA工具?目前全球EDA行业的现状是什么?

EDA的设计仿真工具——EasyEDA

Vivado时序案例分析之解脉冲宽度违例

视频中光流去除冗余信息的动作预测方法

EDA工具的发展特征

如何在EDA工具中屏蔽冗余的违例信息

如何在EDA工具中屏蔽冗余的违例信息

评论