铟化合物(Indium compounds )在3D存储器计算和射频集成方面显示出巨大的潜力,但还需要更多的研究。

研究人员继续在3D设备集成方面取得进展,特别是与铟锡氧化物(ITO)有关,这种物质在显示制造中得到了广泛的应用。近期的研究表明,掺杂锡、镓或锌组合的不同的铟氧化物化合物可能会提高晶体管的特性,如高载流子迁移率和稳定的阈值电压。但氧化物空位控制仍然是可靠的设备集成、BEOL金属化和CMP工艺的关键。

3D在FEOL、BEOL和封装中

单片3D集成描述了在单块硅片上“就地”建造两层或更多设备层的过程。这种3D的使用与3D封装概念形成对比,3D封装概念是在一个封装中组合几个完成的芯片,使用设备层分别制造然后再组合的层转移技术。不同的方法都归于“单片”之下,具体取决于特定设备的需求。单片集成也不排除在转移层下使用不同的基板。

例如,CFETs首先在FEOL中堆叠基于硅或SiGe的PMOS和NMOS设备层,然后进行任何互连金属化。层转移通常用于组合CFETs中的不同层。CFETs减少了一对互补晶体管的占地面积,增加了整体晶体管密度。

但是,3D集成还可以用来缩小电路相关部分之间的距离,减少互连路径的电阻,并提高整体速度。例如,常被提议作为解决内存带宽瓶颈问题的方案的存储器计算模块,可能被直接放置在主CPU逻辑之上。射频设备本身并不需要积极的缩放,但可以从3D集成提供的较短的电路路径中受益。

在这些存储器计算和射频集成应用中,这些设备是BEOL流程的一部分,因此面临严格的热限制。为了防止铜扩散,处理温度不能超过400°C。研究人员提议使用碳纳米管和2D半导体,但这些技术仍然相对不成熟。

然而,铟氧化物半导体相对成熟,今天在显示应用中得到了广泛的使用。这些铟氧化物半导体可能包括锡(Sn)、镓和/或锌掺杂物。这些层通常通过溅射(物理气相沉积)沉积,因为这个过程容易达到所需的低处理温度。

将ITO从显示器移至芯片

铟锡氧化物(ITO)可能是最成熟的基于铟的半导体,拥有几十年的显示行业制造历史。在最近的VLSI技术研讨会上,Yuye Kang及其在新加坡国立大学的同事调查了设备性能指标与通道厚度之间的关系。他们将ITO溅射到准备好的带有钨背门和氟化铪栅极介质的基板上。使用3.5 nm的ITO通道和提高的ITO源和漏电极,他们似乎稳定了有效载流子迁移率为72cm²/V-sec。

尽管按照硅标准,该载流子迁移率较低,但 72cm²/V-sec 明显优于之前报告的ITO器件的值。进一步将沟道厚度减小至2nm改善了亚阈值摆幅和阈值电压,但器件迁移率恶化。

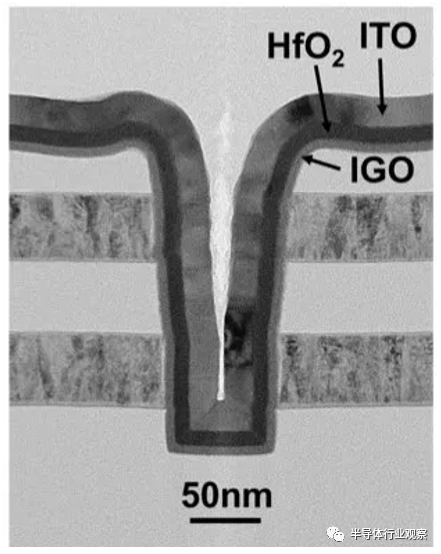

图 1:测试结构展示了 IGO、ITO 和 HfO2的共形 ALD ,可以钝化氧空位,同时实现比溅射更深的结构。来源:2023年VLSI研讨会

众所周知,界面散射会降低非常薄的半导体通道(包括硅通道)的迁移率。在铟基氧化物中,氧空位还会导致迁移率下降和阈值电压不稳定。东京大学的 Kaito Hikake 及其同事在研究氧化铟镓 (IGO) 时提出,环境中的氧气也可以扩散到通道中,从而形成深层陷阱。控制氧含量和钝化与氧相关的缺陷是这些材料面临的根本挑战,研究人员正在采取几种不同的方法。新加坡国立大学的一个独立小组在 Sonu (Devi) Hooda 提出的工作中使用了 ITO/IGZO(氧化铟镓锌)异质结构。在他们的工作中,ITO 厚度控制沟道载流子浓度,补偿氧缺陷。同时,异质结构避免了仅在 ITO 中出现的 SS 退化和阈值电压偏移。有效移动性,110 厘米处2/V-sec,优于其他结果,而且重要的是,与通道厚度无关。

含有或不含镓的氧化铟

Kaito Hikake 的小组重点研究了 In-Ga-Zn 三元相图中的 In-Ga 部分。纯氧化铟实现更高的迁移率;纯氧化镓允许更大的带隙。介于两者之间,氧化铟镓 (IGO) 最大限度地提高了热稳定性。因此,虽然 IGO 在理论上非常有趣,但之前很少有关于实际设备的报道。

东京大学研究人员确定,In3Ga2Ox在迁移率、阈值电压和稳定性之间提供了最佳权衡。虽然可以通过溅射进行沉积,但研究人员对垂直柱 FET 结构特别感兴趣,并因其保形性以及出色的厚度和成分控制而选择了 ALD。通过交替GaOx和InOx子周期,他们定义了膜的组成。接下来,他们重复这种ALD异质结构沉积尽可能多的次数,以产生所需的总体厚度。

研究人员制造了带有 ITO 栅极电极和氧化铪栅极电介质的单栅极和双栅极器件。双栅极器件比单栅极器件实现了更好的驱动电流和迁移率,这显然是由于顶部电介质层对沟道的钝化所致。具体地,使用臭氧(O3)源生长的ALD HfO2稳定了漏极电流和迁移率,而不改变阈值电压。其他钝化工艺,包括溅射 SiO2和使用 H2O氧源的 HfO2 ALD,导致强烈的负阈值电压漂移。

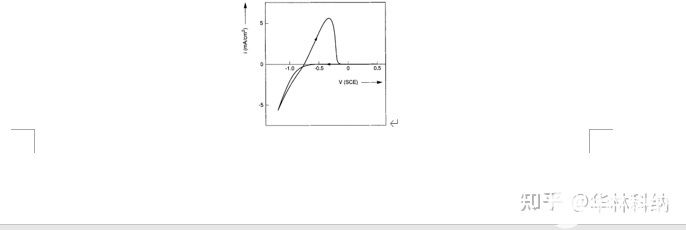

最后,Zhuo Cheng Chang及其普渡大学的同事观察到,镓确实有助于稳定这些器件,但相对于纯 In2O3 ,仍然会降低电气性能。他们将氧化铟中阈值电压的不稳定性归咎于氧空位的产生在栅极偏压应力下,空位充当浅施主。他们认为,O2退火可以钝化这些潜在的施主位点,而不会引入Zn或Ga掺杂的负面影响。

实用性和BEOL设备

这里讨论的器件都无法与领先的CMOS竞争。然而,它们与非晶硅(αSi)和其他可以使用低温工艺的半导体处于同一区域。然而,无论具体材料如何,很明显,基于铟的氧化物半导体在制造和使用过程中对氧浓度都极其敏感。实际器件的正确封装对于在湿法清洗、CMP 以及晶体管制造和 BEOL 步骤之后的其他工艺步骤中保护它们至关重要。这些材料的灵活成分是否会成为一种优势,为工艺工程师提供多种方法来根据其特定需求优化设备,还是成为一致、可靠行为的根本障碍,还有待观察。

审核编辑:汤梓红

-

3D

+关注

关注

9文章

2935浏览量

108972 -

存储器

+关注

关注

38文章

7586浏览量

165608 -

封装

+关注

关注

128文章

8256浏览量

144236 -

晶体管

+关注

关注

77文章

9887浏览量

139956 -

CMP

+关注

关注

6文章

151浏览量

26337

原文标题:3D存内计算,新突破

文章出处:【微信号:晶扬电子,微信公众号:晶扬电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

液晶显示器中常用芯片类型

液晶显示器是什么原理制造的

液晶显示器制造工艺流程基础技术

低阻ITO玻璃的制造工艺

石墨烯电极将催生超薄软性OLED显示器

基于光电显示用透明导电膜及玻璃(ITO)的原理

曲面显示器是怎么设计的

显示器处理器芯片是什么?显示器处理器芯片市场的发展趋势

新研究:将ITO从显示器移至芯片

新研究:将ITO从显示器移至芯片

评论