1、异步复位同步释放

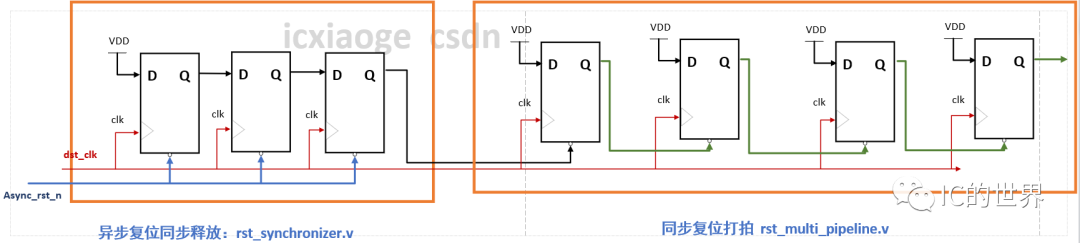

异步复位同步释放:rst_synchronizer.v

采用3级同步打拍模块

异步复位async_rst_n连接到3级同步寄存器复位端

时钟采用目的时钟dst_clk

第一个寄存器输入D端接高电平,Q端驱动下一级寄存器的D端,

最后一级reg的Q端就是作为模块输出的已同步到dst_clk时钟域的复位信号

模块特点:

采用3级同步器减少亚稳定发生概率(7nm,5nm时钟频率一般在1GHz左右会采用3级同步器)

一般设计会采用定制模块实现,保证3级寄存器的上一级Q端和下一级D端延时很小

2、同步复位打拍模块 同步复位同步打拍:rst_multi_pipeline.v

采用多个寄存器实现

所有寄存器输入D端接高电平

输出q端作为复位连接到下一级寄存器的复位端rst_n

首个寄存器复位端来自rst_synchronizer.v的输出复位信号

模块特点:

采用多级寄存器同步打拍,便于时序收敛,布局布线以及增加驱动能力

采用多级寄存器打拍,还能便于芯片整理复位平衡的。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5390浏览量

121901 -

延时器

+关注

关注

1文章

36浏览量

15283 -

同步器

+关注

关注

1文章

98浏览量

14802 -

异步复位

+关注

关注

0文章

47浏览量

13378 -

CLK

+关注

关注

0文章

127浏览量

17290

原文标题:异步复位同步释放与同步复位打拍

文章出处:【微信号:处芯积律,微信公众号:处芯积律】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

Xilinx FPGA异步复位同步释放—同步后的复位该当作同步复位还是异步复位?

浅析异步复位同步释放与同步复位打拍模块

浅析异步复位同步释放与同步复位打拍模块

评论