几年前FPGA时钟只需要连接一个单端输入的晶振,非常容易。现在不同了,差分时钟输入,差分信号又分为LVDS和LVPECL,时钟芯片输出后还要经过直流或交流耦合才能接入FPGA,有点晕了,今天仔细研究一下。

FPGA输入时钟要求

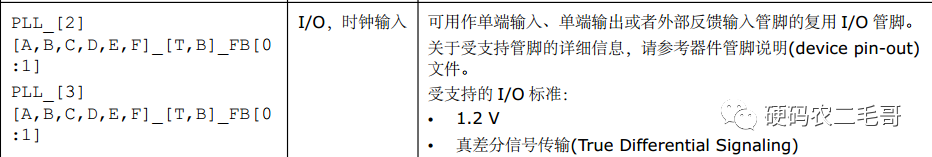

FPGA手册中对时钟输入的描述:

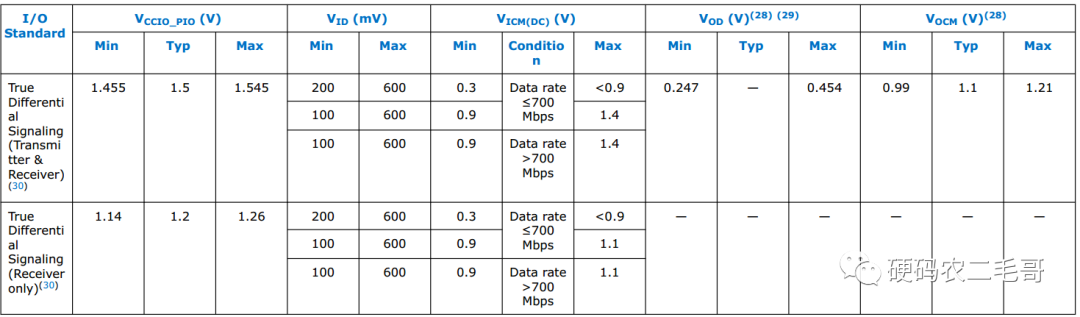

差分I/O电平标准:

真差分信号电压不能超过VICM(max) + VID(max)/2 。

直流耦合与交流耦合

时钟的发送端和接收端都有各自的电平接口类型,它们有可能不相同也可能是相同的。 这个时候通常就会有两种连接方式,即AC耦合以及DC耦合。 其实说简单也很简单, AC耦合就是中间用电容把发送接收端的共模电平隔开,而DC耦合就是不加电容 。交流耦合(AC Coupling)就是通过隔直电容耦合,去掉了直流分量。直流耦合(DC Coupling)就是直通,交流直流一起过,并不是去掉了交流分量。

LVDS与LVPECL

时钟芯片输出时钟信号通常有LVDS和LVPECL。

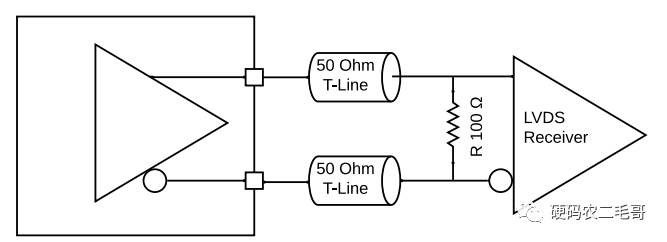

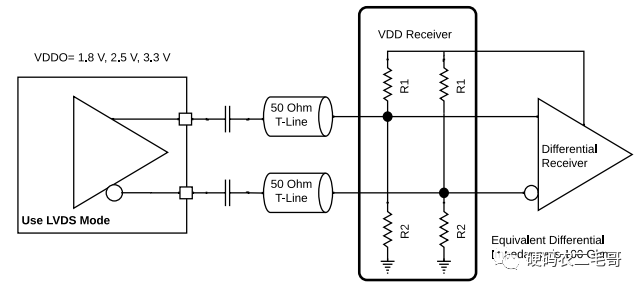

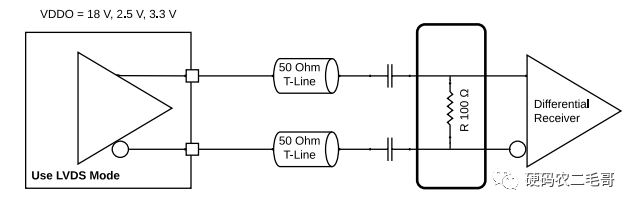

当时时钟芯片输出LVDS信号时

DC耦合

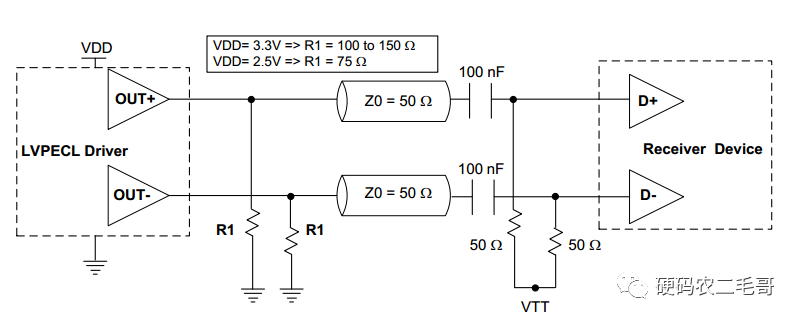

两种AC耦合方式。

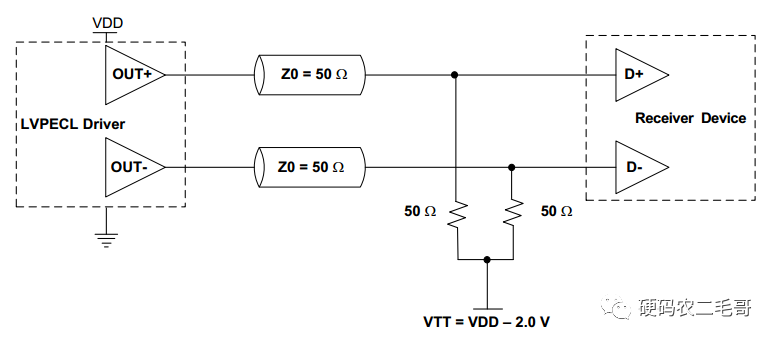

当时钟信号输出LVPECL信号时

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1628文章

21722浏览量

602896 -

lvds

+关注

关注

2文章

1042浏览量

65783 -

时钟芯片

+关注

关注

2文章

249浏览量

39876 -

差分信号

+关注

关注

3文章

367浏览量

27676 -

LVPECL

+关注

关注

2文章

27浏览量

17933

发布评论请先 登录

相关推荐

可否直接使用LVPECL输出的有源晶振交流耦合至AD的时钟引脚?

原本打算使用FPGA的PLL输出端口得到AD的输入时钟,但发现FPGA的时钟输出jitter过大(600ps),远大于得到优秀SNR所需的抖动水平

如图为AD9233的推荐的

发表于 12-22 06:29

LMK00725是否支持LVDS或者LVPECL的差分交流耦合输入呢?

您好,目前我正在使用LMK05318+LMK00725的方案进行≥10路的时钟生成与FANOUT;前者LMK05318的LVDS与LVPECL输出均为AC耦合,

而LMK00725手册中

发表于 11-11 07:42

ADS5404可以使用LVDS或LVPECL的时钟源头吗?

ADS5404的时钟电平要求为如下:

这么高的标称值该使用什么电平的时钟芯片提供呢?LVDS和LVPECL的摆幅都应该达不到吧?

为什

发表于 12-13 07:42

请问高速AD差分时钟驱动能使用LVPECL输出的有源晶振交流耦合至AD的时钟引脚吗?

原本打算使用FPGA的PLL输出端口得到AD的输入时钟,但发现FPGA的时钟输出jitter过大(600ps),远大于得到优秀SNR所需的抖动水平如图为AD9233的推荐的

发表于 11-02 09:25

请问FPGA管脚是否具有电平判决功能将输入的模拟时钟信号判决为数字时钟信号?

1.FPGA管脚是否具有电平判决功能将输入的模拟时钟信号判决为数字时钟信号?2.单载波输入,LVDS

发表于 12-20 09:31

ADCLK946是否可以直接给AD9739作为时钟驱动LVDS

ADCLK946输出为LVPECL,是否可以直接给AD9739作为时钟驱动LVDS,在LVPECL转至LVDS电路设计上有需要注意的么?目前

发表于 01-03 10:41

请问selectIO向导假设输入时钟是280MHz吗?

lvds时钟的时钟。例如,SVGA的时钟对频率为40MHz,串行数据频率为280MHz。但是selectIO向导假设输入时钟是280MHz

发表于 07-17 07:20

如何使用BLVDS或其他驱动Kintex LVPECL输入的方法的信息?

我正在哀悼7系列设备上LVPECL支持的消亡。我有一个需要360MHz LVPECL输入时钟的DAC。 Kintex LVDS(247mV,min)不具备

发表于 07-19 14:43

如何在LVPECL、VML、CML、LVDS和子LVDS接口之间转换

本文我们将回过头来了解如何在 LVPECL、VML、CML、LVDS 和子 LVDS 接口之间转换。系统当前包含 CML 与 LVDS 等各种接口标准。理解如何正确耦合和端接串行数据通

发表于 11-21 07:59

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器

概述

The MAX9376 is a fully differential

发表于 12-19 12:11

•1717次阅读

获得连接:LVPECL、VML、CML、LVDS 与子 LVDS 之间的接口连接

获得连接:LVPECL、VML、CML、LVDS 与子 LVDS 之间的接口连接

发表于 11-04 09:52

•5次下载

使用DS314xx时钟同步IC,具有1Hz输入时钟

本应用笔记介绍了ADI公司的DS314xx时钟同步IC如何进行现场升级,以接受并锁定至1Hz输入时钟信号。它还描述了在少数情况下需要1Hz时钟监控功能和系统软件支持。有了这些元件,使用DS314xx器件构建的系统就可以与1Hz和

CDCLVP111-SP具有可选输入时钟驱动器的低电压1:10 LVPECL数据表

电子发烧友网站提供《CDCLVP111-SP具有可选输入时钟驱动器的低电压1:10 LVPECL数据表.pdf》资料免费下载

发表于 08-20 09:15

•0次下载

CDCLVP111低压1:10 LVPECL,内置可选输入时钟驱动器数据表

电子发烧友网站提供《CDCLVP111低压1:10 LVPECL,内置可选输入时钟驱动器数据表.pdf》资料免费下载

发表于 08-21 11:37

•0次下载

浅谈FPGA输入时钟要求 LVDS与LVPECL讲解

浅谈FPGA输入时钟要求 LVDS与LVPECL讲解

评论