逻辑分析仪(Logic Analyzer)是一种分析数字信号逻辑时序的仪器,能够精确捕获和显示多路数字信号,提供信号时序、协议分析等功能。也是嵌入式工程师日常开发中,极为常用的工具之一。

现在,我们使用基于树莓派主控芯片的合宙RP2040开发板,就可以低成本快速DIY逻辑分析仪。

9.9元自制100M逻辑分析仪

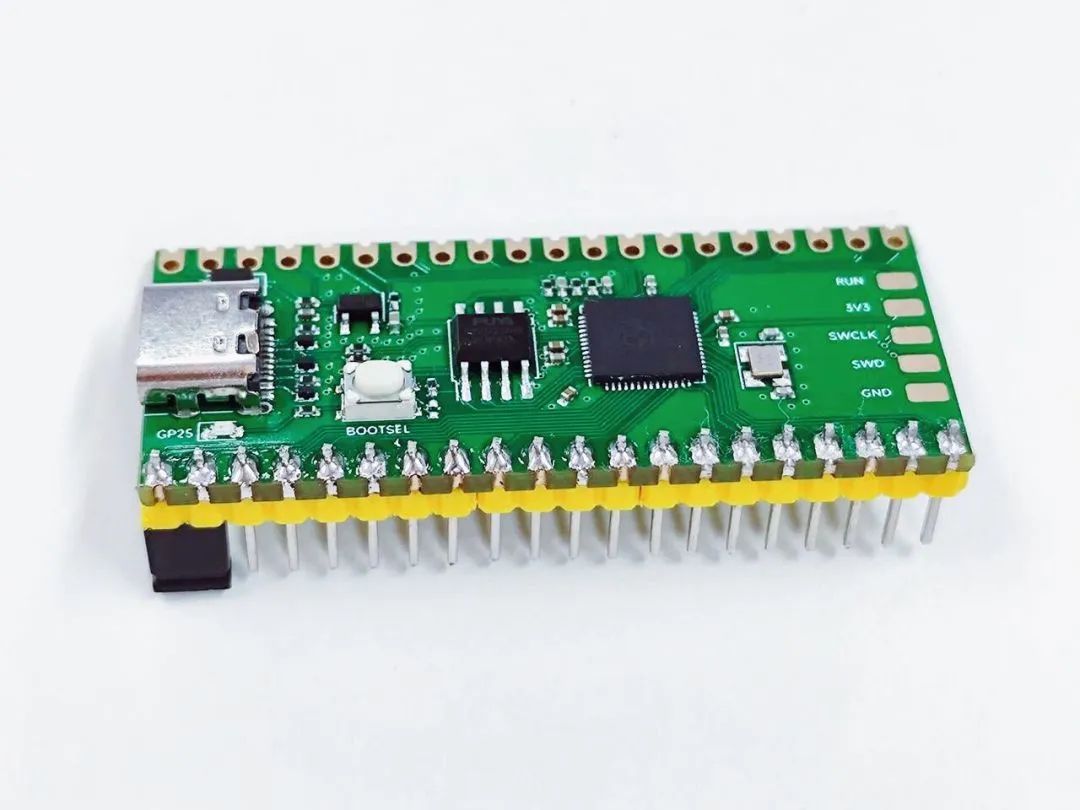

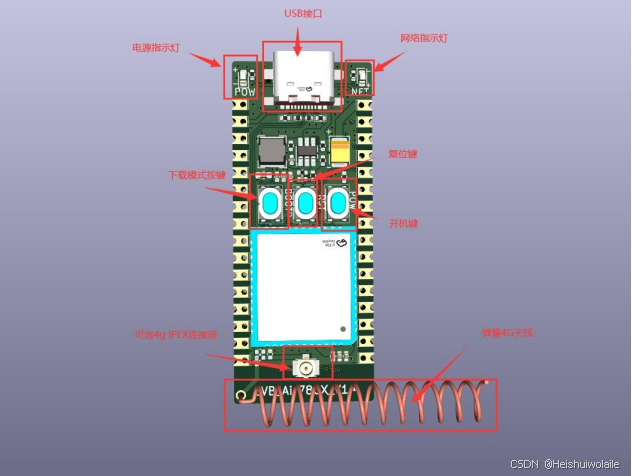

CORE-RP2040——合宙推出的9.9家族又一款新品,采用树莓派RP2040芯片作为核心,引脚定义兼容官方PICO开发板,并在官方基础上升级到4MB Flash和Type-C接口。

结合开源固件,可实现100M的逻辑分析仪功能:

逻辑分析仪开源仓库:

https://github.com/gusmanb/logicanalyzer

功能支持

基于合宙RP2040开发板的逻辑分析仪,可支持如下功能:

支持3.1K至100Mhz的采样频率;

支持24通道输入,通过菊花链最高可支持120通道;

最高支持32767个采样点;

支持多种客户端,全平台可用。

硬件准备

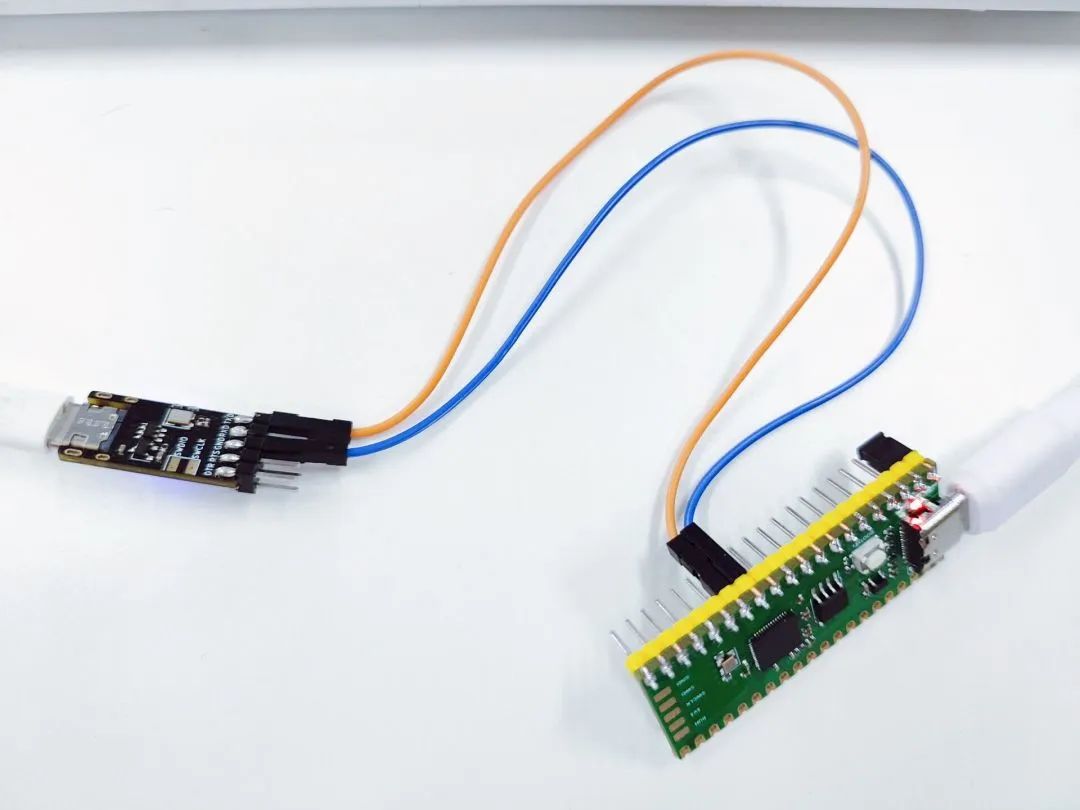

我们需要一块合宙RP2040开发板,并且需要将GP0与GP1两个引脚进行短接处理。

刷入固件

按住BOOT按键,再插入USB,进入升级模式。

下载固件文件,复制进入U盘,即可刷入成功:

https://github.com/gusmanb/logicanalyzer/releases/download/V5.0.0.0/Firmware-LogicAnalyzer-5.0.0.0-PICO.uf2

连接软件

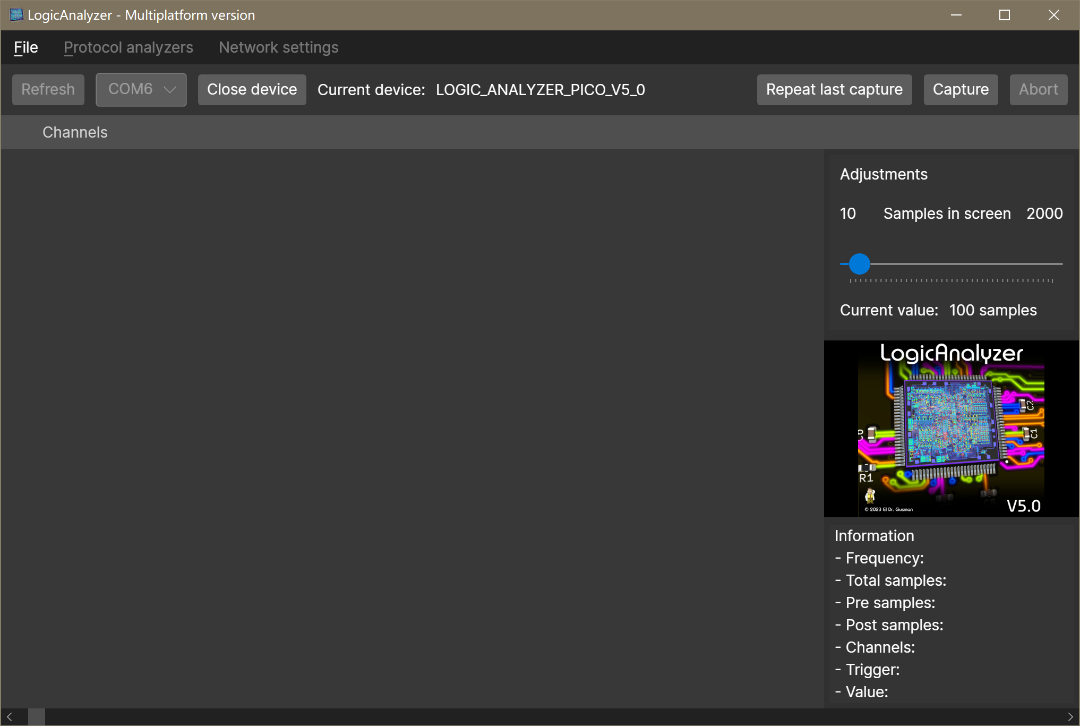

这里默认使用开源仓库作者自行编写的客户端软件:

https://github.com/gusmanb/logicanalyzer/releases/latest

下载自己需要的系统版本,本文选用:

LogicAnalyzer-5.0.0.0-win-x64.zip

选择树莓派虚拟出来对应的串口,连接上:

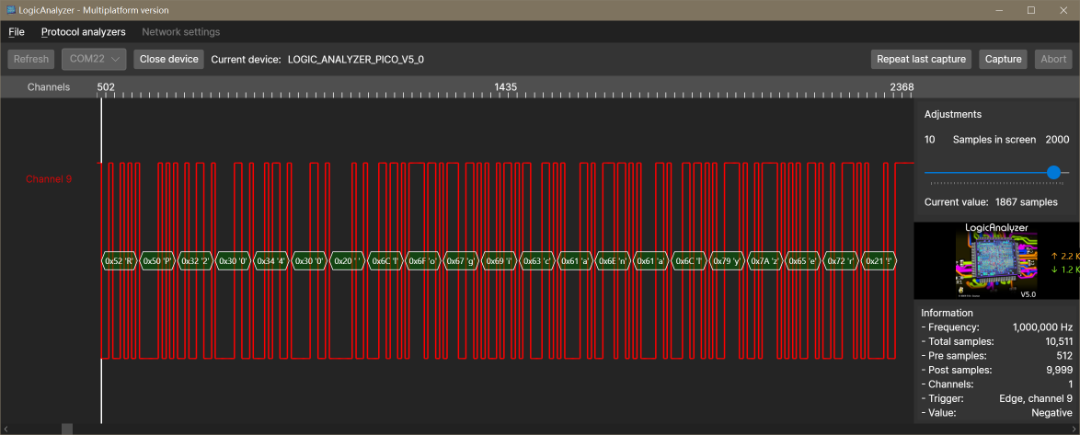

抓取数据

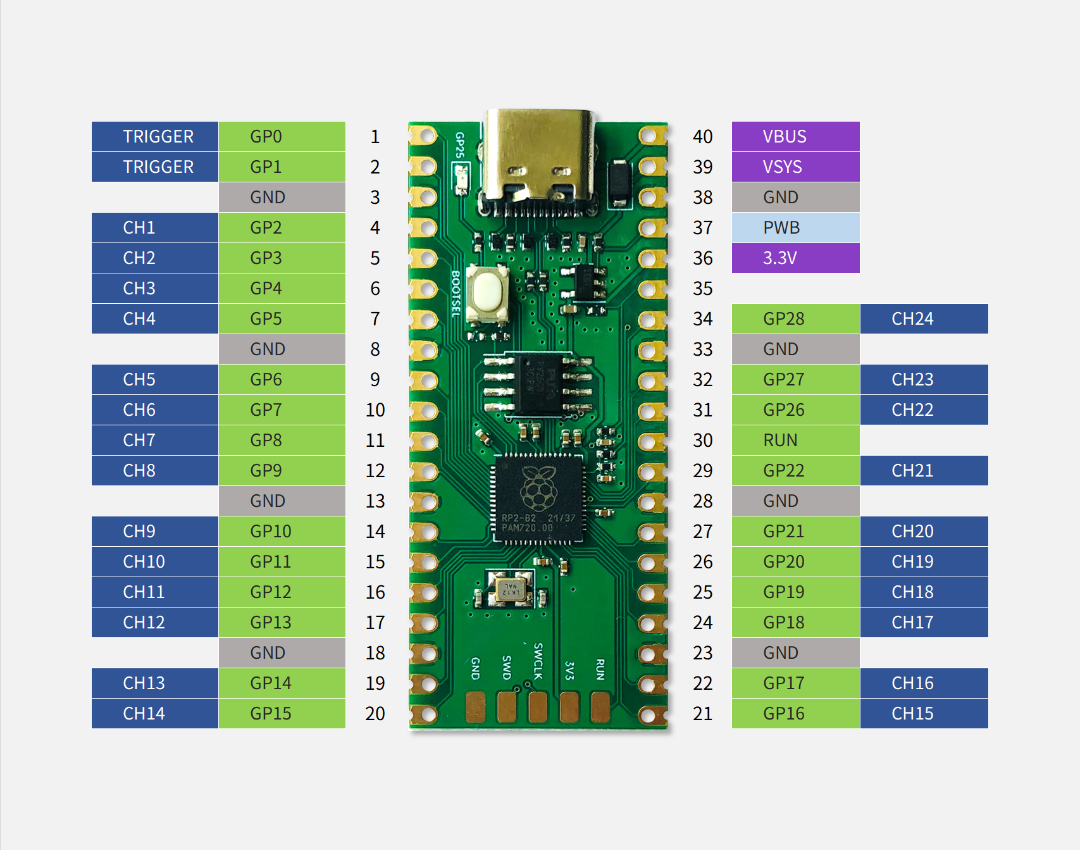

将合宙RP2040开发板的GND与我们需要测量的板子的GND相连,再将需要测量的引脚连接到开发板的GPIO上。

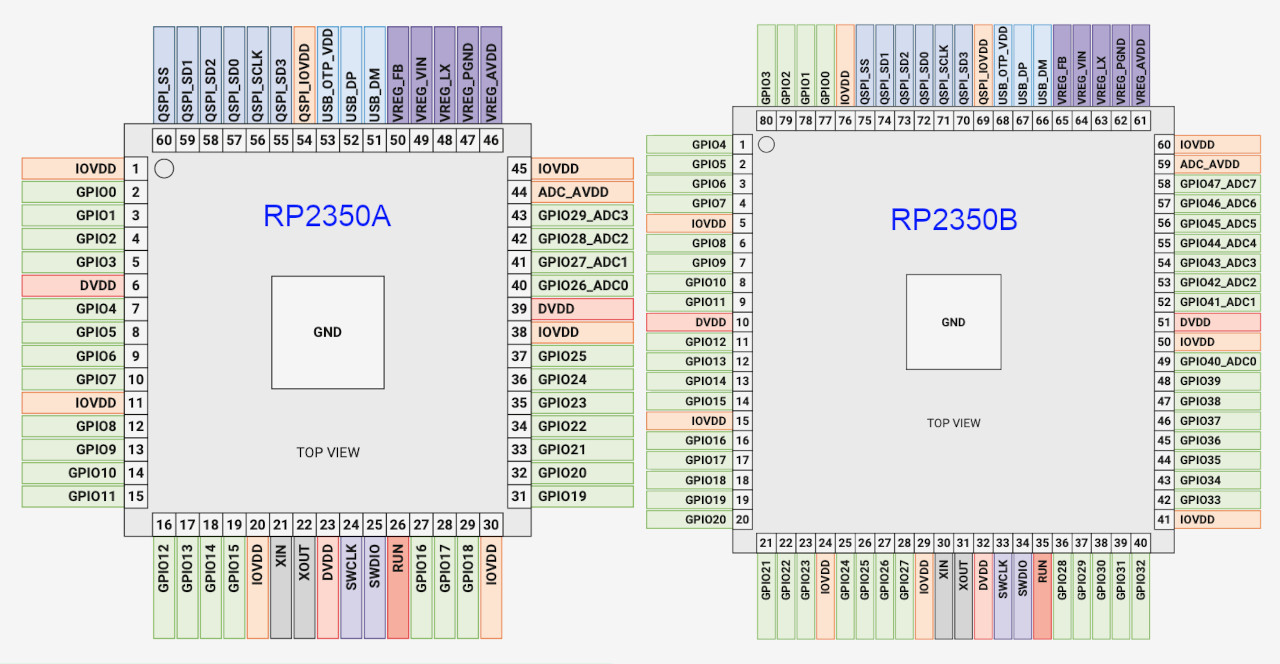

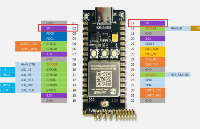

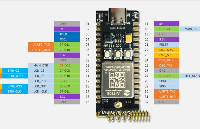

通道编号与GPIO编号的对应关系如下:

我们连接上被测引脚后,就能开始抓取了:

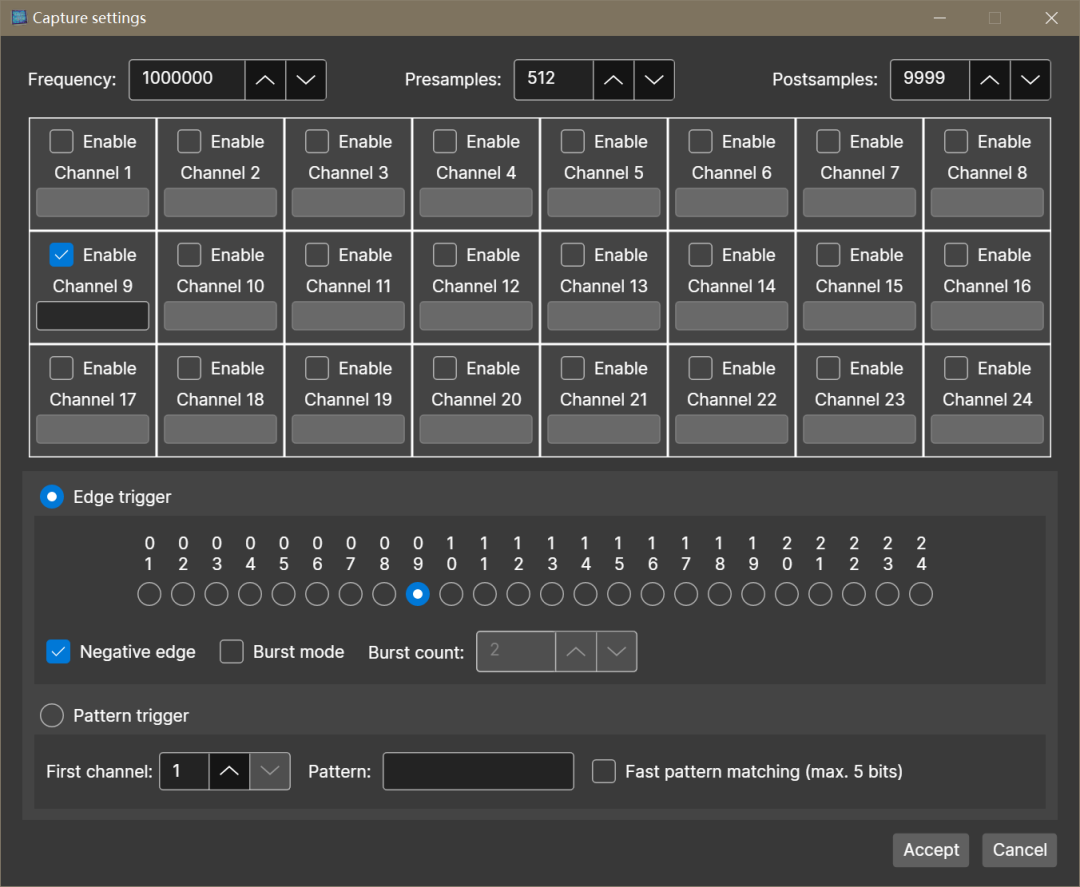

点击Capture,选上对应的通道、抓取频率与采样数、触发条件,点击Accept即可开始抓取:

-

DIY

+关注

关注

176文章

888浏览量

349443 -

开发板

+关注

关注

25文章

5144浏览量

98436 -

合宙通信

+关注

关注

0文章

148浏览量

1864

发布评论请先 登录

相关推荐

RP2350与RP2040全面对比

RP2350 数据手册及深度了解功能性能特性和开源项目案例

【社区工程师专题系列第九期】一个狂热的开源爱好者和传播者——乔楚

Made with KiCad(六):合宙DAPLink开发板

如何使用Air780E开发板?看这篇就够了!

我用了3分钟,从零实现了单片机的点灯开发!

合宙低功耗4G模组AIR780EX ——开发板使用说明

合宙LuatOS开发板Core_Air780EP使用说明

ubuntu上交叉编译rp2040

合宙Air780EP模块——AT指令MQTT接入OneNET开发指南

合宙RP2040开发板轻松DIY

合宙RP2040开发板轻松DIY

评论