如今,高速(ADC)的种类和厂商众多,要选择一款合适的产品可能并非易事。缩小范围之后,最终的抉择往往是选取缓冲型还是无缓冲型(开关电容)转换器。因为受尺寸和功耗的影响,通常倾向于无缓冲型。那么如何设计无缓冲式ADC呢?

是否需要使用无缓冲型ADC?

绶沖型与无缓冲型ADC之间存在很大差异。缓冲型的优点比较直观,缓冲器带来的这些好处可以在一定程度上简化模拟接口设计 ,并日支持更高的输入带宽。然而,缓冲器的缺点也是存在的,尽管不太明显。缓冲器通常需要较高的电源电压,这会带来额外的电源设计问题。ADC的噪声和线性度也会受到影响。因此在电源方面,整体ADC设计大受影响。

在系统层次上,多数高速ADC的输入来用放大器驱动。因此,在常见的信号链应用中 ,缓冲器的电源有点多余。如果模拟接口电路和放大器设買为直接驱动采样网络,而不使用缓冲器,则整个系统可以得到更好的优化。

去掉缓冲器是多数系统设计师的选择,这样可以额外节省功耗。

如何设计无缓冲ADC?

一、挑战

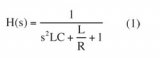

放大器级的设计由两个彼此相关的不同级组成,因此问题变得难以在数学上建模,特别是因为有非线性因素与这两级相关。第一步是选择用来缓冲传感器输出并驱动ADC输入的放大器。第二步是设计一个低通滤波器以降低输入带宽,从而最大限度地减少带外噪声。

理想的放大器是提供刚刚好的带宽以正确缓冲传感器或变送器产生的信号,而不会增加额外噪声,并且功耗为零,但实际放大器与此相距甚远。在大多数情况下,放大器规格将决定整体系统性能,尤其是在噪声、失真和功耗方面。为了更好地弄清楚问题,第一步是了解离散时间ADC的工作原理。

离散时间ADC获得连续时间模拟信号的样本,然后将其转换为数字码。当信号被采样时,根据模拟转换器的类型,同一固有问题有两种不同的情况:

SARADC集成一个采样保持器,其基本上由一个开关和一个电容组成,作用是保持模拟信号直到转换完成。

离散时间∑-ADC或过采样转换器实现了类似的输入级,即具有一定内部电容的输入开关。∑-ADC的采样机制略有不同,但采样输入架构类似,使用开关和电容来保持模拟输入信号的副本。

在这两种情况下,开关都是用CMOS工艺实现,闭合时电阻为非零值,通常为几欧姆。此串联电阻与采样电容(pF级)的组合,意味着ADC输入带宽常常非常大,在许多情况下要远大于ADC采样频率。

二、带宽问题

对转换器来说,输入信号带宽是一个问题。在采样理论中,我们知道高于奈奎斯特频率(ADC采样频率的一半)的频率信号应被移除,否则这些频率信号将在目标频带中产生镜像或混叠。通常,噪声频谱中有相当一部分功率存在于ADC奈奎斯特频率以上的频带中。如果不处理这种噪声,它将混叠到奈奎斯特频率以下,增加本底噪声,使系统的动态范围明显降低。

ADC输入信号带宽,以及缓冲器输出带宽,是第一个要解决的问题。为确保噪声不会向下混叠,必须限制ADC输入信号的带宽。这不是一个小问题。

通常,放大器的选择是基于大信号带宽(即压摆率)和增益带宽积的规格,以便应对输入信号的极端情况,这决定了ADC可以跟踪的最快变化的信号。

然而,放大器的有效噪声带宽等于小信号带宽(通常针对小于10mVp-p的信号而考虑),这常常比大信号带宽高出至少四到五倍。

换句话说,如果大信号规格是针对500kHz而选择,那么小信号带宽很容易就能达到2MHz或3MHz,这可能会导致ADC采集到大量噪声。因此,在将模拟信号输入ADC之前,应在外部限制小信号带宽,否则测得的噪声将是ADC数据手册规格的三到四倍。

但是,这还没完。ADC内部开关电阻和电容定义了模拟输入带宽,但由于输入信号的变化,会产生时域充放电循环。每次开关(连接到采样ADC电容的外部电路)闭合时,内部电容电压可能与先前储存在采样电容上的电压不同。

三、何为反冲问题?如何解决?

下面是一个经典的模拟问题:“若有两个并联电容连接到一个开关,开关断开时,一个电容储存了一些能量,那么当开关闭合时,两个电容会发生什么?”

答案取决于充电电容储存的能量和电容之间的比率。例如,如果两个电容具有相同的值,则能量将在它们之间均分,电容端子间测得的电压将减半。

这就是反冲问题。一些ADC会执行内部校准以补偿内部误差,这称为自稳零校准。这些程序会使采样电容电压接近供电轨或另一电压,例如基准电压的一半。

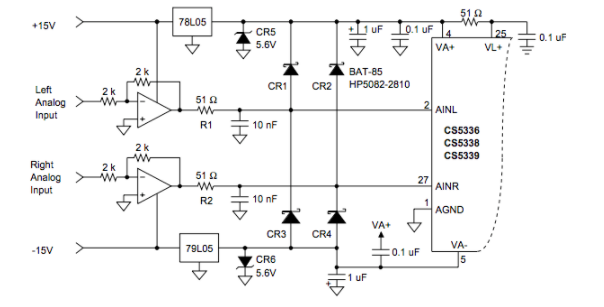

为了最大限度地解决这个问题,放大器输出应通过低通滤波器的串联电阻与外部电容隔离。电阻应足够大,以保证缓冲器不会看到虚部阻抗,但又足够小,以满足所需的输入系统带宽,并使缓冲器流出的电流在电阻上引起的IR压降最小(放大器可能无法足够快地使这种电压降稳定下来)。同时,电阻应支持外部电容减小到足够小的值,以最小化反冲而不影响建立时间。

-

放大器

+关注

关注

144文章

13736浏览量

214803 -

串联电阻

+关注

关注

1文章

197浏览量

14933 -

缓冲器

+关注

关注

6文章

2001浏览量

45880 -

低通滤波器

+关注

关注

14文章

485浏览量

47650 -

ADC转换器

+关注

关注

1文章

28浏览量

8390

发布评论请先 登录

相关推荐

无缓冲ADC设计的挑战和问题

高速无缓冲ADC的反冲

高速ADC的无缓冲式架构选择

两类高速ADC之间选择:有缓冲和无缓冲

关于ADC 输入缓冲器和保护技术分析

详解高速ADC模拟输入架构类型:缓冲型和无缓冲型资料下载

是否需要使用无缓冲型ADC?如何设计无缓冲式ADC呢?

是否需要使用无缓冲型ADC?如何设计无缓冲式ADC呢?

评论