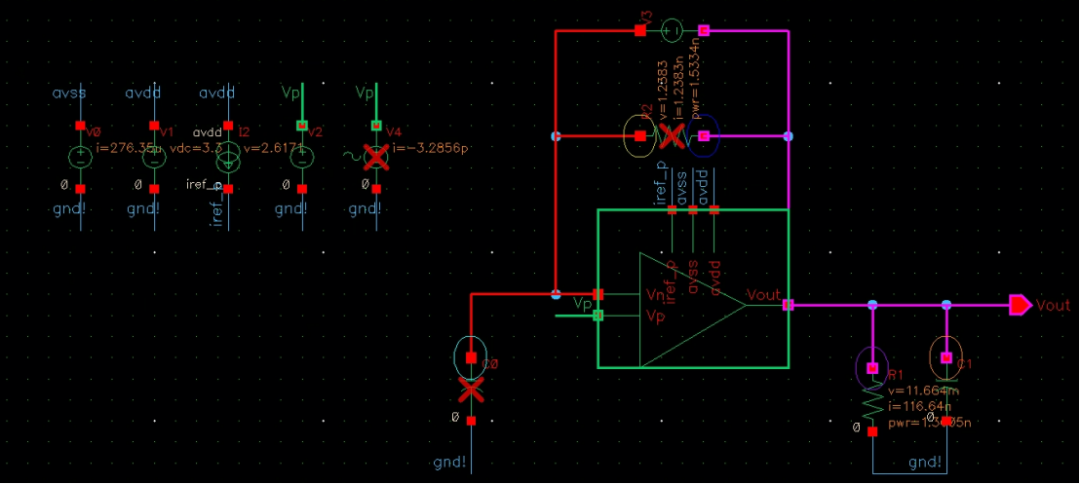

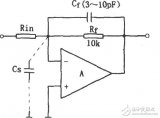

stb分析可以得到环路增益的bode图,但却不能看到环路中其他位置的AC增益大小,这在需要分析不同级的放大倍数时造成了困难。解决这个问题,可以按照下图所示的方法设计testbench。

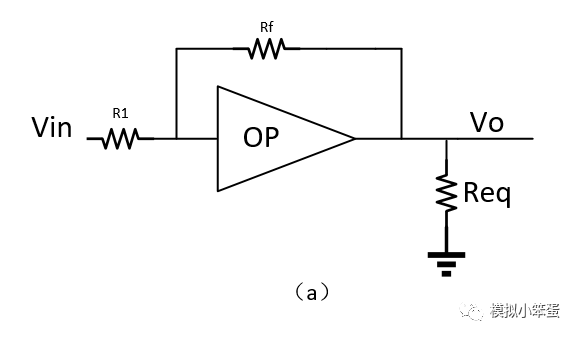

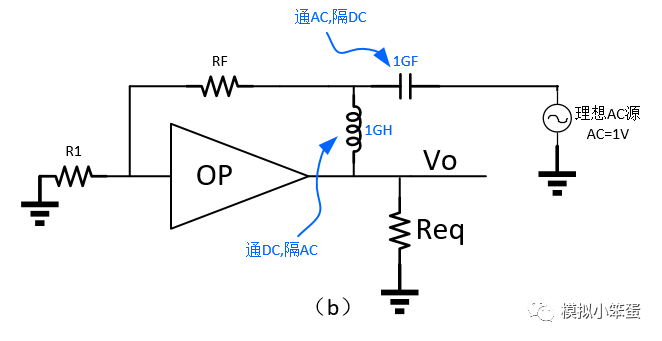

图1

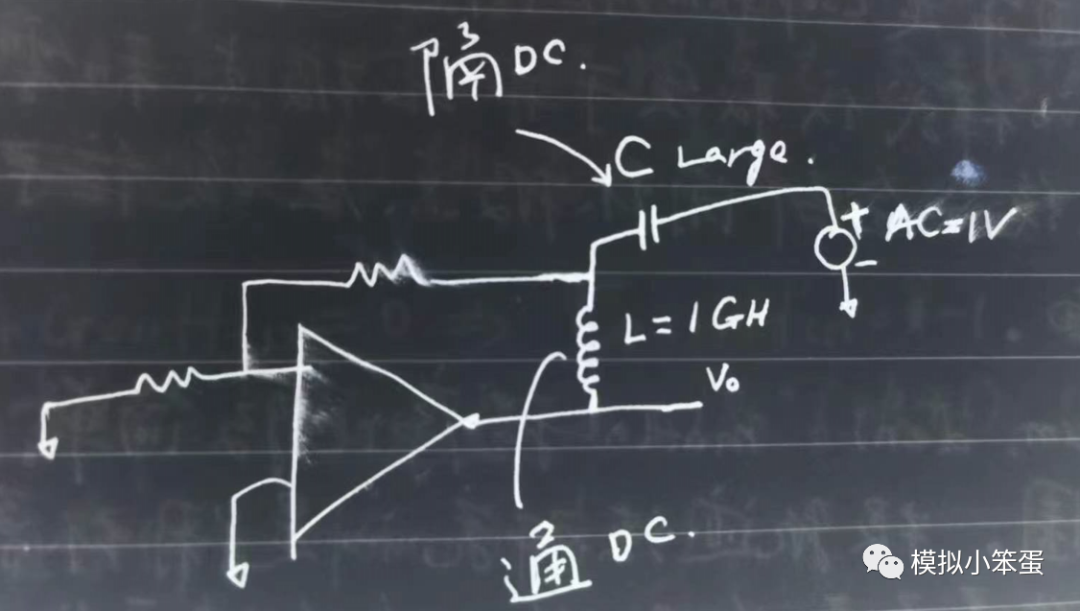

以图1a为例,对环路断环进行仿真时,除了用stb分析方式之外,可以用如图1b所示添加L、C的办法进行环路增益仿真。L的作用是通直流交流,所以电路可以认为存在直流连接,此时负反馈环路认为没有断开,因此可以保证电路直流工作点的正常。但交流时,由于L设定值很大,呈现出很大的交流阻抗,相当于“断路”,所以在交流角度此处路径又是断开的。再看电容C,它的作用是通交流隔直流。直流时,所加的AC激励源直流电平被电容隔开,不会对环路造成影响。交流时的信号可以通过电容、RF、R1的网络施加到OP输入端。

使用图1的仿真办法,激励源AC=1V,收集到的Vo即为环路增益大小。除了这点之外,可以看到电路中任何一点的小信号增益和相位情况,这一点对分析电路尤其有帮助。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

运放

+关注

关注

49文章

1231浏览量

55757 -

仿真

+关注

关注

55文章

4532浏览量

138647 -

AC

+关注

关注

1文章

596浏览量

86399 -

负反馈

+关注

关注

6文章

218浏览量

31346

发布评论请先 登录

相关推荐

热点推荐

运放-单电源运放和双电源运放

本文转自:http://www.sohu.com/a/321387578_100281310(1)分析分析:单电源运放和单电源运

发表于 11-06 18:21

•61次下载

运放的共模抑制比高有什么作用?共模抑制比比较高的运放有哪些啊?

运放的共模抑制比高有什么作用?共模抑制比比较高的运放有哪些啊? 共模抑制比(Common Mode Rejection Ratio,CMRR)是一个衡量

L、C对运放AC分析的辅助作用

L、C对运放AC分析的辅助作用

评论