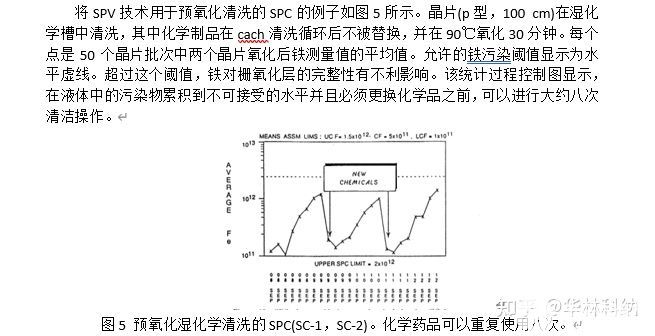

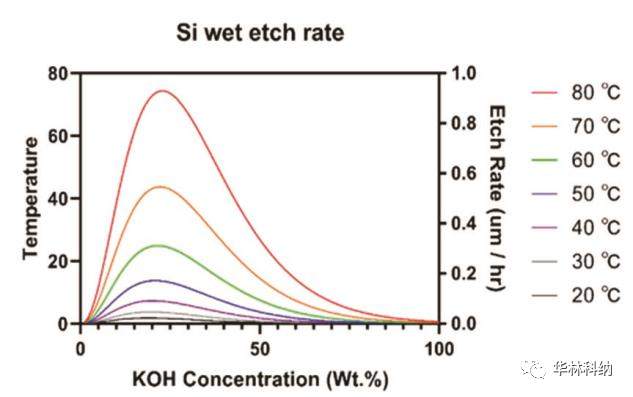

我们华林科纳通过光学反射光谱半实时地原位监测用有机碱性溶液的湿法蚀刻,以实现用于线波导的氢化非晶硅(a-Si:H)膜的高分辨率厚度控制。由a-Si:H的本征各向同性结构产生的各向同性蚀刻导致表面粗糙度<1nm的均匀蚀刻。适度的蚀刻速率使得能够在室温下以≤1nm的分辨率进行精确的终点检测。由蚀刻的A-Si:H薄膜制成的线波导具有1.2dB/cm的低传播损耗,这几乎相当于未蚀刻的线波导。

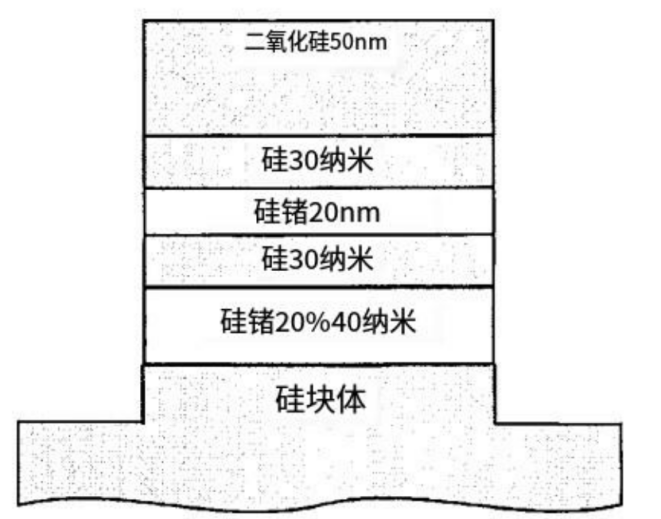

用硅材料制成的光波导部分取代全球金属布线,有望在大规模集成器件中实现更快的信号传输和更大的节能。硅材料由于其高折射率和互补金属氧化物半导体(CMOS)工艺兼容性,使得能够低成本制造尺寸与布线电路相当的超小型光学电路。在硅材料中,氢化非晶硅(a-Si:H)是一个很有前途的例子,因为它允许通过低温等离子体增强化学气相沉积(PECVD)在现有的电层上连续形成硅波导。到目前为止,一些小组已经使用a-Si:H材料制造了高质量的线波导。

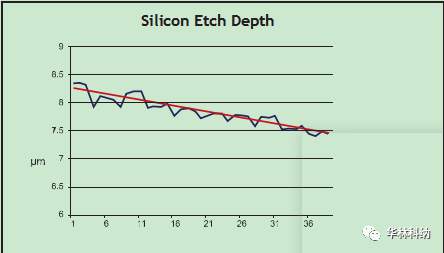

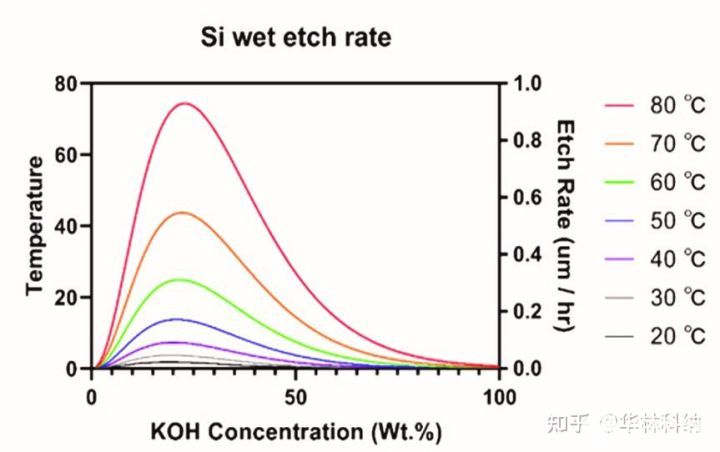

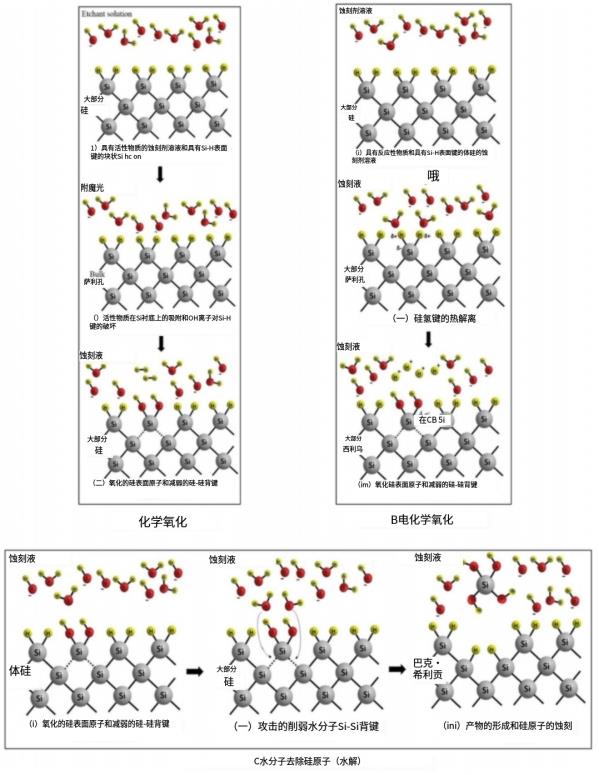

然而,用于生长a-Si:H膜的PECVD工艺通常在膜厚度上产生65%的偏差。对于厚度为200nm的膜,该偏差对应于610nm,这对于许多器件应用,尤其是那些对波长敏感的器件应用是不可接受的。因此,在PECVD之后需要额外的工艺来提供具有纳米级分辨率的精确厚度控制。化学机械抛光(CMP)已被用于调整a-Si:H膜的厚度。1-3然而,通常很难高精度地检测CMP的终点。在这封信中,作为CMP的替代方法,我们报告了湿蚀刻方法与半实时光学厚度监测器相结合的实用性,以提供分辨率为~1nm的精细厚度控制。这种方法不会显著增加沉积态a-Si:H膜的表面粗糙度,从而能够制造出具有低传播损耗of~1dB/cm的线波导。

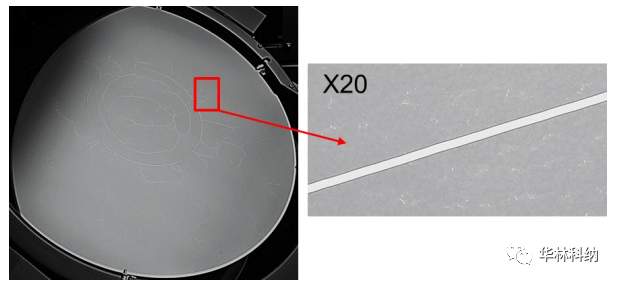

使用原子力显微镜的轻敲模式评估室温下蚀刻前后的表面粗糙度。8蚀刻前膜的均方根表面粗糙度为0.739nm,蚀刻后膜的均均方根表面粗度为0.891nm,蚀刻在220nm的膜厚度处停止。因此,即使在通过蚀刻去除约100nm的膜之后,表面粗糙度也仅略有增加。对于薄膜上的几个点获得了一致的结果。

总之,我们华林科纳为了实现PECVD沉积a-Si:H薄膜的高分辨率厚度控制,开发了一种使用TMAH溶液和光学反射光谱半实时原位厚度监测的湿法蚀刻方法。由于室温下~4nm/min的适度蚀刻速率和~2s的测量响应时间相结合,蚀刻终点可以控制在≤1nm的分辨率。即使在通过蚀刻去除约100nm的膜之后,膜的表面粗糙度也仅略有增加。由蚀刻的a-Si:H膜制成的线波导的传播损耗几乎等于未蚀刻的线波导,并且是迄今为止报道的最低的。所开发的蚀刻方法可用于生产低传播损耗波导器件,并且与CMOS工艺具有良好的兼容性。

为更好的服务客户,华林科纳特别成立了监理团队,团队成员拥有多年半导体行业项目实施、监督、控制、检查经验,可对项目建设全过程或分阶段进行专业化管理与服务,实现高质量监理,降本增效。利用仿真技术可对未来可能发生的情况进行系统的、科学的、合理的推算,有效避免造成人力、物力的浪费,助科研人员和技术工作者做出正确的决策,助力工程师应对物理机械设计和耐受性制造中遇到的难题。

审核编辑 黄宇

-

半导体

+关注

关注

334文章

27527浏览量

219930 -

监测

+关注

关注

2文章

3626浏览量

44605 -

蚀刻

+关注

关注

9文章

414浏览量

15449 -

波导

+关注

关注

3文章

97浏览量

18868 -

光波导

+关注

关注

4文章

48浏览量

10218

发布评论请先 登录

相关推荐

雷尼绍测头为什么具有各向同性

《炬丰科技-半导体工艺》CMOS 单元工艺

《炬丰科技-半导体工艺》GaN晶体蚀刻的几何方面和光子应用

用于硅片减薄的湿法蚀刻工艺控制

常见的各向同性湿法刻蚀的实际应用

锗化硅(SiGe)和硅(Si)之间的各向同性和选择性蚀刻机制

使用各向同性湿蚀刻和低损耗线波导制造与蚀刻材料对非晶硅进行纳米级厚度控制

使用各向同性湿蚀刻和低损耗线波导制造与蚀刻材料对非晶硅进行纳米级厚度控制

评论