近日,第五届集成电路EDA设计精英挑战赛正式拉开帷幕。作为国内首家EDA上市公司,也是集成电路设计自动化(EDA)产教融合联盟常务理事单位,概伦电子一直秉持与中国集成电路产业共同成长的理念,始终致力于为中国集成电路产业打造多层次的专业人才培养机制,已连续五年支持和参与该项赛事。本次概伦电子全新发布“标准单元电路的版图自动生成”企业赛题,欢迎广大同学们踊跃报名!

赛题名称

标准单元电路的版图自动生成

赛题背景

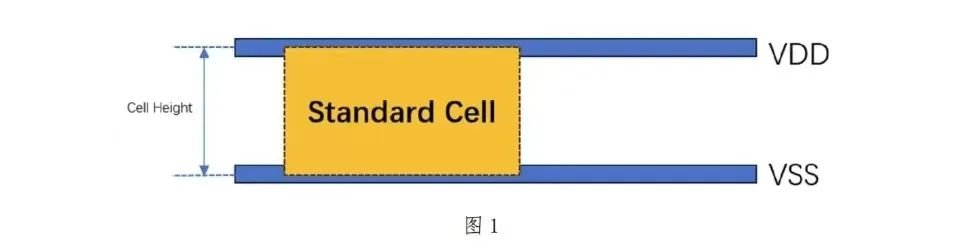

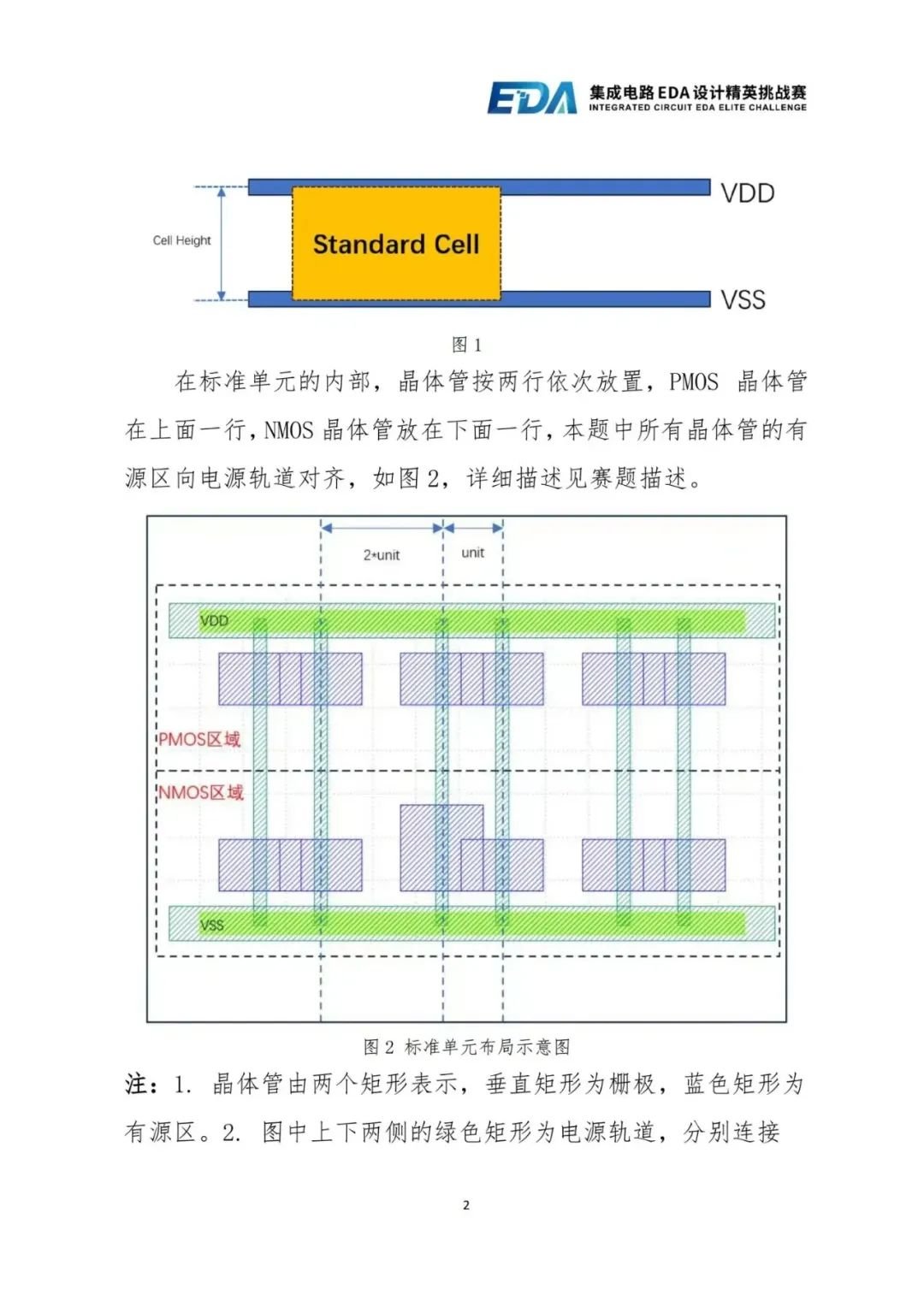

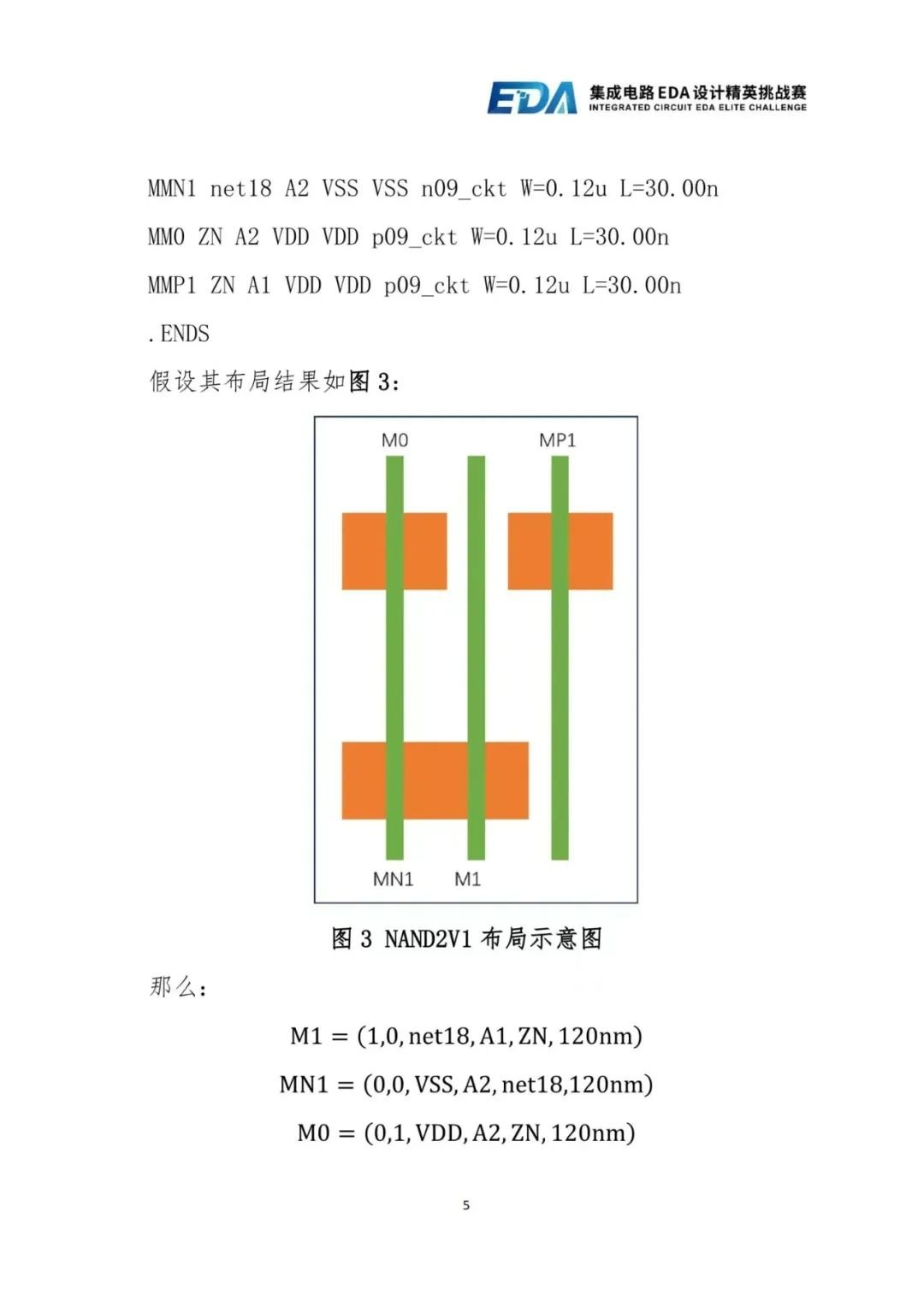

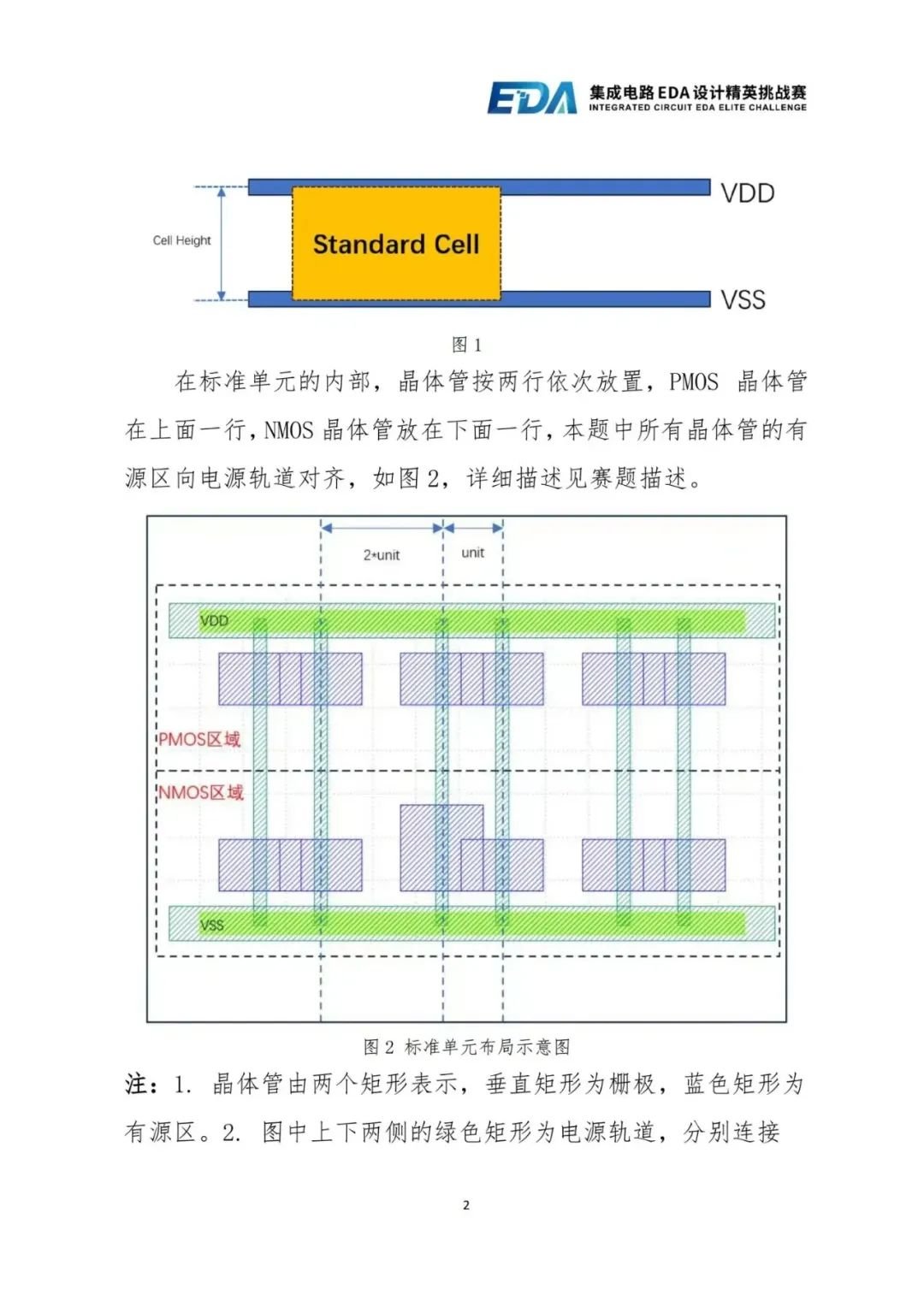

在数字电路标准单元库的开发中,版图设计是最重要的环节之一。目前标准单元的版图绘制仍然以人工绘制为主,而库中单元的数量往往多达上千颗,导致整个标准单元库的开发周期较长。如果能够提高标准单元版图设计自动化的程度,整个库的开发周期将大大缩减。标准单元的版图设计中,通常包含两个环节——晶体管布局和布线。本赛题重点关注布局环节,主要考虑组合逻辑和时序逻辑的标准单元,包含NMOS 和 PMOS 晶体管。在本题中,平面工艺下简化后的布局问题如图1所示,标准单元将被放在两条电源轨道(Power Rail)之间,高度固定,宽度不定。

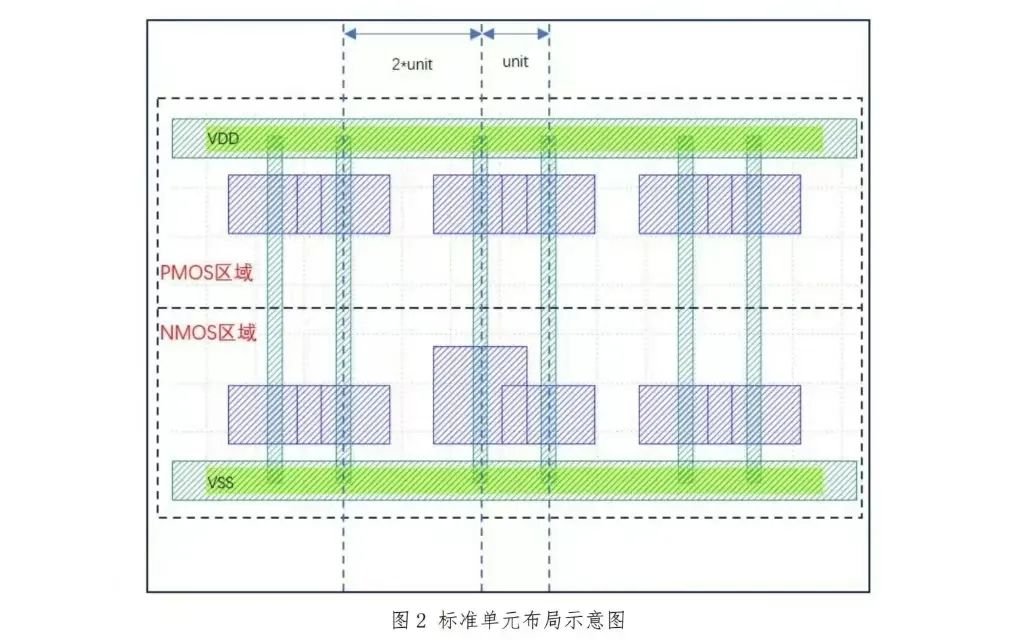

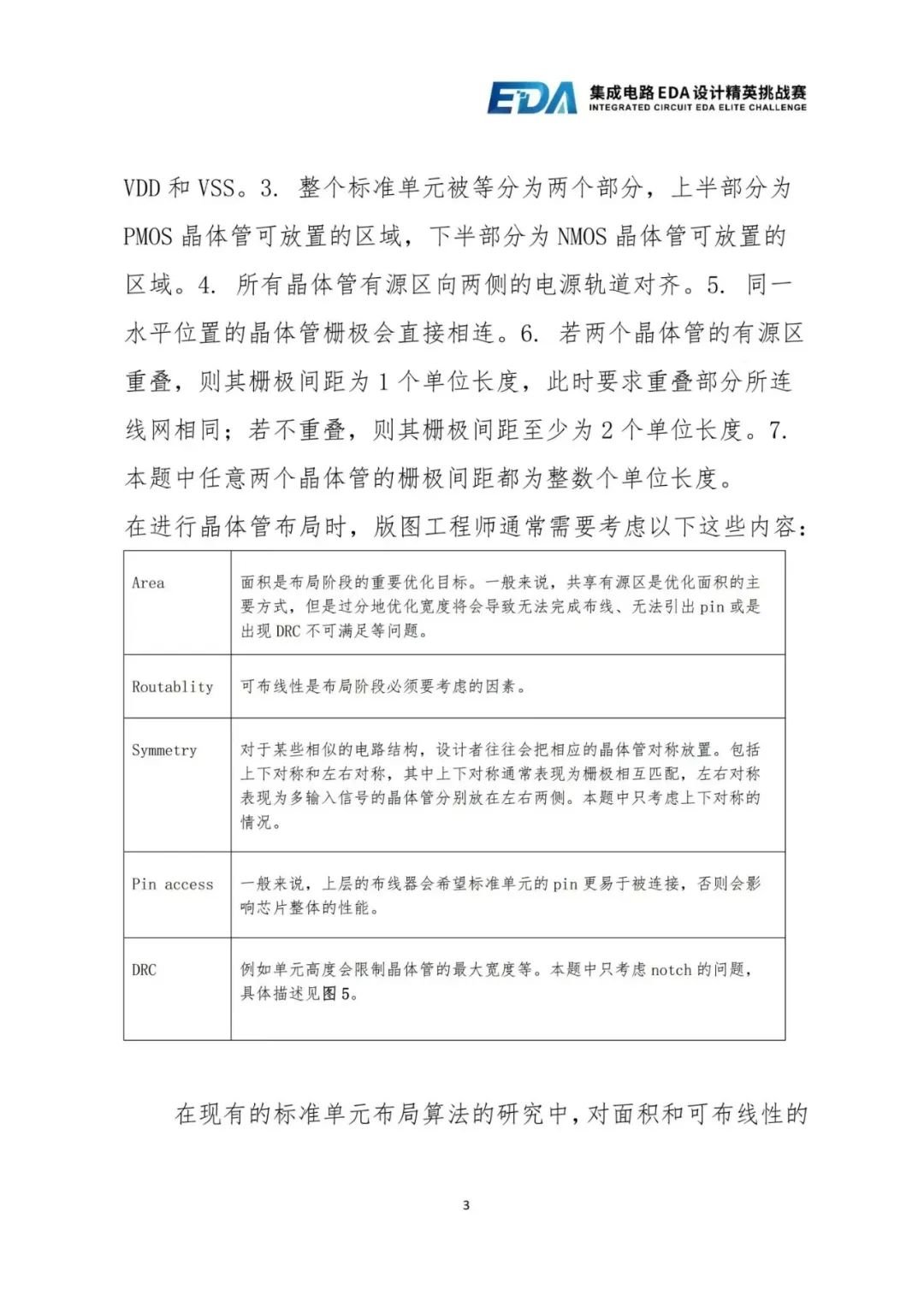

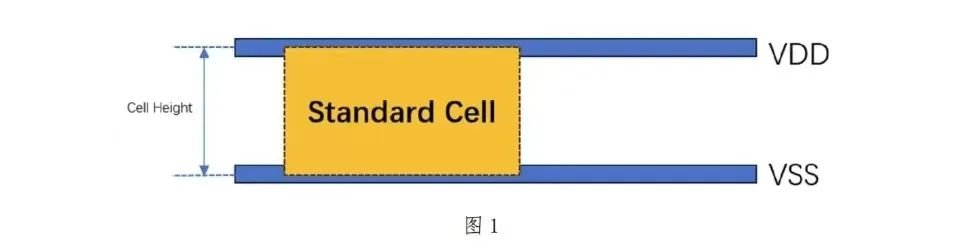

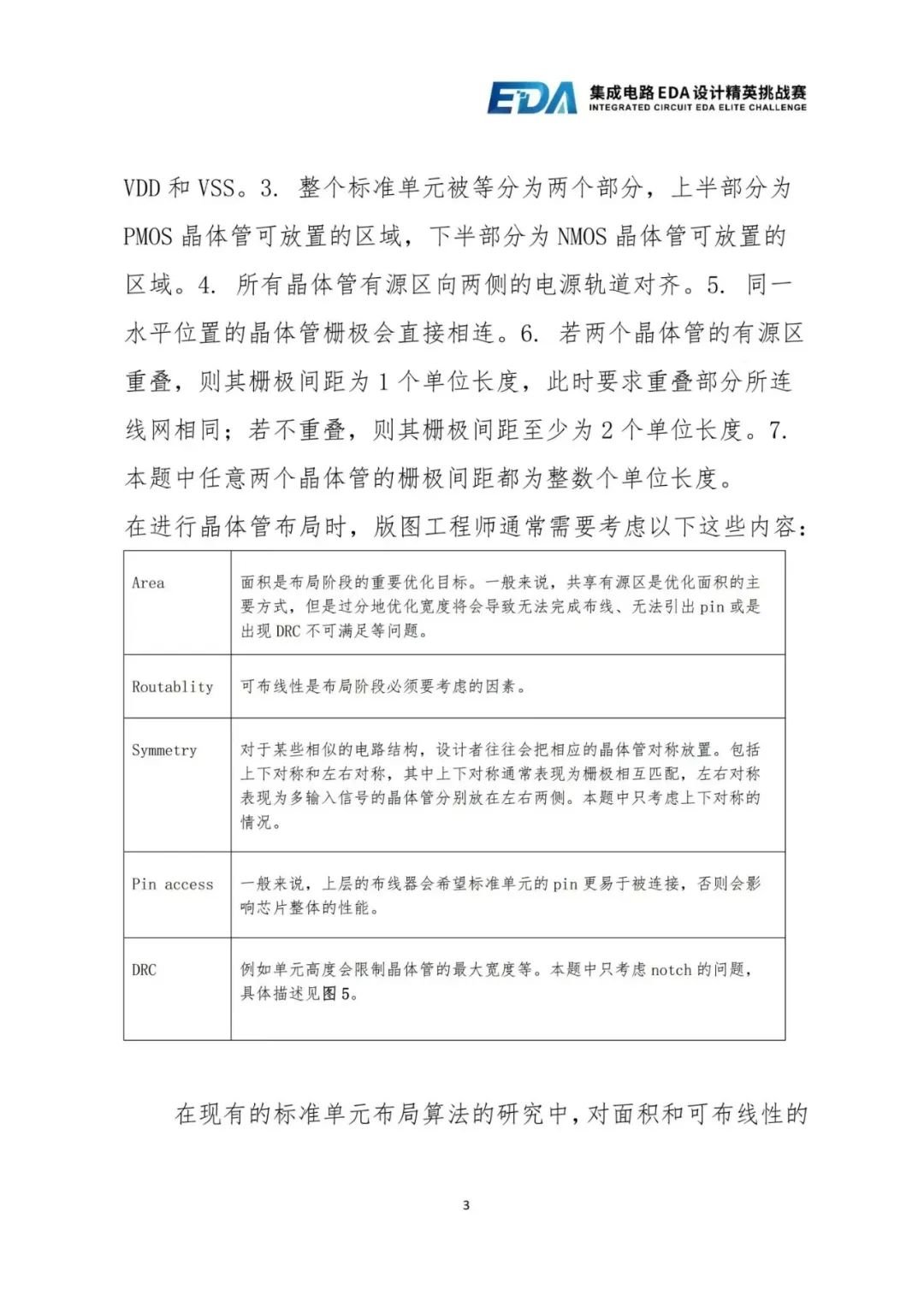

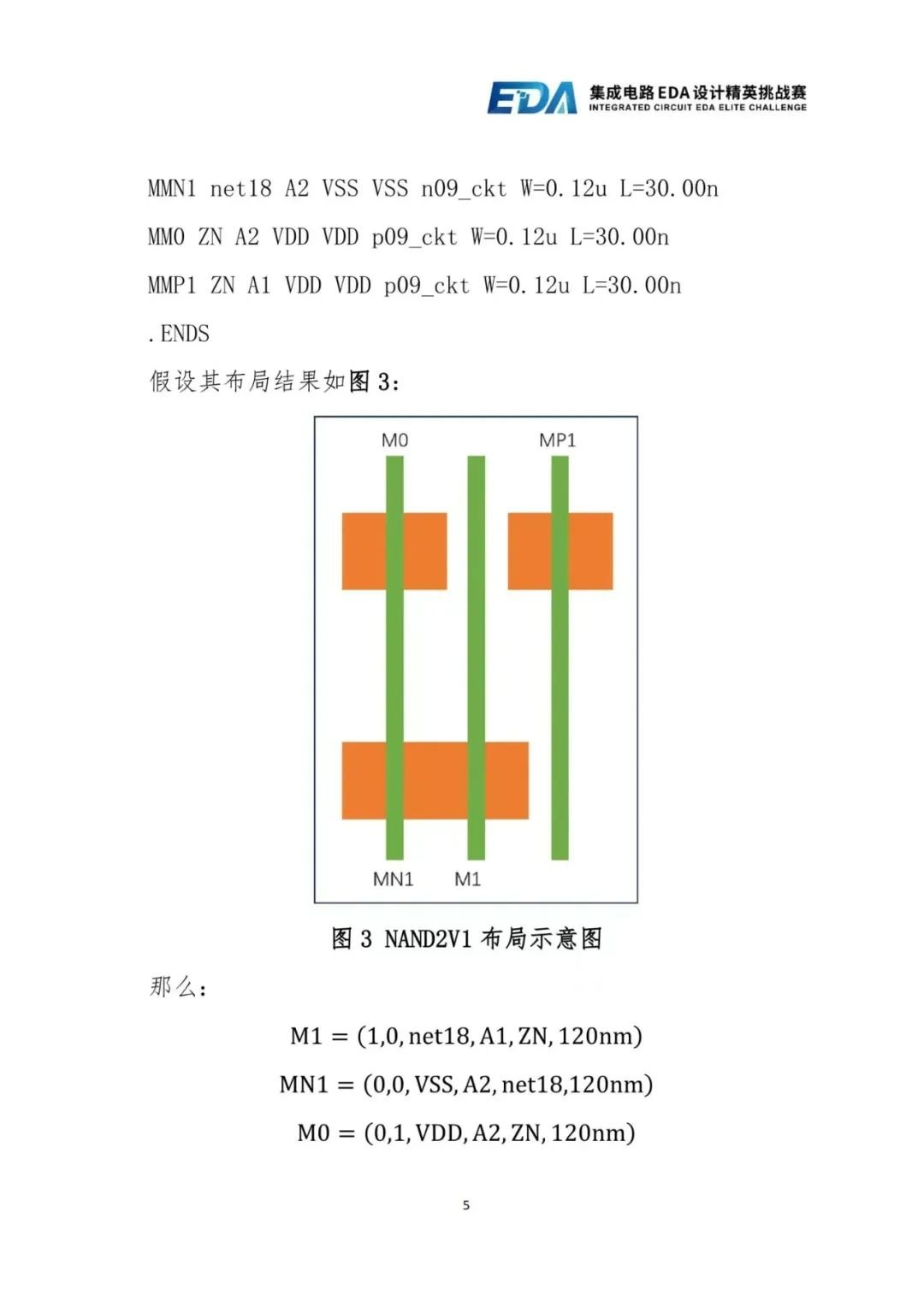

在标准单元的内部,晶体管按两行依次放置,PMOS晶体管在上面一行,NMOS 晶体管放在下面一行,本题中所有晶体管的有源区向电源轨道对齐,如图 2,详细描述见赛题描述。

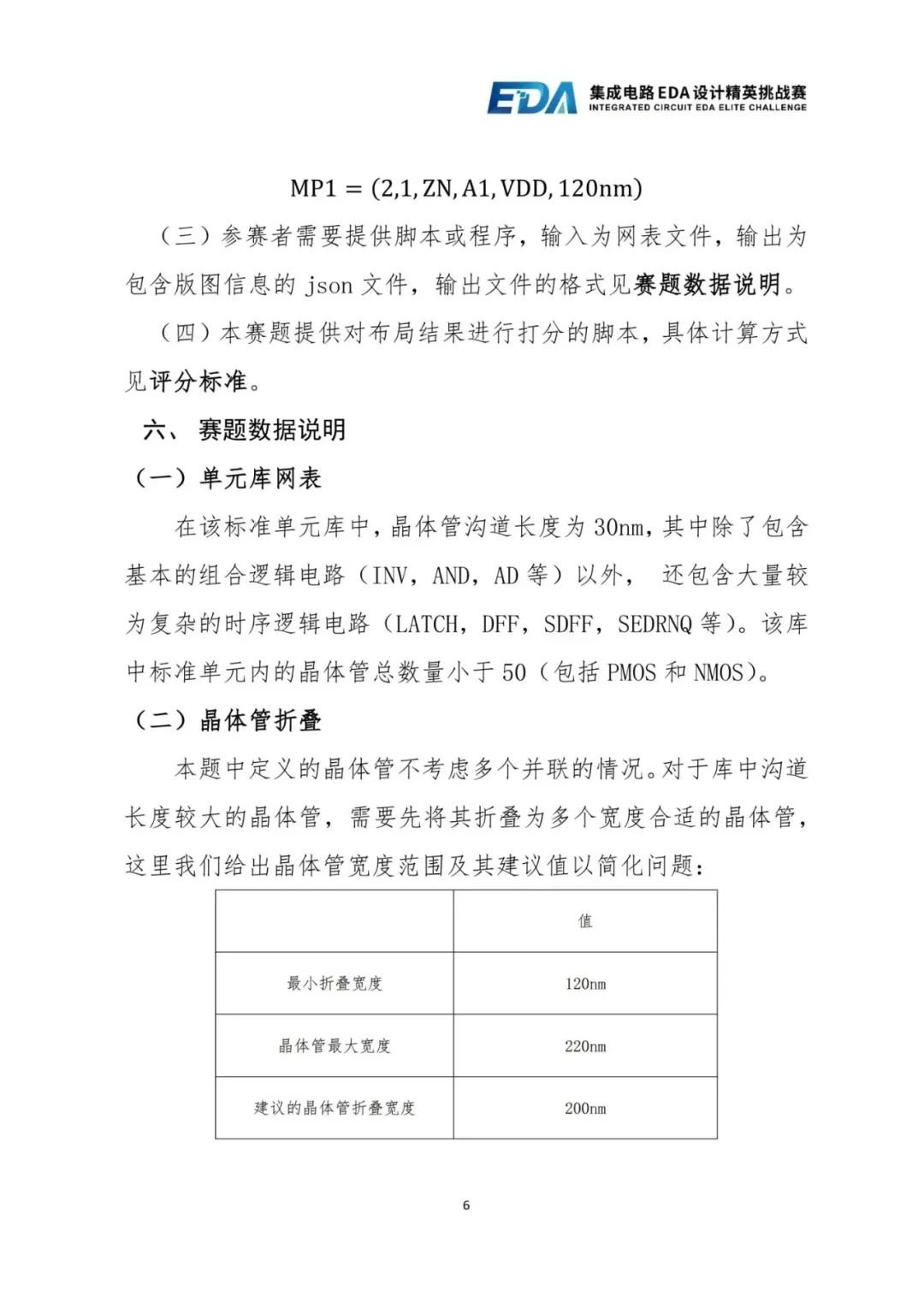

注:1. 晶体管由两个矩形表示,垂直矩形为栅极,蓝色矩形为有源区。2. 图中上下两侧的绿色矩形为电源轨道,分别连接VDD 和VSS。3. 整个标准单元被等分为两个部分,上半部分为PMOS 晶体管可放置的区域,下半部分为 NMOS 晶体管可放置的区域。4. 所有晶体管有源区向两侧的电源轨道对齐。5. 同一水平位置的晶体管栅极会直接相连。6. 若两个晶体管的有源区重叠,则其栅极间距为1个单位长度,此时要求重叠部分所连线网相同;若不重叠,则其栅极间距至少为2个单位长度。7. 本题中任意两个晶体管的栅极间距都为整数个单位长度。

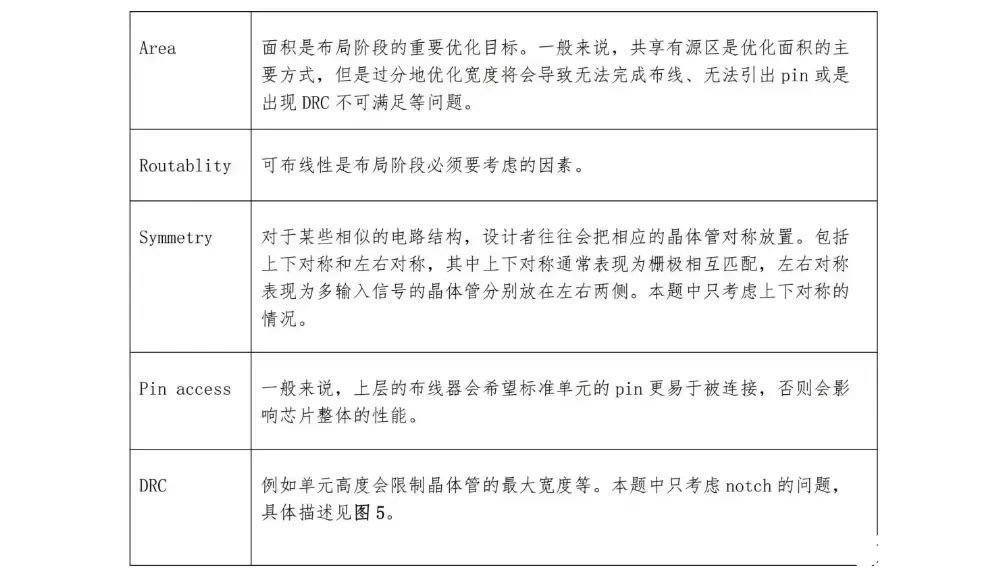

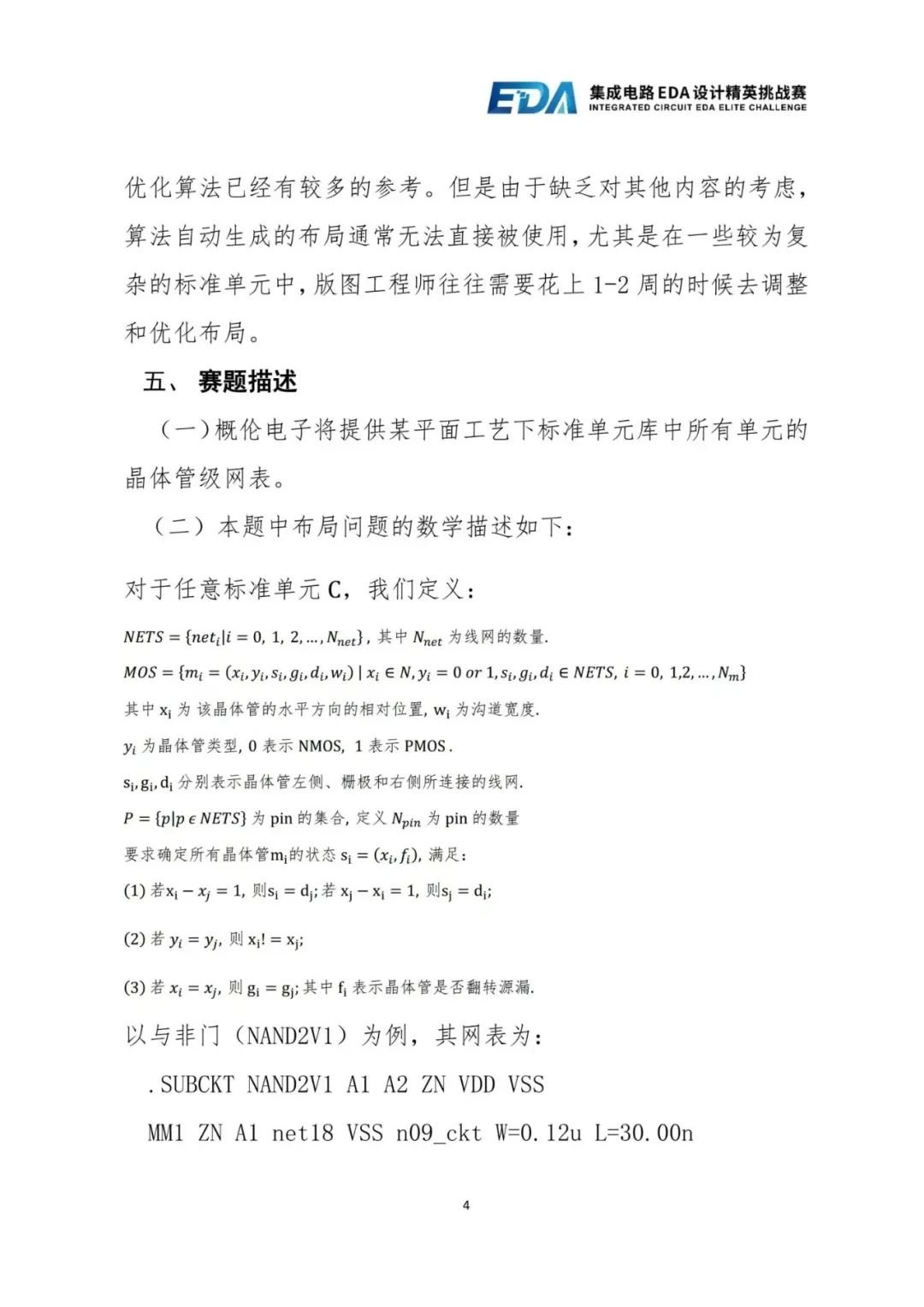

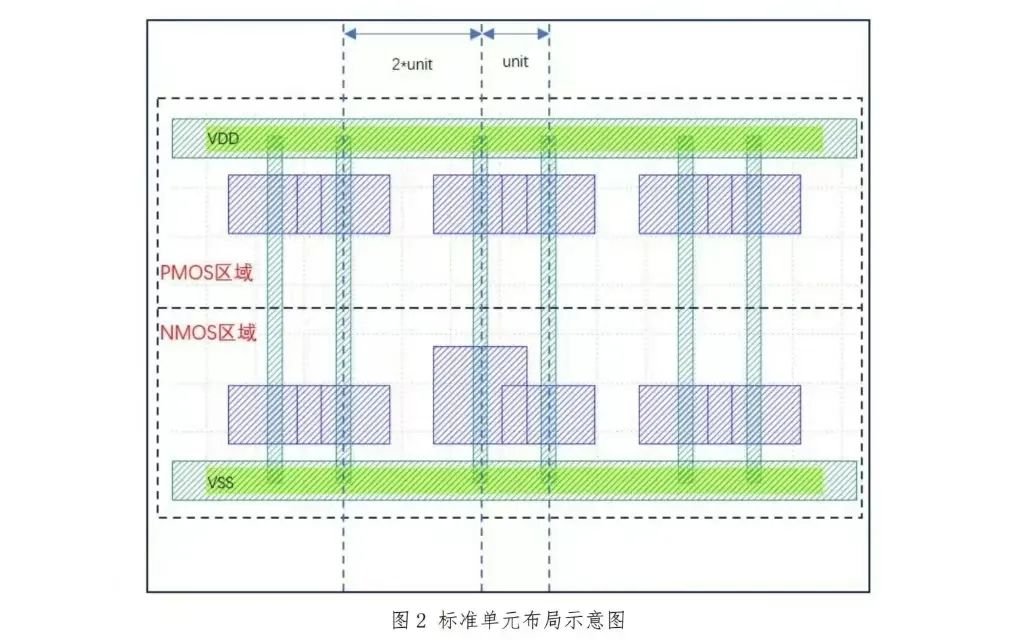

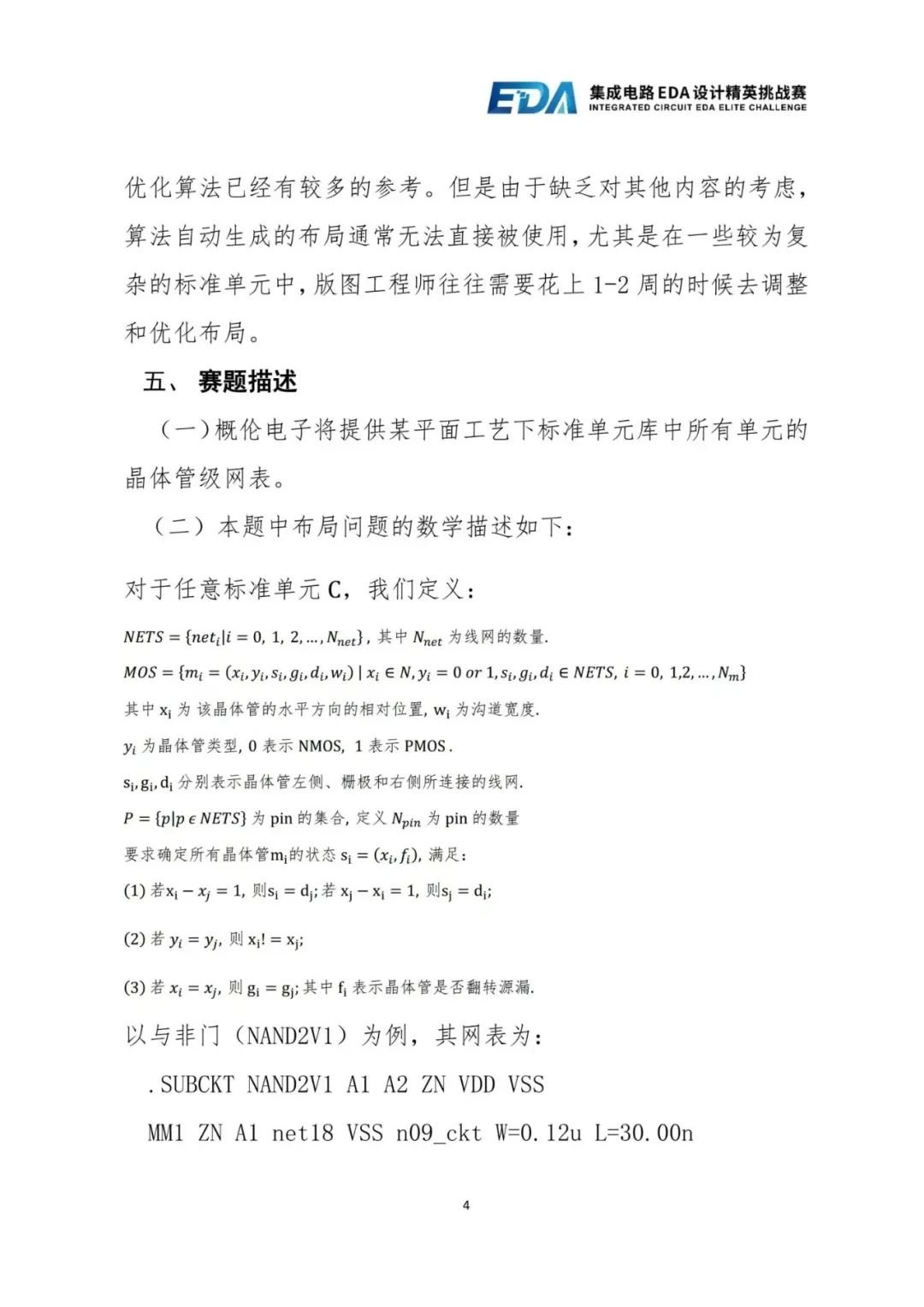

在进行晶体管布局时,版图工程师通常需要考虑以下这些内容:

在现有的标准单元布局算法的研究中,对面积和可布线性的优化算法已经有较多的参考。但是由于缺乏对其他内容的考虑,算法自动生成的布局通常无法直接被使用,尤其是在一些较为复杂的标准单元中,版图工程师往往需要花上 1-2 周的时候去调整和优化布局。

赛题Chair介绍

叶佐昌

清华大学

博士,毕业于清华大学微电子研究所。曾在美国Cadence伯克利实验室担任研究员,目前为清华大学集成电路学院副研究员,研究领域包括集成电路仿真、建模和自动化设计方法学。目前研究方向主要用于模拟全流程敏捷设计的EDA工具开发。

博士,毕业于清华大学微电子研究所。曾在美国Cadence伯克利实验室担任研究员,目前为清华大学集成电路学院副研究员,研究领域包括集成电路仿真、建模和自动化设计方法学。目前研究方向主要用于模拟全流程敏捷设计的EDA工具开发。

赛题描述

向左滑动查看更多内容>>

大赛概况

2023 (第五届)集成电路EDA设计精英挑战赛赛程时间安排如下:

EDA设计精英挑战赛现已正式开放报名,关注官网(http://eda.icisc.cn),获取更多大赛信息。

奖项设置

麒麟杯(1支):20万菁英杯(1-2支):8万一等奖(最高15%):2万二等奖(最高30%):1万

关于概伦

上海概伦电子股份有限公司(688206.SH)作为国内首家EDA上市公司,是关键核心技术具备国际市场竞争力的EDA领军企业,致力于打造应用驱动的、覆盖集成电路设计与制造的EDA全流程解决方案,支撑各类高端芯片研发的持续发展,并联合产业链上下游和EDA合作伙伴,建设有竞争力和生命力的EDA生态。通过EDA方法学创新,概伦电子推动集成电路设计和制造的深度联动,加快工艺开发和芯片设计进程,提高集成电路产品的良率和性能,增强了集成电路企业整体市场竞争力。

扫描二维码

扫描二维码

加入EDA设计精英挑战赛交流群

了解活动详情

原文标题:火热开赛,第五届集成电路EDA设计精英挑战赛概伦电子赛题发布

文章出处:【微信公众号:概伦电子Primarius】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:火热开赛,第五届集成电路EDA设计精英挑战赛概伦电子赛题发布

文章出处:【微信号:khai-long_tech,微信公众号:概伦电子Primarius】欢迎添加关注!文章转载请注明出处。

相关推荐

日前,2024中国研究生创“芯”大赛·EDA精英挑战赛(以下简称EDA竞赛)决赛在南京江北新区举办。今年EDA竞赛首次升级为国

![的头像]() 发表于

发表于 12-17 15:47

•233次阅读

12月13日, “2024第五届鸾鹭精英董秘论坛暨颁奖典礼”在贵州遵义隆重举行。本次活动由上海报业集团指导,财联社主办,百余家上市公司董秘、券商分析师及公司高管出席。会上发布了“第五届

![的头像]() 发表于

发表于 12-16 16:31

•257次阅读

12月11日-12日,上海集成电路2024年度产业发展论坛暨第三十届集成电路设计业展览会(ICCAD-Expo)圆满落幕。作为国内首家EDA上市公司、关键核心技术具备国际市场竞争力的

![的头像]() 发表于

发表于 12-13 15:45

•267次阅读

近日,“2024中国研究生创“芯”大赛·EDA精英挑战赛” 总决赛在南京完美收官,最终评审结果荣耀揭晓。广立微荣幸受邀成为本次大赛的命题合作企业,通过精心设计的命题、专业的指导以及参与高端论坛的演讲,为大赛的顺利进行增添了浓墨重

![的头像]() 发表于

发表于 12-13 14:08

•235次阅读

12月11日,上海EDA/IP创新中心授牌仪式在上海集成电路2024年度产业发展论坛暨第三十届集成电路设计业展览会(ICCAD-Expo 2024)上举行。上海市政府副秘书长、浦东新区

![的头像]() 发表于

发表于 12-11 17:18

•397次阅读

2024中国研究生创芯大赛·EDA精英挑战赛12月7-8日,2024中国研究生创芯大赛·EDA精英挑战赛

![的头像]() 发表于

发表于 12-11 01:03

•332次阅读

11月23日至24日,“奔跑贵州”山地跑系列赛暨第二届贵州织金洞精英穿越挑战赛盛大开赛。织金洞作为“世界地质公园”“国家5A级旅游景区”“中

![的头像]() 发表于

发表于 11-28 01:00

•156次阅读

11月7日,第五届毕马威中国“芯科技”新锐企业50评选榜单发布暨颁奖典礼在国家会展中心(上海)毕马威展台举行。本次活动聚集了业内专家及企业精英,共同探讨芯片技术的最前沿趋势,以及行业发展的新机遇与

![的头像]() 发表于

发表于 11-07 17:34

•611次阅读

近日,第五届毕马威中国“芯科技”新锐企业50评选榜单发布暨颁奖典礼在国家会展中心(上海)毕马威展台举行。

![的头像]() 发表于

发表于 11-07 15:44

•451次阅读

第二届OpenHarmony创新应用挑战赛作为开放原子大赛旗下的重要赛项,聚焦 OpenHarmony应用开发,致力提升开发者的动手实践能力与开发创新应用的能力。

赛项要求开发者

发表于 10-24 15:40

经过数月角逐,第二届AI4Science黑客松竞赛日前落下帷幕。在曦智科技主持的光子计算挑战赛中,参赛选手何自强和来自东北大学的参赛队伍The Power of Light获得完赛优胜奖。

![的头像]() 发表于

发表于 08-07 09:58

•520次阅读

赛题发布COMPETITIONRELEASE2024中国研究生创芯大赛·EDA精英挑战赛(原“

![的头像]() 发表于

发表于 08-03 08:24

•666次阅读

竞争力的EDA领军企业,概伦电子已连续14年参加DAC,今年更是现场展示了其快速精准的器件建模、单元库特征化和电路仿真解决方案。

![的头像]() 发表于

发表于 06-27 14:52

•651次阅读

赛微电子回应称,此番收购仅限于国家集成电路基金持有赛微电子之全资子公司赛莱克斯北京的少数股权,与

![的头像]() 发表于

发表于 05-13 09:47

•908次阅读

12月28日,第二十六届中国机器人及人工智能大赛人形机器人创新挑战赛在苏州正式发布,首次结合

![的头像]() 发表于

发表于 12-30 08:32

•1106次阅读

博士,毕业于清华大学微电子研究所。曾在美国Cadence伯克利实验室担任研究员,目前为清华大学集成电路学院副研究员,研究领域包括集成电路仿真、建模和自动化设计方法学。目前研究方向主要用于模拟全流程敏捷设计的EDA工具开发。

博士,毕业于清华大学微电子研究所。曾在美国Cadence伯克利实验室担任研究员,目前为清华大学集成电路学院副研究员,研究领域包括集成电路仿真、建模和自动化设计方法学。目前研究方向主要用于模拟全流程敏捷设计的EDA工具开发。

扫描二维码

扫描二维码

火热开赛,第五届集成电路EDA设计精英挑战赛概伦电子赛题发布

火热开赛,第五届集成电路EDA设计精英挑战赛概伦电子赛题发布

评论